Комплементарный металл -оксид-полупроводник ( КМОП , произносится как «морской мох», / s iːmɑːs / , / -ɒs / ) — это тип процесса изготовления полевых транзисторов на основе металла-оксида-полупроводника ( МОП-транзисторов) , в котором для выполнения логических функций используются комплементарные и симметричные пары МОП-транзисторов p-типа и n-типа . [1] Технология КМОП используется для создания интегральных схем (ИС), включая микропроцессоры , микроконтроллеры , микросхемы памяти (включая КМОП-BIOS ) и другие цифровые логические схемы. Технология КМОП также используется для аналоговых схем, таких как датчики изображения ( КМОП-датчики ), преобразователи данных , радиочастотные схемы ( РЧ-КМОП ) и высокоинтегрированные приемопередатчики для многих типов связи.

В 1948 году Бардин и Браттейн запатентовали транзистор с изолированным затвором (IGFET) с инверсионным слоем. Концепция Бардина составляет основу технологии КМОП сегодня. Процесс КМОП был представлен Фрэнком Уонлассом и Чи-Тан Са из Fairchild Semiconductor на Международной конференции по твердотельным схемам в 1963 году. Позднее Уонласс подал заявку на патент США 3 356 858 на схему КМОП, и он был выдан в 1967 году. RCA коммерциализировала технологию под торговой маркой «COS-MOS» в конце 1960-х годов, заставив других производителей найти другое название, в результате чего «КМОП» стало стандартным названием для технологии к началу 1970-х годов. КМОП обогнал NMOS логику как доминирующий процесс изготовления MOSFET для чипов сверхбольшой интеграции (VLSI) в 1980-х годах, также заменив более раннюю технологию транзисторно-транзисторной логики (TTL). С тех пор КМОП остается стандартным процессом изготовления полупроводниковых устройств MOSFET в чипах VLSI. По состоянию на 2011 год 99% чипов ИС, включая большинство цифровых , аналоговых и смешанных сигналов ИС, были изготовлены с использованием технологии КМОП. [2][обновлять]

Две важные характеристики устройств CMOS — высокая помехоустойчивость и низкое статическое энергопотребление . [3] Поскольку один транзистор пары MOSFET всегда выключен, последовательная комбинация потребляет значительную мощность только на мгновение во время переключения между включенным и выключенным состояниями. Следовательно, устройства CMOS не производят столько отработанного тепла , как другие формы логики, такие как логика NMOS или транзисторно-транзисторная логика (TTL), которые обычно имеют некоторый постоянный ток, даже когда не меняют состояние. Эти характеристики позволяют CMOS интегрировать высокую плотность логических функций на кристалле. Именно по этой причине CMOS стала наиболее широко используемой технологией для внедрения в кристаллы VLSI.

Фраза «металл–оксид–полупроводник» относится к физической структуре полевых МОП-транзисторов , имеющих металлический затворный электрод, размещенный поверх оксидного изолятора, который, в свою очередь, находится поверх полупроводникового материала . Когда-то использовался алюминий , но теперь материалом является поликремний . Другие металлические затворы вернулись с появлением диэлектрических материалов с высокой проводимостью в процессе КМОП, как было объявлено IBM и Intel для узла 45 нанометров и меньших размеров. [4]

Принцип дополнительной симметрии был впервые введен Джорджем Шиклаем в 1953 году, который затем обсудил несколько дополнительных биполярных схем. Пол Ваймер , также работавший в RCA , в 1962 году изобрел дополнительные схемы на тонкопленочных транзисторах (TFT), близкие родственники КМОП. Он изобрел дополнительные схемы триггеров и инверторов, но не работал над более сложной дополнительной логикой. Он был первым человеком, который смог поместить p-канальные и n-канальные TFT в схему на одной подложке. Тремя годами ранее Джон Т. Уоллмарк и Сэнфорд М. Маркус опубликовали множество сложных логических функций, реализованных в виде интегральных схем с использованием JFET , включая дополнительные схемы памяти. Фрэнк Ванласс был знаком с работой Ваймера в RCA. [6] [7] [8] [9] [10] [11]

В 1955 году Карл Фрош и Линкольн Дерик случайно вырастили слой диоксида кремния поверх кремниевой пластины, для которого они наблюдали эффекты пассивации поверхности. [12] К 1957 году Фрош и Деррик, используя маскирование и предварительное осаждение, смогли изготовить транзисторы из диоксида кремния и показали, что диоксид кремния изолирует, защищает кремниевые пластины и предотвращает диффузию легирующих примесей в пластину. [12] [13] Дж. Р. Лигенца и В. Г. Шпитцер изучили механизм термически выращенных оксидов и изготовили высококачественный стек Si/ SiO 2 в 1960 году. [14] [15] [16]

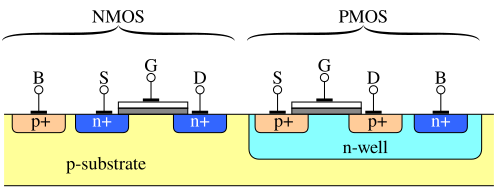

После этого исследования Мохамед Аталла и Давон Канг предложили кремниевый МОП-транзистор в 1959 году [17] и успешно продемонстрировали работающее МОП-устройство со своей командой из Bell Labs в 1960 году. [18] [19] В их команду входили EE LaBate и EI Povilonis, которые изготовили устройство; MO Thurston, LA D'Asaro и JR Ligenza, которые разработали процессы диффузии, а также HK Gummel и R. Lindner, которые охарактеризовали устройство. [20] [21] Первоначально существовало два типа логики МОП-транзистора: PMOS ( МОП p-типа ) и NMOS ( МОП n-типа ). [22] Оба типа были разработаны Фрошем и Дерриком в 1957 году в Bell Labs. [23]

В 1948 году Бардин и Браттейн запатентовали предшественника МОП-транзистора, полевой транзистор с изолированным затвором (IGFET) с инверсионным слоем. Патент Бардина и концепция инверсионного слоя сегодня составляют основу технологии КМОП. [24] Новый тип логики МОП-транзистора, объединяющий процессы PMOS и NMOS, был разработан Чи-Тангом Са и Фрэнком Ванлассом из Fairchild, названный комплементарным МОП (КМОП). В феврале 1963 года они опубликовали изобретение в исследовательской статье . [25] [26] И в исследовательской статье, и в патенте , поданном Ванлассом, было описано изготовление устройств КМОП на основе термического окисления кремниевой подложки для получения слоя диоксида кремния, расположенного между стоковым контактом и истоковым контактом. [27] [26]

Технология CMOS была коммерциализирована компанией RCA в конце 1960-х годов. RCA приняла технологию CMOS для проектирования интегральных схем (ИС), разработав схемы CMOS для компьютера ВВС в 1965 году, а затем 288- битную микросхему памяти CMOS SRAM в 1968 году. [25] RCA также использовала технологию CMOS для своих интегральных схем серии 4000 в 1968 году, начав с 20- мкм процесса производства полупроводников , а затем постепенно масштабируясь до 10-мкм процесса в течение следующих нескольких лет. [28]

Технология CMOS изначально была проигнорирована американской полупроводниковой промышленностью в пользу NMOS, которая была более мощной в то время. Однако CMOS была быстро принята и далее развита японскими производителями полупроводников из-за ее низкого энергопотребления, что привело к росту японской полупроводниковой промышленности. [29] В 1969 году Toshiba разработала C 2 MOS (Clocked CMOS), технологию схем с более низким энергопотреблением и более высокой скоростью работы, чем у обычных CMOS. Toshiba использовала свою технологию C 2 MOS для разработки микросхемы с большой интеграцией (LSI) для карманного светодиодного калькулятора Elsi Mini компании Sharp , разработанного в 1971 году и выпущенного в 1972 году. [30] Suwa Seikosha (теперь Seiko Epson ) начала разработку микросхемы CMOS IC для кварцевых часов Seiko в 1969 году и начала массовое производство с выпуском часов Seiko Analog Quartz 38SQW в 1971 году. [31] Первым массовым потребительским электронным продуктом CMOS стали цифровые часы Hamilton Pulsar «Wrist Computer», выпущенные в 1970 году. [32] Благодаря низкому энергопотреблению логика CMOS широко используется для калькуляторов и часов с 1970-х годов. [33]

Самые ранние микропроцессоры в начале 1970-х годов были процессорами PMOS, которые изначально доминировали в ранней микропроцессорной индустрии. К концу 1970-х годов микропроцессоры NMOS обогнали процессоры PMOS. [34] Микропроцессоры CMOS были представлены в 1975 году с Intersil 6100 , [34] и RCA CDP 1801. [ 35] Однако процессоры CMOS не стали доминирующими до 1980-х годов. [34]

Первоначально КМОП-логика была медленнее, чем логика NMOS , поэтому NMOS более широко использовалась для компьютеров в 1970-х годах. [33] Чип памяти CMOS Intel 5101 (1 кб SRAM ) (1974) имел время доступа 800 нс , [36] [37] тогда как самый быстрый чип NMOS в то время, чип памяти HMOS Intel 2147 (4 кб SRAM) (1976), имел время доступа 55/70 нс. [33] [37] В 1978 году исследовательская группа Hitachi под руководством Тошиаки Масухары представила двухъярусный процесс Hi-CMOS с чипом памяти HM6147 (4 кб SRAM), изготовленным по 3 мкм процессу . [33] [38] [39] Чип Hitachi HM6147 смог сравниться по производительности ( доступ 55/70 нс) с чипом Intel 2147 HMOS, в то время как HM6147 также потреблял значительно меньше энергии (15 мА ), чем 2147 (110 мА). При сопоставимой производительности и гораздо меньшем потреблении энергии двухъядерный CMOS-процесс в конечном итоге обогнал NMOS как наиболее распространенный процесс производства полупроводников для компьютеров в 1980-х годах. [33]

В 1980-х годах КМОП-микропроцессоры вытеснили НМОП-микропроцессоры. [34] Космический аппарат НАСА « Галилео» , отправленный на орбиту Юпитера в 1989 году, использовал КМОП-микропроцессор RCA 1802 из-за низкого энергопотребления. [32]

Intel представила 1,5 мкм процесс для изготовления полупроводниковых устройств КМОП в 1983 году. [40] В середине 1980-х годов Биджан Давари из IBM разработал высокопроизводительную, низковольтную, глубокую субмикронную технологию КМОП, которая позволила разрабатывать более быстрые компьютеры, а также портативные компьютеры и портативную электронику с питанием от батарей . [41] В 1988 году Давари возглавил команду IBM, которая продемонстрировала высокопроизводительный 250-нанометровый процесс КМОП. [42]

Fujitsu коммерциализировала 700 нм КМОП-процесс в 1987 году, [40] а затем Hitachi, Mitsubishi Electric , NEC и Toshiba коммерциализировали 500 нм КМОП-процесс в 1989 году. [43] В 1993 году Sony коммерциализировала 350 нм КМОП-процесс, в то время как Hitachi и NEC коммерциализировали 250 нм КМОП. Hitachi представила 160 нм КМОП-процесс в 1995 году, затем Mitsubishi представила 150 нм КМОП в 1996 году, а затем Samsung Electronics представила 140 нм в 1999 году. [43]

В 2000 году Гуртедж Сингх Сандху и Трунг Т. Доан из Micron Technology изобрели атомно-слоевое осаждение диэлектрических пленок High-κ , что привело к разработке экономически эффективного 90-нм КМОП-процесса. [41] [44] Toshiba и Sony разработали 65-нм КМОП-процесс в 2002 году, [45] а затем TSMC инициировала разработку 45-нм КМОП-логики в 2004 году. [46] Разработка Гуртеджем Сингхом Сандху из Micron Technology двойного шаблона привела к разработке 30 -нм класса КМОП в 2000-х годах. [41]

КМОП используется в большинстве современных устройств LSI и VLSI . [33] По состоянию на 2010 год, процессоры с лучшей производительностью на ватт каждый год были на основе статической логики КМОП с 1976 года. [ необходима ссылка ] По состоянию на 2019 год планарная технология КМОП по-прежнему является наиболее распространенной формой изготовления полупроводниковых устройств, но постепенно заменяется непланарной технологией FinFET , которая позволяет изготавливать полупроводниковые узлы размером менее 20 нм . [47]

«КМОП» относится как к определенному стилю проектирования цифровых схем, так и к семейству процессов, используемых для реализации этих схем на интегральных схемах (чипах). Схемы КМОП рассеивают меньше мощности , чем логические семейства с резистивными нагрузками. Поскольку это преимущество возросло и стало более важным, процессы и варианты КМОП стали доминировать, поэтому подавляющее большинство современных интегральных схем производится на основе процессов КМОП. [48] Логика КМОП потребляет около одной седьмой мощности логики NMOS , [33] и примерно в 10 миллионов раз меньше мощности, чем биполярная транзисторно-транзисторная логика (ТТЛ). [49] [50]

Схемы КМОП используют комбинацию полевых транзисторов металл-оксид-полупроводник p-типа и n-типа (МОП-транзисторы) для реализации логических вентилей и других цифровых схем. Хотя логика КМОП может быть реализована с помощью дискретных устройств для демонстраций, коммерческие продукты КМОП представляют собой интегральные схемы, состоящие из миллиардов транзисторов обоих типов на прямоугольном куске кремния часто от 10 до 400 мм 2 . [ необходима цитата ]

КМОП всегда использует все МОП-транзисторы в режиме улучшения (другими словами, нулевое напряжение затвор-исток выключает транзистор). [51]

Схемы CMOS построены таким образом, что все транзисторы металл-оксид-полупроводник (PMOS) P-типа должны иметь либо вход от источника напряжения, либо от другого транзистора PMOS. Аналогично, все транзисторы NMOS должны иметь либо вход от земли, либо от другого транзистора NMOS. Состав транзистора PMOS создает низкое сопротивление между его контактами истока и стока при приложении низкого напряжения затвора и высокое сопротивление при приложении высокого напряжения затвора. С другой стороны, состав транзистора NMOS создает высокое сопротивление между истоком и стоком при приложении низкого напряжения затвора и низкое сопротивление при приложении высокого напряжения затвора. CMOS обеспечивает снижение тока, дополняя каждый nMOSFET pMOSFET и соединяя оба затвора и оба стока вместе. Высокое напряжение на затворах заставит nMOSFET проводить, а pMOSFET не проводить, в то время как низкое напряжение на затворах вызывает обратное. Такое расположение значительно снижает потребление энергии и выделение тепла. Однако во время переключения как pMOS, так и nMOS MOSFET кратковременно проводят ток, когда напряжение затвора переходит из одного состояния в другое. Это вызывает кратковременный всплеск потребления энергии и становится серьезной проблемой на высоких частотах.

На соседнем изображении показано, что происходит, когда вход подключен как к PMOS-транзистору (вверху диаграммы), так и к NMOS-транзистору (внизу диаграммы). Vdd — это некоторое положительное напряжение, подключенное к источнику питания, а Vss — это земля. A — это вход, а Q — это выход.

Когда напряжение A низкое (т.е. близко к Vss), канал NMOS-транзистора находится в состоянии высокого сопротивления, отключая Vss от Q. Канал PMOS-транзистора находится в состоянии низкого сопротивления, подключая Vdd к Q. Таким образом, Q регистрирует Vdd.

С другой стороны, когда напряжение A высокое (т.е. близко к Vdd), PMOS-транзистор находится в состоянии высокого сопротивления, отключая Vdd от Q. NMOS-транзистор находится в состоянии низкого сопротивления, подключая Vss к Q. Теперь Q регистрирует Vss.

Короче говоря, выходы транзисторов PMOS и NMOS являются комплементарными, так что когда вход низкий, выход высокий, а когда вход высокий, выход низкий. Независимо от того, какой вход, выход никогда не остается плавающим (заряд никогда не сохраняется из-за емкости проводов и отсутствия электрического стока/земли). Из-за такого поведения входа и выхода выход схемы CMOS является инверсией входа.

Сопротивления транзисторов никогда не равны нулю или бесконечности, поэтому Q никогда не будет точно равен Vss или Vdd, но Q всегда будет ближе к Vss, чем A был к Vdd (или наоборот, если бы A был близок к Vss). Без этого усиления был бы очень низкий предел количества логических вентилей, которые могли бы быть соединены последовательно, и КМОП-логика с миллиардами транзисторов была бы невозможна.

Контакты питания для КМОП называются V DD и V SS или V CC и Ground(GND) в зависимости от производителя. V DD и V SS являются переносами из обычных схем МОП и обозначают сток и исток . [52] Они не применяются напрямую к КМОП, поскольку оба источника на самом деле являются источниками. V CC и Ground являются переносами из логики ТТЛ , и эта номенклатура была сохранена с введением линейки КМОП 54C/74C.

Важной характеристикой схемы CMOS является дуальность, которая существует между ее транзисторами PMOS и транзисторами NMOS. Схема CMOS создается для того, чтобы всегда существовал путь от выхода либо к источнику питания, либо к земле. Чтобы достичь этого, набор всех путей к источнику напряжения должен быть дополнением набора всех путей к земле. Этого можно легко достичь, определив один в терминах НЕ другого. Благодаря логике, основанной на законах Де Моргана , транзисторы PMOS, включенные параллельно, имеют соответствующие транзисторы NMOS, включенные последовательно, в то время как транзисторы PMOS, включенные последовательно, имеют соответствующие транзисторы NMOS, включенные параллельно.

Более сложные логические функции, такие как те, которые включают вентили И и ИЛИ, требуют манипулирования путями между вентилями для представления логики. Когда путь состоит из двух транзисторов последовательно, оба транзистора должны иметь низкое сопротивление соответствующему напряжению питания, моделируя И. Когда путь состоит из двух транзисторов параллельно, один или оба транзистора должны иметь низкое сопротивление для подключения напряжения питания к выходу, моделируя ИЛИ.

Справа показана принципиальная схема вентиля NAND в логике CMOS. Если оба входа A и B имеют высокий уровень, то оба NMOS-транзистора (нижняя половина схемы) будут проводить ток, ни один из PMOS-транзисторов (верхняя половина) не будет проводить ток, и между выходом и V ss (землей) будет установлен проводящий путь, что приведет к низкому уровню выхода. Если оба входа A и B имеют низкий уровень, то ни один из NMOS-транзисторов не будет проводить ток, в то время как оба PMOS-транзистора будут проводить ток, устанавливая проводящий путь между выходом и V dd (источником напряжения), что приведет к высокому уровню выхода. Если любой из входов A или B имеет низкий уровень, один из NMOS-транзисторов не будет проводить ток, один из PMOS-транзисторов будет проводить ток, и между выходом и V dd (источником напряжения) будет установлен проводящий путь, что приведет к высокому уровню выхода. Поскольку единственная конфигурация двух входов, которая приводит к низкому уровню на выходе, — это когда оба входа имеют высокий уровень, эта схема реализует логический элемент NAND (НЕ И).

Преимущество CMOS по сравнению с NMOS-логикой заключается в том, что как низко-высокие, так и высоко-низкие выходные переходы происходят быстро, поскольку транзисторы подтяжки (PMOS) имеют низкое сопротивление при включении, в отличие от нагрузочных резисторов в NMOS-логике. Кроме того, выходной сигнал качает полное напряжение между низким и высоким уровнями. Этот сильный, более симметричный отклик также делает CMOS более устойчивым к шуму.

Метод расчета задержки в схеме КМОП см. в разделе Логические усилия .

В этом примере показано логическое устройство NAND , нарисованное в виде физического представления, как оно будет изготовлено. Физическая компоновка представляет собой «вид с высоты птичьего полета» на стопку слоев. Схема построена на подложке P-типа . Поликремниевый , диффузионный и n-well слои называются «базовыми слоями» и фактически вставлены в канавки подложки P-типа. (См. шаги с 1 по 6 на схеме процесса внизу справа) Контакты проникают в изолирующий слой между базовыми слоями и первым слоем металла (metal1), создавая соединение.

Входы в NAND (показаны зеленым цветом) находятся в поликремнии. Транзисторы (устройства) образованы пересечением поликремния и диффузии; N-диффузия для N-устройства и P-диффузия для P-устройства (показаны лососевым и желтым цветом соответственно). Выход («out») соединен вместе в металле (показаны голубым цветом). Соединения между металлом и поликремнием или диффузией осуществляются через контакты (показаны черными квадратами). Пример физической компоновки соответствует логической схеме NAND, приведенной в предыдущем примере.

Устройство N изготавливается на подложке типа P, тогда как устройство P изготавливается в яме типа N (n-well). «Отвод» подложки типа P подключается к V SS , а отвод n-well типа N подключается к V DD для предотвращения защелкивания .

Логика CMOS рассеивает меньше мощности, чем логические схемы NMOS, потому что CMOS рассеивает мощность только при переключении («динамическая мощность»). На типичной ASIC в современном 90-нанометровом процессе переключение выхода может занять 120 пикосекунд и происходит раз в десять наносекунд. Логика NMOS рассеивает мощность всякий раз, когда транзистор включен, потому что существует путь тока от V dd до V ss через нагрузочный резистор и сеть n-типа.

Статические КМОП-затворы очень энергоэффективны, поскольку они рассеивают почти нулевую мощность в режиме ожидания. Раньше энергопотребление КМОП-устройств не было главной проблемой при проектировании чипов. Такие факторы, как скорость и площадь, доминировали в параметрах проектирования. По мере того, как технология КМОП опускалась ниже субмикронных уровней, энергопотребление на единицу площади чипа значительно возросло.

В широком смысле рассеивание мощности в КМОП-схемах происходит из-за двух компонентов: статического и динамического:

Оба транзистора NMOS и PMOS имеют пороговое напряжение затвор-исток (V th ), ниже которого ток (называемый субпороговым током) через устройство будет падать экспоненциально. Исторически схемы CMOS работали при напряжениях питания, намного превышающих их пороговые напряжения (V dd могло быть 5 В, а V th как для NMOS, так и для PMOS могло быть 700 мВ). Особым типом транзистора, используемого в некоторых схемах CMOS, является собственный транзистор с пороговым напряжением , близким к нулю .

SiO 2 является хорошим изолятором, но при очень малых толщинах электроны могут туннелировать через очень тонкую изоляцию; вероятность падает экспоненциально с толщиной оксида. Туннельный ток становится очень важным для транзисторов ниже 130 нм технологии с затворными оксидами 20 Å или тоньше.

Небольшие обратные токи утечки образуются из-за образования обратного смещения между диффузионными областями и ямами (например, диффузия p-типа против n-ямы), ямами и подложкой (например, n-яма против p-подложки). В современных процессах утечка диода очень мала по сравнению с подпороговыми и туннельными токами, поэтому ими можно пренебречь при расчетах мощности.

Если соотношения не совпадают, то могут быть разные токи PMOS и NMOS; это может привести к дисбалансу, и, таким образом, неправильный ток заставляет CMOS нагреваться и рассеивать мощность без необходимости. Кроме того, недавние исследования показали, что мощность утечки уменьшается из-за эффектов старения в качестве компромисса для устройств, которые становятся медленнее. [53]

Для ускорения разработки производители перешли на конструкции с более низкими порогами напряжения, но из-за этого современный NMOS-транзистор с V th 200 мВ имеет значительный подпороговый ток утечки. Конструкции (например, настольные процессоры), которые включают в себя огромное количество схем, которые не переключаются активно, все равно потребляют мощность из-за этого тока утечки. Мощность утечки составляет значительную часть общей мощности, потребляемой такими конструкциями. Многопороговая КМОП (MTCMOS), теперь доступная в литейных цехах, является одним из подходов к управлению мощностью утечки. С MTCMOS транзисторы с высоким V th используются, когда скорость переключения не критична, в то время как транзисторы с низким V th используются в чувствительных к скорости путях. Дальнейшие технологические достижения, которые используют еще более тонкие диэлектрики затвора, имеют дополнительный компонент утечки из-за туннелирования тока через чрезвычайно тонкий диэлектрик затвора. Использование диэлектриков с высоким κ вместо диоксида кремния , который является обычным диэлектриком затвора, позволяет добиться аналогичной производительности устройства, но с более толстым изолятором затвора, что позволяет избежать этого тока. Снижение мощности утечки с использованием новых материалов и системных конструкций имеет решающее значение для поддержания масштабирования КМОП. [54]

Схемы КМОП рассеивают мощность, заряжая различные емкости нагрузки (в основном емкости затвора и проводов, но также сток и некоторые емкости источника) всякий раз, когда они переключаются. За один полный цикл логики КМОП ток течет от V DD к емкости нагрузки для ее зарядки, а затем течет от заряженной емкости нагрузки (C L ) к земле во время разряда. Таким образом, за один полный цикл заряда/разряда, в общей сложности Q=C L V DD передается от V DD к земле. Умножьте на частоту переключения на емкостях нагрузки, чтобы получить используемый ток, и снова умножьте на среднее напряжение, чтобы получить характерную мощность переключения, рассеиваемую устройством КМОП: .

Поскольку большинство вентилей не работают/переключаются в каждом такте , они часто сопровождаются фактором , называемым фактором активности. Теперь динамическое рассеивание мощности можно переписать как .

Часы в системе имеют фактор активности α=1, поскольку они поднимаются и опускаются каждый цикл. Большинство данных имеют фактор активности 0,1. [55] Если правильная емкость нагрузки оценивается на узле вместе с его фактором активности, динамическое рассеивание мощности на этом узле может быть эффективно рассчитано.

Поскольку существует конечное время нарастания/спада как для pMOS, так и для nMOS, во время перехода, например, из выключенного состояния во включенное, оба транзистора будут включены в течение небольшого периода времени, в течение которого ток найдет путь непосредственно от V DD к земле, тем самым создавая ток короткого замыкания , иногда называемый током короткого замыкания . Рассеиваемая мощность короткого замыкания увеличивается с увеличением времени нарастания и спада транзисторов.

Эта форма потребления энергии стала значимой в 1990-х годах, когда провода на чипе стали уже, а длинные провода — более резистивными. КМОП-затворы на конце этих резистивных проводов видят медленные входные переходы. Тщательная конструкция, которая избегает слабо управляемых длинных тонких проводов, уменьшает этот эффект, но мощность ломовой заглушки может быть существенной частью динамической мощности КМОП.

Паразитные транзисторы, присущие структуре КМОП, могут быть включены входными сигналами за пределами нормального рабочего диапазона, например, электростатическими разрядами или отражениями линий . Возникающее защелкивание может повредить или разрушить устройство КМОП. Для работы с этими сигналами в схемы КМОП включены фиксирующие диоды. В технических характеристиках производителей указан максимально допустимый ток, который может протекать через диоды.

Помимо цифровых приложений, технология CMOS также используется в аналоговых приложениях. Например, на рынке доступны операционные усилители CMOS IC. Передающие вентили могут использоваться как аналоговые мультиплексоры вместо сигнальных реле . Технология CMOS также широко используется для схем RF вплоть до микроволновых частот в приложениях со смешанным сигналом (аналоговый+цифровой). [ необходима цитата ]

RF CMOS относится к радиочастотным схемам ( радиочастотным схемам), которые основаны на технологии интегральных схем смешанного сигнала CMOS . Они широко используются в беспроводной телекоммуникационной технологии. RF CMOS была разработана Асадом Абиди во время работы в Калифорнийском университете в Лос-Анджелесе в конце 1980- х годов. Это изменило способ проектирования радиочастотных схем, что привело к замене дискретных биполярных транзисторов на интегральные схемы CMOS в радиотрансиверах . [56] Это позволило создать сложные, недорогие и портативные терминалы конечного пользователя и привело к появлению небольших, дешевых, маломощных и портативных устройств для широкого спектра беспроводных систем связи. Это позволило осуществлять связь «в любое время и в любом месте» и помогло осуществить беспроводную революцию , что привело к быстрому росту беспроводной индустрии. [57]

Процессоры основной полосы частот [58] [59] и радиопередатчики во всех современных беспроводных сетевых устройствах и мобильных телефонах производятся серийно с использованием устройств RF CMOS. [56] Схемы RF CMOS широко используются для передачи и приема беспроводных сигналов в различных приложениях, таких как спутниковые технологии (например, GPS ), Bluetooth , Wi-Fi , связь ближнего поля (NFC), мобильные сети (например, 3G и 4G ), наземное вещание и автомобильные радары , среди прочих применений. [60]

Примерами коммерческих RF CMOS-чипов являются беспроводной телефон Intel DECT и чипы 802.11 ( Wi-Fi ), созданные Atheros и другими компаниями. [61] Коммерческие RF CMOS-продукты также используются для сетей Bluetooth и беспроводных локальных сетей (WLAN). [62] RF CMOS также используется в радиопередатчиках для беспроводных стандартов, таких как GSM , Wi-Fi и Bluetooth, приемопередатчиках для мобильных сетей, таких как 3G, и удаленных устройствах в беспроводных сенсорных сетях (WSN). [63]

Технология RF CMOS имеет решающее значение для современных беспроводных коммуникаций, включая беспроводные сети и мобильные устройства связи. Одной из компаний, которая коммерциализировала технологию RF CMOS, была Infineon . Ее массовые коммутаторы CMOS RF продаются в количестве более 1 миллиарда единиц в год, достигнув совокупного показателя в 5 миллиардов единиц по состоянию на 2018 год [update]. [64]

Обычные КМОП-устройства работают в диапазоне температур от −55 °C до +125 °C.

Уже в августе 2008 года появились теоретические указания на то, что кремниевая КМОП-технология будет работать при температуре до −233 °C (40 K ). [65] С тех пор рабочие температуры около 40 K были достигнуты с использованием разогнанных процессоров AMD Phenom II с комбинацией охлаждения жидким азотом и жидким гелием . [66]

Устройства CMOS на основе карбида кремния испытывались в течение года при температуре 500 °C. [67] [68]

Сверхмалые (L = 20 нм, W = 20 нм) МОП-транзисторы достигают предела одного электрона при работе при криогенной температуре в диапазоне от −269 °C (4 K ) до примерно −258 °C (15 K ). Транзистор демонстрирует кулоновскую блокаду из-за прогрессирующей зарядки электронов по одному. Количество электронов, удерживаемых в канале, управляется напряжением затвора, начиная с занятия нулевых электронов, и может быть установлено равным одному или нескольким. [69]

Главное отличие — это мощность: КМОП-затворы могут потреблять примерно в 100 000 раз меньше энергии, чем их ТТЛ-эквиваленты!