Аппаратное ускорение — это использование компьютерного оборудования, разработанного для более эффективного выполнения определенных функций по сравнению с программным обеспечением, работающим на универсальном центральном процессоре (ЦП). Любое преобразование данных , которое может быть рассчитано в программном обеспечении, работающем на универсальном ЦП, может быть также рассчитано в изготовленном на заказ оборудовании или в некоторой комбинации того и другого.

Чтобы выполнять вычислительные задачи более эффективно, обычно можно инвестировать время и деньги в улучшение программного обеспечения, улучшение оборудования или и то, и другое. Существуют различные подходы с преимуществами и недостатками с точки зрения уменьшения задержки , увеличения пропускной способности и снижения потребления энергии . Типичные преимущества сосредоточения на программном обеспечении могут включать большую универсальность, более быструю разработку , меньшие единовременные затраты на проектирование, повышенную переносимость и простоту обновления функций или исправления ошибок за счет накладных расходов на вычисление общих операций. Преимущества сосредоточения на оборудовании могут включать ускорение , уменьшение потребления энергии , [1] меньшую задержку, увеличение параллелизма [2] и пропускной способности , а также лучшее использование площади и функциональных компонентов, доступных на интегральной схеме ; за счет меньшей возможности обновления конструкций после травления на кремнии и более высоких затрат на функциональную проверку , времени выхода на рынок и потребности в большем количестве деталей. В иерархии цифровых вычислительных систем, начиная от универсальных процессоров и заканчивая полностью настраиваемым оборудованием, существует компромисс между гибкостью и эффективностью, при этом эффективность увеличивается на порядки , когда любое приложение реализуется выше в этой иерархии. [3] Эта иерархия включает универсальные процессоры, такие как центральные процессоры, [4] более специализированные процессоры, такие как программируемые шейдеры в графических процессорах , [5] процессоры с фиксированной функцией, реализованные на программируемых пользователем вентильных матрицах (FPGA), [6] и процессоры с фиксированной функцией, реализованные на специализированных интегральных схемах (ASIC). [7]

Аппаратное ускорение выгодно для производительности и практично, когда функции фиксированы, поэтому обновления не так необходимы, как в программных решениях. С появлением перепрограммируемых логических устройств , таких как ПЛИС, ограничение аппаратного ускорения полностью фиксированными алгоритмами ослабло с 2010 года, что позволяет применять аппаратное ускорение к проблемным областям, требующим модификации алгоритмов и потока управления обработкой . [8] [9] Однако недостатком является то, что во многих проектах с открытым исходным кодом требуются проприетарные библиотеки, которые не все поставщики стремятся распространять или раскрывать, что затрудняет интеграцию в такие проекты.

Интегральные схемы предназначены для обработки различных операций как с аналоговыми, так и с цифровыми сигналами. В вычислительной технике цифровые сигналы являются наиболее распространенными и обычно представляются в виде двоичных чисел. Компьютерное оборудование и программное обеспечение используют это двоичное представление для выполнения вычислений. Это делается путем обработки булевых функций на двоичном входе и последующего вывода результатов для хранения или дальнейшей обработки другими устройствами.

Поскольку все машины Тьюринга могут выполнять любую вычислимую функцию , всегда можно разработать пользовательское оборудование, которое выполняет ту же функцию, что и заданная часть программного обеспечения. И наоборот, программное обеспечение всегда можно использовать для эмуляции функции заданной части оборудования. Пользовательское оборудование может обеспечивать более высокую производительность на ватт для тех же функций, которые могут быть указаны в программном обеспечении. Языки описания оборудования (HDL), такие как Verilog и VHDL, могут моделировать ту же семантику, что и программное обеспечение, и синтезировать проект в список соединений , который можно запрограммировать на FPGA или скомпоновать в логические вентили ASIC.

Подавляющее большинство программных вычислений происходит на машинах, реализующих архитектуру фон Неймана , которые в совокупности известны как компьютеры с хранимой программой . Компьютерные программы хранятся в виде данных и выполняются процессорами . Такие процессоры должны извлекать и декодировать инструкции, а также загружать операнды данных из памяти (как часть цикла инструкций ), чтобы выполнить инструкции, составляющие программу. Использование общего кэша для кода и данных приводит к «узкому месту фон Неймана», фундаментальному ограничению пропускной способности программного обеспечения на процессорах, реализующих архитектуру фон Неймана. Даже в модифицированной архитектуре Гарварда , где инструкции и данные имеют отдельные кэши в иерархии памяти , существуют накладные расходы на декодирование кодов операций инструкций и мультиплексирование доступных исполнительных блоков на микропроцессоре или микроконтроллере , что приводит к низкому использованию схемы. Современные процессоры, которые обеспечивают одновременную многопоточность, эксплуатируют недоиспользование доступных функциональных блоков процессора и параллелизм уровня инструкций между различными аппаратными потоками.

Аппаратные исполнительные блоки в целом не полагаются на архитектуру фон Неймана или модифицированную архитектуру Гарварда и не должны выполнять шаги выборки и декодирования инструкций цикла инструкций и нести накладные расходы этих этапов. Если необходимые вычисления указаны в аппаратном проекте уровня передачи регистров (RTL), то затраты времени и площади схемы, которые были бы понесены этапами выборки и декодирования инструкций, могут быть возвращены и использованы для других целей.

Это восстановление экономит время, мощность и площадь схемы в вычислениях. Восстановленные ресурсы могут быть использованы для увеличения параллельных вычислений, других функций, связи или памяти, а также для увеличения возможностей ввода/вывода . Это происходит за счет универсальной полезности.

Более широкая настройка RTL аппаратных конструкций позволяет новым архитектурам, таким как вычисления в памяти , архитектуры с транспортным запуском (TTA) и сети на кристалле (NoC), получать дополнительные преимущества от повышенной локальности данных в контексте выполнения, тем самым сокращая задержку вычислений и связи между модулями и функциональными блоками.

Возможности параллельной обработки настраиваемого оборудования ограничены только площадью и логическими блоками , доступными на кристалле интегральной схемы . [10] Таким образом, оборудование гораздо более свободно для обеспечения массового параллелизма, чем программное обеспечение на процессорах общего назначения, что дает возможность реализовать модель параллельной машины с произвольным доступом (PRAM).

Обычно многоядерные и многоядерные процессорные блоки строятся из схем микропроцессорных IP-ядер на одной FPGA или ASIC. [11] [12] [13] [14] [15] Аналогично, специализированные функциональные блоки могут быть составлены параллельно, как в цифровой обработке сигналов , без встраивания в процессорное IP-ядро . Поэтому аппаратное ускорение часто используется для повторяющихся, фиксированных задач, включающих небольшое условное ветвление , особенно при больших объемах данных. Именно так реализована линейка графических процессоров CUDA от Nvidia .

С ростом мобильности устройств были разработаны новые метрики, которые измеряют относительную производительность конкретных протоколов ускорения, учитывая такие характеристики, как физические размеры оборудования, энергопотребление и пропускная способность операций. Их можно свести к трем категориям: эффективность задач, эффективность реализации и гибкость. Соответствующие метрики учитывают площадь оборудования вместе с соответствующей пропускной способностью операций и потребляемой энергией. [16]

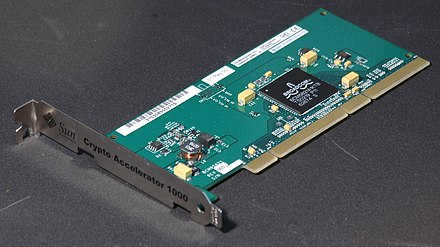

Примерами аппаратного ускорения являются функциональность ускорения бит-блита в графических процессорах (GPU), использование мемристоров для ускорения нейронных сетей и аппаратное ускорение регулярных выражений для контроля спама в серверной отрасли, предназначенное для предотвращения атак типа «отказ в обслуживании» с использованием регулярных выражений (ReDoS). [17] Аппаратное обеспечение, которое выполняет ускорение, может быть частью универсального ЦП или отдельным блоком, называемым аппаратным ускорителем, хотя обычно их называют более конкретным термином, например, 3D-ускорителем или криптографическим ускорителем .

Традиционно процессоры были последовательными (инструкции выполнялись одна за другой) и были разработаны для выполнения алгоритмов общего назначения, контролируемых выборкой инструкций (например, перемещение временных результатов в файл регистров и из него ) . Аппаратные ускорители улучшают выполнение определенного алгоритма, обеспечивая большую параллельность , имея определенные пути данных для своих временных переменных и сокращая накладные расходы на управление инструкциями в цикле выборка-декодирование-выполнение.

Современные процессоры являются многоядерными и часто имеют параллельные блоки «одна инструкция; несколько данных» ( SIMD ). Тем не менее, аппаратное ускорение все еще дает преимущества. Аппаратное ускорение подходит для любого алгоритма с интенсивными вычислениями, который часто выполняется в задаче или программе. В зависимости от гранулярности аппаратное ускорение может варьироваться от небольшого функционального блока до большого функционального блока (например, оценка движения в MPEG-2 ).

Аппаратное моделирование на ПЛИС повысило производительность цифрового фильтра.