В цифровой электронике вентиль И-НЕ ( НЕ-И ) — это логический вентиль , который выдает выходной сигнал, который является ложным, только если все его входные сигналы являются истинными; таким образом, его выходной сигнал является дополнением к выходному сигналу вентиля И. НИЗКИЙ (0) выходной сигнал получается только в том случае, если все входные сигналы вентиля являются ВЫСОКИМ (1); если какой-либо входной сигнал является НИЗКИМ (0), получается ВЫСОКИЙ (1) выходной сигнал. Вентиль И-НЕ выполнен с использованием транзисторов и диодов. По законам Де Моргана , логика двухвходового вентиля И-НЕ может быть выражена как , что делает вентиль И-НЕ эквивалентным инверторам , за которыми следует вентиль ИЛИ .

NAND-вентиль важен, поскольку любая булева функция может быть реализована с помощью комбинации NAND-вентилей. Это свойство называется « функциональной полнотой ». Он разделяет это свойство с NOR-вентилем . Цифровые системы, использующие определенные логические схемы, используют функциональную полноту NAND.

Вентили NAND с двумя или более входами доступны в виде интегральных схем в транзисторно-транзисторной логике , КМОП и других семействах логических схем .

Для вентилей NAND существует три символа: символ MIL/ ANSI , символ IEC и устаревший символ DIN , который иногда встречается на старых схемах. Символ ANSI для вентиля NAND — это стандартный вентиль AND с подключенным инверсионным пузырьком.

Функция НЕ-И( a 1 , a 2 , ..., a n ) логически эквивалентна НЕ ( a 1 AND a 2 AND ... AND a n ).

Одним из способов выражения A NAND B является , где символ обозначает И, а черта обозначает отрицание выражения под ним: по сути, просто .

Базовые реализации можно понять из изображения слева ниже: Если один из переключателей S1 или S2 открыт, подтягивающий резистор R установит выходной сигнал Q на 1 (высокий). Если S1 и S2 оба закрыты, подтягивающий резистор будет переопределен переключателями, и выход будет равен 0 (низкий).

В реализации логики NMOS с обеднением и нагрузкой, показанной в середине, переключателями являются транзисторы T2 и T3, а транзистор T1 выполняет функцию подтягивающего резистора.

В реализации КМОП справа внизу переключателями являются транзисторы T3 и T4, а подтягивающий резистор состоит из транзисторов T1 и T2, которые образуют дополнение к транзисторам T3 и T4.

Вентили NAND являются базовыми логическими вентилями и поэтому используются в микросхемах ТТЛ и КМОП .

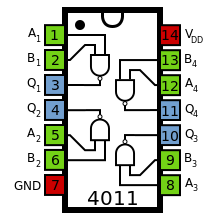

Стандартная КМОП - ИС серии 4000 — это 4011, которая включает четыре независимых двухвходовых вентиля NAND. Эти устройства доступны у многих производителей полупроводников. Они обычно доступны в форматах DIL и SOIC со сквозным отверстием . Технические описания легко доступны в большинстве баз данных технических описаний .

Доступны стандартные двух-, трех-, четырех- и восьмивходовые вентили NAND:

Вентиль NAND обладает свойством функциональной полноты , которое он разделяет с вентилем NOR . То есть любая другая логическая функция (AND, OR и т. д.) может быть реализована с использованием только вентилей NAND. [1] Весь процессор может быть создан с использованием только вентилей NAND. В микросхемах TTL, использующих многоэмиттерные транзисторы , также требуется меньше транзисторов, чем вентиль NOR.

Поскольку вентили NOR также являются функционально завершенными, если нет определенных вентилей NAND, их можно создать из вентилей NOR с использованием логики NOR . [1]