В цифровой электронике декодер адреса — это двоичный декодер , который имеет два или более входов для битов адреса и один или более выходов для сигналов выбора устройства. [1] Когда адрес для конкретного устройства появляется на адресных входах, декодер утверждает выход выбора для этого устройства. Выделенный декодер адреса с одним выходом может быть встроен в каждое устройство на адресной шине, или один декодер адреса может обслуживать несколько устройств. [2]

Один декодер адреса с n битами входного адреса может обслуживать до 2 n устройств. Несколько членов серии 7400 интегральных схем могут использоваться в качестве декодеров адреса. Например, при использовании в качестве декодера адреса 74154 [3] обеспечивает четыре входа адреса и шестнадцать (т. е. 2 4 ) выходов селектора устройств. Декодер адреса — это особое использование схемы двоичного декодера, известной как « демультиплексор » или «демультиплексор» (74154 обычно называют «демультиплексором 4-в-16»), которая имеет много других применений помимо декодирования адреса.

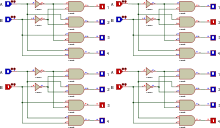

Декодеры адресов являются фундаментальными строительными блоками для систем, использующих шины . Они представлены во всех семействах и процессах интегральных схем и во всех стандартных библиотеках FPGA и ASIC . Они обсуждаются во вводных учебниках по проектированию цифровой логики. [1]

Декодер адреса — широко используемый компонент в микроэлектронике, который применяется для выбора ячеек памяти в устройствах памяти со случайной адресацией.

Такая ячейка памяти состоит из фиксированного числа элементов памяти или битов. Декодер адреса подключается к адресной шине и считывает созданный там адрес. Используя специальную логику переключения, он использует этот адрес для вычисления того, к какой ячейке памяти следует получить доступ. Затем он выбирает эту ячейку, выбирая ее через специальную линию управления. Эта линия также известна как линия выбора. В динамической памяти ( DRAM ) на матрице памяти есть линии выбора строк и столбцов, которые управляются декодерами адреса, интегрированными в чип.

В зависимости от типа декодера логика, используемая для выбора ячейки памяти, при определенных обстоятельствах может быть программируемой.

Декодер адреса также используется для выбора соответствующего модуля памяти или микросхемы памяти, когда определенный адрес предоставляется адресной шиной процессорной системы.

Для этой цели модули памяти или чипы памяти имеют входы выбора, обычно называемые штырьками выбора чипа (CS) или штырьками включения чипа (CE). Эти входы часто имеют отрицательную логическую функцию ( CS или CE ), т. е. с соседним логическим нулем (низкий уровень напряжения) выбирается.

Декодер адреса использует различную комбинаторную логику для размещения модулей памяти или чипов в адресном пространстве процессора. Модули памяти часто имеют меньшую емкость, чем адресное пространство. В большинстве случаев можно использовать несколько модулей, даже если они полностью идентичны по структуре. Необходимо убедиться, что они различаются по диапазону адресов.