Статическая оперативная память ( статическое ОЗУ или SRAM ) — это тип оперативной памяти (ОЗУ), в которой для хранения каждого бита используется схема с фиксацией (триггер) . SRAM — энергозависимая память ; данные теряются при отключении питания.

Термин статический отличает SRAM от DRAM ( динамическая оперативная память):

Полупроводниковая биполярная SRAM была изобретена в 1963 году Робертом Норманом в компании Fairchild Semiconductor . [1] SRAM металл -оксид-полупроводник (MOS-SRAM) был изобретен в 1964 году Джоном Шмидтом из Fairchild Semiconductor. Это была 64-битная MOS p-канальная SRAM. [2] [3]

SRAM была основной движущей силой любого нового процесса производства на основе КМОП -технологий с 1959 года, когда была изобретена КМОП. [4]

В 1964 году Арнольд Фарбер и Юджин Шлиг, работавшие в IBM, создали проводную ячейку памяти, используя затвор транзистора и защелку туннельного диода . Они заменили защелку двумя транзисторами и двумя резисторами — конфигурация, которая стала известна как ячейка Фарбера-Шлига. В том же году они представили раскрытие изобретения, но сначала оно было отклонено. [5] [6] В 1965 году Бенджамин Агуста и его команда из IBM создали 16-битный кремниевый чип памяти на основе ячейки Фарбера-Шлига с 80 транзисторами, 64 резисторами и 4 диодами.

В апреле 1969 года компания Intel Inc. представила свой первый продукт, Intel 3101, микросхему памяти SRAM, предназначенную для замены громоздких модулей памяти с магнитными сердечниками ; Его разрядность составляла 64 бита (в первых версиях из-за ошибки можно было использовать только 63 бита) [7] и была основана на биполярных транзисторах [8] и была разработана с использованием рубилита . [9]

Хотя SRAM можно охарактеризовать как энергозависимую память , в ней сохраняется остаточная память данных . [10]

SRAM предлагает простую модель доступа к данным и не требует схемы обновления. Производительность и надежность хорошие, а энергопотребление в режиме ожидания низкое. [11]

Поскольку для реализации SRAM требуется больше транзисторов на бит, она менее плотная и более дорогая, чем DRAM, а также имеет более высокое энергопотребление во время доступа к чтению или записи. Потребляемая мощность SRAM широко варьируется в зависимости от частоты обращения к ней. [11]

Многие категории промышленных и научных подсистем, автомобильной электроники и аналогичных встроенных систем содержат SRAM, которую в этом контексте можно называть ESRAM . [12] Некоторый объем (килобайты или меньше) также встроен практически во все современные устройства, игрушки и т. д., реализующие электронный пользовательский интерфейс.

SRAM в двухпортовой форме иногда используется для схем цифровой обработки сигналов в реальном времени . [13]

SRAM также используется в персональных компьютерах, рабочих станциях, маршрутизаторах и периферийном оборудовании: файлы регистров ЦП , внутренние кэши ЦП , внутренние кэши графического процессора и внешние кэши SRAM пакетного режима , буферы жесткого диска , буферы маршрутизатора и т. д. ЖК-экраны и принтеры также обычно используют SRAM. для сохранения изображения на дисплее (или для печати). ЖК-дисплеи могут иметь SRAM в своих контроллерах ЖК-дисплеев. SRAM использовалась в качестве основной памяти многих ранних персональных компьютеров, таких как ZX80 , TRS-80 Model 100 и VIC-20 .

Некоторые ранние карты памяти в конце 1980-х - начале 1990-х годов использовали SRAM в качестве носителя данных, для чего требовалась литиевая батарея для хранения содержимого SRAM. [14] [15]

SRAM может быть интегрирован в чип для:

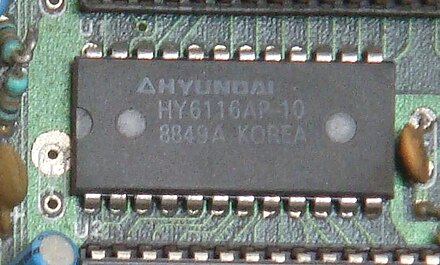

Любители, особенно энтузиасты самодельных процессоров, [16] часто предпочитают SRAM из-за простоты интерфейса. С ним гораздо проще работать, чем с DRAM, поскольку здесь нет циклов обновления, а шины адреса и данных часто доступны напрямую. [ нужна цитация ] В дополнение к шинам и соединениям питания, SRAM обычно требует только три элемента управления: включение чипа (CE), включение записи (WE) и включение вывода (OE). В синхронную SRAM также включен Clock (CLK). [ нужна цитата ]

Энергонезависимая SRAM (nvSRAM) имеет стандартную функциональность SRAM, но сохраняет данные при потере питания, обеспечивая сохранность критической информации. nvSRAM используются в самых разных ситуациях – в сетевых, аэрокосмических и медицинских, среди многих других [17] – где сохранение данных имеет решающее значение и где батареи нецелесообразны.

Псевдостатическое ОЗУ (PSRAM) — это DRAM, объединенное со схемой самообновления. [18] Внешне он выглядит как более медленный SRAM, хотя и с преимуществом в плотности/стоимости и повышенным энергопотреблением по сравнению с настоящим SRAM, и без сложности доступа, как у DRAM.

В 1990-е годы для обеспечения быстрого доступа использовалась асинхронная SRAM. Асинхронная SRAM использовалась в качестве основной памяти для небольших встроенных процессоров без кэша, используемых во всем: от промышленной электроники и измерительных систем до жестких дисков и сетевого оборудования, а также во многих других приложениях. В настоящее время синхронная SRAM (например, DDR SRAM) используется скорее аналогично синхронной DRAM – память DDR SDRAM используется скорее, чем асинхронная DRAM . Интерфейс синхронной памяти работает намного быстрее, поскольку время доступа можно значительно сократить за счет использования конвейерной архитектуры. Кроме того, поскольку DRAM намного дешевле SRAM, SRAM часто заменяют DRAM, особенно в случае, когда требуется большой объем данных. Однако память SRAM намного быстрее при произвольном (не блочном/пакетном) доступе. Поэтому память SRAM в основном используется для кэша ЦП , небольшой встроенной памяти, FIFO или других небольших буферов.

Типичная ячейка SRAM состоит из шести МОП-транзисторов и часто называется ячейкой 6T SRAM . Каждый бит в ячейке хранится на четырех транзисторах (М1, М2, М3, М4), которые образуют два инвертора с перекрестной связью. Эта ячейка хранения имеет два стабильных состояния, которые используются для обозначения 0 и 1. Два дополнительных транзистора доступа служат для управления доступом к ячейке хранения во время операций чтения и записи. 6T SRAM — наиболее распространенный тип SRAM. [19] Помимо 6T SRAM, другие типы SRAM используют 4, 5, 7, [20] 8, 9, [19] 10 (4T, 5T, 7T 8T, 9T, 10T SRAM) или больше транзисторов на бит. . [21] [22] [23] Четырехтранзисторная SRAM довольно распространена в автономных устройствах SRAM (в отличие от SRAM, используемой для кэшей ЦП), реализованная в специальных процессах с дополнительным слоем поликремния , обеспечивающим очень высокое сопротивление. подтягивающие резисторы. [24] Основным недостатком использования 4T SRAM является увеличение статической мощности из-за постоянного тока, протекающего через один из понижающих транзисторов (M1 или M2).

Иногда это используется для реализации более одного порта (чтения и/или записи), что может быть полезно в определенных типах видеопамяти и файлах регистров , реализованных с помощью многопортовой схемы SRAM.

Как правило, чем меньше транзисторов требуется на ячейку, тем меньше может быть каждая ячейка. Поскольку стоимость обработки кремниевой пластины относительно фиксирована, использование ячеек меньшего размера и, следовательно, упаковка большего количества битов на одну пластину снижает стоимость бита памяти.

Возможны ячейки памяти, в которых используется менее четырех транзисторов; однако такие ячейки 3T [25] [26] или 1T представляют собой DRAM, а не SRAM (даже так называемую 1T-SRAM ).

Доступ к ячейке осуществляется с помощью словной линии (WL на рисунке), которая управляет двумя транзисторами доступа M 5 и M 6 , которые, в свою очередь, контролируют, должна ли ячейка быть подключена к битовым линиям: BL и BL. Они используются для передачи данных как для операций чтения, так и для операций записи. Хотя наличие двух битовых линий не является строго обязательным, обычно используются как сигнал, так и его инверсия, чтобы улучшить запас по шуму и скорость.

Во время доступа для чтения битовые линии активно управляются инверторами в ячейке SRAM. Это улучшает пропускную способность SRAM по сравнению с DRAM — в DRAM битовая линия подключена к запоминающим конденсаторам, и распределение заряда заставляет битовую линию колебаться вверх или вниз. Симметричная структура SRAM также обеспечивает дифференциальную передачу сигналов , что облегчает обнаружение небольших колебаний напряжения. Еще одно отличие DRAM, которое способствует ускорению SRAM, заключается в том, что коммерческие микросхемы принимают все биты адреса одновременно. Для сравнения, в обычных DRAM адрес мультиплексирован на две половины, т.е. старшие биты, за которыми следуют младшие биты, по одним и тем же выводам корпуса, чтобы сохранить их размер и стоимость на низком уровне.

Размер SRAM с m адресными строками и n строками данных составляет 2 m слов или 2 m × n бит. Наиболее распространенный размер слова составляет 8 бит, что означает, что один байт может быть прочитан или записан в каждое из 2 м разных слов внутри микросхемы SRAM. Некоторые распространенные микросхемы SRAM имеют 11 адресных линий (таким образом, емкость 2 11 = 2048 = 2 тыс. слов) и 8-битное слово, поэтому их называют «2k × 8 SRAM».

Размеры ячейки SRAM на микросхеме определяются минимальным размером элемента процесса, используемого для изготовления микросхемы.

Ячейка SRAM имеет три состояния:

SRAM, работающая в режимах чтения и записи, должна обладать «читаемостью» и «стабильностью записи» соответственно. Три разных состояния работают следующим образом:

Если словная линия не установлена, транзисторы доступа М 5 и М 6 отсоединяют ячейку от битовых линий. Два инвертора с перекрестной связью, образованные M 1 – M 4 , будут продолжать усиливать друг друга, пока они подключены к источнику питания.

Теоретически для чтения требуется только утверждение словной линии WL и считывание состояния ячейки SRAM с помощью одного транзистора доступа и битовой линии, например M 6 , BL. Однако битовые линии относительно длинные и имеют большую паразитную емкость . Для ускорения чтения на практике используется более сложный процесс: цикл чтения начинается с предварительной зарядки обеих битовых линий BL и BL до высокого (логическая 1 ) напряжения. Затем установка словной линии WL включает оба транзистора доступа M 5 и M 6 , что приводит к небольшому падению напряжения на одной битовой линии BL. Тогда между линиями BL и BL будет небольшая разница напряжений. Усилитель чувствительности определит, какая линия имеет более высокое напряжение, и таким образом определит, была ли сохранена 1 или 0. Чем выше чувствительность усилителя считывания, тем быстрее операция считывания. Поскольку NMOS более мощный, процесс понижения уровня проще. Поэтому битовые линии традиционно предварительно заряжаются до высокого напряжения. Многие исследователи также пытаются выполнить предварительную зарядку при несколько низком напряжении, чтобы снизить энергопотребление. [27] [28]

Цикл записи начинается с применения записываемого значения к битовым строкам. Чтобы записать 0, к битовым строкам применяется 0, например, установка BL в 1 и BL в 0. Это похоже на подачу импульса сброса на SR-защелку , которая заставляет триггер изменить состояние. 1 записывается путем инвертирования значений битовых строк. Затем утверждается WL, и значение, которое должно быть сохранено, фиксируется. Это работает, потому что входные драйверы битовых линий спроектированы так, чтобы быть намного более сильными, чем относительно слабые транзисторы в самой ячейке, поэтому они могут легко переопределить предыдущее состояние инверторы с перекрестной связью. На практике NMOS-транзисторы доступа M5 и M6 должны быть мощнее, чем нижние NMOS-транзисторы (M1 , M3 ) или верхние PMOS- транзисторы ( M2 , M4 ). Этого легко добиться, поскольку транзисторы PMOS намного слабее, чем NMOS при одинаковом размере. Следовательно, когда одна пара транзисторов (например, M 3 и M 4 ) лишь слегка подавляется процессом записи, напряжение затвора противоположной пары транзисторов (M 1 и M 2 ) также изменяется. Это означает, что транзисторы М 1 и М 2 можно легче переопределить и так далее. Таким образом, инверторы с перекрестной связью ускоряют процесс записи.

ОЗУ со временем доступа 70 нс выдаст действительные данные в течение 70 нс с момента, когда адресные строки станут действительными. Некоторые ячейки SRAM имеют «страничный режим», в котором слова страницы (256, 512 или 1024 слова) могут считываться последовательно со значительно более коротким временем доступа (обычно примерно 30 нс). Страница выбирается путем установки верхних строк адреса, а затем последовательно считываются слова, проходя через нижние строки адреса.

С появлением транзисторов FinFET для ячеек SRAM они начали страдать от увеличения неэффективности размеров ячеек. За последние 30 лет (с 1987 по 2017 год) при неуклонном уменьшении размера транзистора (размера узла) сокращение занимаемой площади самой топологии ячеек SRAM замедлилось, что усложнило более плотную упаковку ячеек. [4]

Помимо проблем с размером, серьезной проблемой современных ячеек SRAM является утечка статического тока. Ток, который течет от положительного источника питания (V dd ), через элемент и на землю, увеличивается экспоненциально при повышении температуры элемента. Потребление энергии ячейки происходит как в активном, так и в режиме ожидания, таким образом, тратится полезная энергия без совершения какой-либо полезной работы. Несмотря на то, что за последние 20 лет проблема была частично решена с помощью метода напряжения удержания данных (DRV) со степенью уменьшения от 5 до 10, уменьшение размера узла привело к падению скорости сокращения примерно до 2. [4]

Из-за этих двух проблем разработка энергоэффективной и плотной памяти SRAM стала более сложной, что побудило полупроводниковую промышленность искать альтернативы, такие как STT-MRAM и F-RAM . [4] [29]

В 2019 году французский институт сообщил об исследовании 28-нм изготовленной микросхемы для Интернета вещей . [30] Он был основан на полностью обедненных кремниевых транзисторах с изолятором (FD-SOI), имел двухпортовую шину памяти SRAM для синхронного/асинхронного доступа и селективное виртуальное заземление (SVGND). В исследовании утверждалось, что удалось достичь сверхнизкого тока SVGND в режимах «сна» и чтения за счет точной настройки его напряжения. [30]

{{cite web}}: |last=имеет общее имя ( справка ){{cite web}}: |last=имеет общее имя ( справка )