В электронике проходная транзисторная логика (PTL) описывает несколько логических семейств , используемых при проектировании интегральных схем . Это уменьшает количество транзисторов, используемых для создания различных логических элементов , за счет исключения избыточных транзисторов. Транзисторы используются в качестве переключателей для передачи логических уровней между узлами схемы, а не в качестве переключателей, подключенных непосредственно к питающему напряжению. [1] Это уменьшает количество активных устройств, но имеет тот недостаток, что разница напряжений между высоким и низким логическими уровнями уменьшается на каждом этапе (поскольку проходные транзисторы обладают некоторым сопротивлением и не обеспечивают восстановление уровня). Каждый последовательно включенный транзистор менее насыщен на выходе, чем на входе. [2] Если несколько устройств соединены последовательно в логический путь, может потребоваться вентиль традиционной конструкции для восстановления напряжения сигнала до полного значения. Напротив, обычная логика КМОП переключает транзисторы так, что выход подключается к одной из шин питания (напоминая схему с открытым коллектором ), поэтому уровни логического напряжения в последовательной цепи не уменьшаются. Для обеспечения адекватной производительности может потребоваться моделирование цепей.

Логика проходных транзисторов часто использует меньше транзисторов, работает быстрее и требует меньше энергии, чем та же функция, реализованная с помощью тех же транзисторов в полностью комплементарной КМОП-логике. [3]

XOR имеет карту Карно наихудшего случая — если она реализована на основе простых вентилей, для нее требуется больше транзисторов, чем для любой другой функции. В те времена, когда транзисторы были более дорогими, разработчики Z80 и многих других микросхем стремились сэкономить несколько транзисторов, реализовав исключающее ИЛИ с использованием логики проходного транзистора, а не простых вентилей. [4]

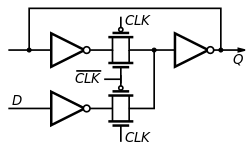

Транзисторы MOSFET представляют собой электронные переключатели , которые включают или выключают путь между стоком и истоком в зависимости от сигнала напряжения на их затворе (например, тактового сигнала в ячейке SRAM или закрытой D-защелке ).

Поскольку проходные транзисторы не обеспечивают восстановление уровня и поскольку их проводящий путь имеет небольшое ненулевое сопротивление, увеличивается RC-задержка для зарядки входной емкости следующего логического каскада (которая включает в себя паразитную емкость в дополнение к емкости затвора следующего каскада) до допустимого уровня. Уровни напряжения с высоким или низким логическим уровнем.

Для обеспечения адекватной производительности может потребоваться моделирование цепей.

Некоторые авторы используют термин «логика дополнительных проходных транзисторов» для обозначения стиля реализации логических элементов, в котором используются передающие элементы, состоящие как из проходных транзисторов NMOS, так и из PMOS. [5]

Другие авторы используют термин «комплементарная транзисторная логика» (CPL) для обозначения стиля реализации логических вентилей, где каждый вентиль состоит из сети проходных транзисторов только для NMOS, за которой следует выходной инвертор CMOS. [6] [7] [8]

Другие авторы используют термин «дополнительная транзисторная логика» (CPL) для обозначения стиля реализации логических элементов с использованием двухканального кодирования. Каждый вентиль CPL имеет два выходных провода: положительный сигнал и дополнительный сигнал, что устраняет необходимость в инверторах. [9] [10] [11]

Дополнительная транзисторная логика или «Дифференциальная транзисторная логика» относится к семейству логических схем , которое разработано для определенных преимуществ. Это семейство логики обычно используется для мультиплексоров и триггеров . [ нужна цитата ]

CPL использует последовательные транзисторы для выбора между возможными инвертированными выходными значениями логики, выходной сигнал которой управляет инвертором. Передающие вентили CMOS состоят из nMOS и pMOS транзисторов, соединенных параллельно.

Существуют статические и динамические типы проходной транзисторной логики с разными свойствами в отношении скорости, мощности и работы при низком напряжении. [12] По мере снижения напряжения питания интегральной схемы недостатки проходной транзисторной логики становятся более существенными; пороговое напряжение транзисторов становится большим по сравнению с напряжением питания, что сильно ограничивает количество последовательных каскадов. Поскольку для управления проходными транзисторами часто требуются дополнительные входы, требуются дополнительные логические каскады.