PCI Express ( Peripheral Component Interconnect Express ), официально сокращенно PCIe или PCI-e , [2] — это высокоскоростной стандарт последовательной шины расширения компьютера , разработанный для замены старых стандартов шин PCI , PCI-X и AGP . Это общий интерфейс материнской платы для видеокарт персональных компьютеров , карт захвата , звуковых карт , хост-адаптеров жестких дисков , твердотельных накопителей , Wi-Fi и аппаратных соединений Ethernet . [3] PCIe имеет многочисленные улучшения по сравнению со старыми стандартами, включая более высокую максимальную пропускную способность системной шины, меньшее количество контактов ввода-вывода и меньший физический размер, лучшее масштабирование производительности для шинных устройств, более подробный механизм обнаружения и сообщения об ошибках (Advanced Error Reporting, AER) [4] и собственную функциональность горячей замены . Более поздние версии стандарта PCIe обеспечивают аппаратную поддержку виртуализации ввода-вывода .

Электрический интерфейс PCI Express измеряется числом одновременных полос. [5] (Полоса — это одна линия отправки/приема данных, аналогичная «однополосной дороге», имеющей одну полосу движения в обоих направлениях.) Интерфейс также используется во множестве других стандартов — в частности, в интерфейсе карты расширения ноутбука под названием ExpressCard . Он также используется в интерфейсах хранения данных SATA Express , U.2 (SFF-8639) и M.2 .

Официальные спецификации поддерживаются и разрабатываются PCI-SIG (PCI Special Interest Group ) — группой из более чем 900 компаний, которая также поддерживает общепринятые спецификации PCI .

Концептуально шина PCI Express является высокоскоростной последовательной заменой старой шины PCI/PCI-X. [8] Одним из ключевых отличий между шиной PCI Express и старой PCI является топология шины; PCI использует общую параллельную архитектуру шины , в которой хост PCI и все устройства совместно используют общий набор адресов, данных и линий управления. Напротив, PCI Express основан на топологии точка-точка с отдельными последовательными соединениями, соединяющими каждое устройство с корневым комплексом (хостом). Из-за своей общей топологии шины доступ к старой шине PCI является арбитражным (в случае нескольких ведущих) и ограничивается одним ведущим устройством за раз в одном направлении. Кроме того, старая схема синхронизации PCI ограничивает тактовую частоту шины самым медленным периферийным устройством на шине (независимо от устройств, участвующих в транзакции шины). Напротив, шина PCI Express поддерживает полнодуплексную связь между любыми двумя конечными точками без неотъемлемого ограничения на одновременный доступ через несколько конечных точек.

С точки зрения протокола шины, связь PCI Express инкапсулируется в пакеты. Работа по пакетированию и депакетированию данных и трафика сообщений о состоянии обрабатывается транзакционным уровнем порта PCI Express (описанным ниже). Радикальные различия в электрической сигнализации и протоколе шины требуют использования другого механического форм-фактора и разъемов расширения (и, следовательно, новых материнских плат и новых плат адаптеров); слоты PCI и слоты PCI Express не являются взаимозаменяемыми. На программном уровне PCI Express сохраняет обратную совместимость с PCI; устаревшее системное программное обеспечение PCI может обнаруживать и настраивать новые устройства PCI Express без явной поддержки стандарта PCI Express, хотя новые функции PCI Express недоступны.

Канал PCI Express между двумя устройствами может иметь размер от одной до 16 полос. В многополосном канале пакетные данные распределяются по полосам, а пиковая пропускная способность данных масштабируется с общей шириной канала. Количество полос автоматически согласовывается во время инициализации устройства и может быть ограничено любой конечной точкой. Например, однополосная карта PCI Express (x1) может быть вставлена в многополосный слот (x4, x8 и т. д.), а цикл инициализации автоматически согласовывает наибольшее взаимно поддерживаемое количество полос. Канал может динамически понижать свою конфигурацию для использования меньшего количества полос, обеспечивая отказоустойчивость в случае наличия плохих или ненадежных полос. Стандарт PCI Express определяет ширину канала x1, x2, x4, x8 и x16. Также были определены каналы PCIe 5.0, x12 и x32 включительно, но никогда не использовались. [9] Это позволяет шине PCI Express обслуживать как чувствительные к стоимости приложения, где не требуется высокая пропускная способность, так и критически важные к производительности приложения, такие как 3D-графика, сетевые технологии ( 10 Gigabit Ethernet или многопортовый Gigabit Ethernet ) и корпоративные хранилища ( SAS или Fibre Channel ). Слоты и разъемы определены только для подмножества этих значений ширины, а ширина соединения между ними использует следующий больший размер физического слота.

Для справки, устройство PCI-X (133 МГц 64-бит) и устройство PCI Express 1.0, использующее четыре полосы (x4), имеют примерно одинаковую пиковую скорость передачи данных в одном направлении 1064 МБ/с. Шина PCI Express имеет потенциал для лучшей производительности, чем шина PCI-X, в случаях, когда несколько устройств передают данные одновременно или если связь с периферийным устройством PCI Express является двунаправленной .

Устройства PCI Express взаимодействуют через логическое соединение, называемое межсоединением [ 10] или связью . Связь — это канал связи точка-точка между двумя портами PCI Express, позволяющий им обоим отправлять и получать обычные запросы PCI (конфигурация, ввод-вывод или чтение/запись памяти) и прерывания ( INTx , MSI или MSI-X ). На физическом уровне связь состоит из одной или нескольких полос . [10] Низкоскоростные периферийные устройства (например, карта Wi-Fi 802.11 ) используют однополосную связь (x1), в то время как графический адаптер обычно использует гораздо более широкую и, следовательно, более быструю 16-полосную связь (x16).

Полоса состоит из двух дифференциальных сигнальных пар, одна пара для приема данных, а другая для передачи. Таким образом, каждая полоса состоит из четырех проводов или сигнальных трасс . Концептуально каждая полоса используется как полнодуплексный поток байтов , транспортирующий пакеты данных в восьмибитном «байтовом» формате одновременно в обоих направлениях между конечными точками канала. [11] Физические каналы PCI Express могут содержать 1, 4, 8 или 16 каналов. [12] [6] : 4, 5 [10] Количество каналов записывается с префиксом «x» (например, «x8» представляет восьмиканальную карту или слот), причем x16 является наибольшим размером в общем использовании. [13] Размеры каналов также упоминаются с помощью терминов «ширина» или «по», например, восьмиканальный слот может упоминаться как «по 8» или как «ширина 8 каналов».

Механические размеры карт см. ниже.

Архитектура связанной последовательной шины была выбрана вместо традиционной параллельной шины из-за присущих последней ограничений, включая полудуплексный режим работы, избыточное количество сигналов и изначально более низкую пропускную способность из-за временного сдвига . Временной сдвиг возникает из-за того, что отдельные электрические сигналы в параллельном интерфейсе проходят по проводникам разной длины, на потенциально разных слоях печатной платы (PCB) и, возможно, с разной скоростью сигнала . Несмотря на то, что сигналы в параллельном интерфейсе передаются одновременно как одно слово , они имеют разную продолжительность перемещения и достигают своих пунктов назначения в разное время. Когда период тактовой частоты интерфейса короче наибольшей разницы во времени между прибытиями сигналов, восстановление переданного слова становится невозможным. Поскольку временной сдвиг по параллельной шине может составлять несколько наносекунд, результирующее ограничение полосы пропускания находится в диапазоне сотен мегагерц.

Последовательный интерфейс не демонстрирует временной перекос, поскольку в каждом направлении в каждой полосе есть только один дифференциальный сигнал, и нет внешнего тактового сигнала, поскольку информация о синхронизации встроена в сам последовательный сигнал. Таким образом, типичные ограничения полосы пропускания последовательных сигналов находятся в диапазоне нескольких гигагерц. PCI Express является одним из примеров общей тенденции к замене параллельных шин последовательными соединениями; другие примеры включают Serial ATA (SATA), USB , Serial Attached SCSI (SAS), FireWire (IEEE 1394) и RapidIO . В цифровом видео примерами часто используемых являются DVI , HDMI и DisplayPort .

Многоканальная последовательная конструкция повышает гибкость за счет возможности выделять меньше полос для более медленных устройств.

Карта PCI Express вставляется в слот своего физического размера или больше (с x16 в качестве наибольшего используемого размера), но может не влезть в меньший слот PCI Express; например, карта x16 может не влезть в слот x4 или x8. Некоторые слоты используют открытые гнезда, чтобы позволить физически более длинные карты и согласовать наилучшее доступное электрическое и логическое соединение.

Количество полос, фактически подключенных к слоту, также может быть меньше, чем количество, поддерживаемое физическим размером слота. Примером является слот x16, работающий на x4, который принимает любую карту x1, x2, x4, x8 или x16, но обеспечивает только четыре полосы. Его спецификация может читаться как «x16 (режим x4)», в то время как «механическая @ электрическая» нотация (например, «x16 @ x4») также распространена. [ необходима цитата ] Преимущество заключается в том, что такие слоты могут вмещать более широкий диапазон карт PCI Express, не требуя от аппаратной части материнской платы поддержки полной скорости передачи данных. Стандартные механические размеры — x1, x4, x8 и x16. Карты, использующие количество полос, отличное от стандартных механических размеров, должны физически соответствовать следующему большему механическому размеру (например, карта x2 использует размер x4 или карта x12 использует размер x16).

Сами карты проектируются и производятся в различных размерах. Например, твердотельные накопители (SSD), которые поставляются в виде карт PCI Express, часто используют HHHL (половинная высота, половинная длина) и FHHL (полная высота, половинная длина) для описания физических размеров карты. [15] [16]

Современные (с 2012 года [17] ) игровые видеокарты обычно превышают высоту и толщину, указанные в стандарте PCI Express, из-за необходимости в более мощных и тихих вентиляторах охлаждения , поскольку игровые видеокарты часто выделяют сотни ватт тепла. [18] Современные компьютерные корпуса часто шире, чтобы вместить эти более высокие карты, но не всегда. Поскольку полноразмерные карты (312 мм) встречаются редко, современные корпуса иногда не могут их вместить. Толщина этих карт также обычно занимает пространство от 2 до 5 [19] слотов PCIe. Фактически, даже методология измерения карт различается у разных поставщиков, некоторые включают размер металлической скобы в размеры, а другие нет.

Например, сравнивая три видеокарты высокого класса, выпущенные в 2020 году: карта Sapphire Radeon RX 5700 XT имеет высоту 135 мм (без учета металлического кронштейна), что превышает стандартную высоту PCIe на 28 мм, [20] другая карта Radeon RX 5700 XT от XFX имеет толщину 55 мм (т. е. 2,7 слота PCI по 20,32 мм), занимая 3 слота PCIe, [21] в то время как видеокарта Asus GeForce RTX 3080 занимает два слота и имеет размеры 140,1 мм × 318,5 мм × 57,8 мм, что превышает максимальную высоту, длину и толщину PCI Express соответственно. [22]

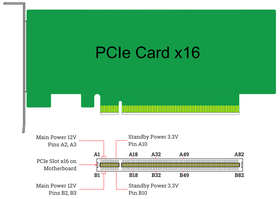

В следующей таблице указаны проводники с каждой стороны краевого разъема на карте PCI Express. Сторона пайки печатной платы (PCB) — это сторона A, а сторона компонентов — это сторона B. [23] Контакты PRSNT1# и PRSNT2# должны быть немного короче остальных, чтобы гарантировать, что карта с горячим подключением полностью вставлена. Контакт WAKE# использует полное напряжение для пробуждения компьютера, но должен быть поднят от резервного питания, чтобы указать, что карта способна к пробуждению. [24]

Все карты PCI Express могут потреблять до3 А в+3,3 В (9,9 Вт ). Количество +12 В и общая мощность, которую они могут потреблять, зависят от форм-фактора и роли карты: [29] : 35–36 [30] [31]

Дополнительные разъемы добавить75 Вт (6-контактный) или150 Вт (8-контактный) питания +12 В дляВсего 300 Вт ( 2 × 75 Вт + 1 × 150 Вт ).

Некоторые карты используют два 8-контактных разъема, но по состоянию на 2018 год это еще не было стандартизировано [update], поэтому такие карты не должны иметь официальный логотип PCI Express. Эта конфигурация позволяет в общей сложности 375 Вт ( 1 × 75 Вт + 2 × 150 Вт ) и, скорее всего, будет стандартизирована PCI-SIG со стандартом PCI Express 4.0. [ требуется обновление ] 8-контактный разъем PCI Express можно спутать с разъемом EPS12V , который в основном используется для питания SMP и многоядерных систем. Разъемы питания являются вариантами разъемов серии Molex Mini-Fit Jr. [32]

16-контактный разъем 12VHPWR является стандартом для подключения графических процессоров (GPU) к источникам питания компьютера для подачи питания мощностью до 600 Вт. Он был представлен в 2022 году для замены предыдущих 6- и 8-контактных разъемов питания для GPU. Основной целью было удовлетворение растущих требований к питанию высокопроизводительных GPU. Он был заменен незначительной ревизией под названием 12V-2x6, которая изменила разъем, чтобы гарантировать, что контакты датчика контактируют только в том случае, если контакты питания установлены правильно.

Первоначальный разъем был официально принят как часть PCI Express 5.x, [37] а пересмотренная конструкция разъема 12V-2x6 была принята позже. [38]

PCI Express Mini Card (также известная как Mini PCI Express , Mini PCIe , Mini PCI-E , mPCIe и PEM ), основанная на PCI Express, является заменой форм-фактора Mini PCI . Она разработана PCI-SIG . Хост-устройство поддерживает как PCI Express, так и USB 2.0, и каждая карта может использовать любой стандарт. Большинство ноутбуков, выпущенных после 2005 года, используют PCI Express для карт расширения; однако, по состоянию на 2015 год [update], многие поставщики переходят на использование более нового форм-фактора M.2 для этой цели. [39]

Из-за различных размеров карты PCI Express Mini Cards физически несовместимы со стандартными полноразмерными слотами PCI Express; однако существуют пассивные адаптеры, которые позволяют использовать их в полноразмерных слотах. [40]

Размеры карт PCI Express Mini Card составляют 30 мм × 50,95 мм (ширина × длина) для полной карты Mini Card. Имеется 52-контактный краевой разъем , состоящий из двух смещенных рядов с шагом 0,8 мм. Каждый ряд имеет восемь контактов, зазор, эквивалентный четырем контактам, затем еще 18 контактов. Платы имеют толщину 1,0 мм, не считая компонентов. Также указывается «Half Mini Card» (иногда сокращенно HMC), имеющая приблизительно половину физической длины 26,8 мм. Существуют также карты mini PCIe половинного размера, которые имеют размеры 30 x 31,90 мм, что составляет примерно половину длины карты mini PCIe полного размера. [41] [42]

Краевые разъемы PCI Express Mini Card обеспечивают несколько подключений и шин:

Несмотря на общий форм-фактор Mini PCI Express, слот mSATA не обязательно электрически совместим с Mini PCI Express. По этой причине только некоторые ноутбуки совместимы с дисками mSATA. Большинство совместимых систем основаны на архитектуре процессора Intel Sandy Bridge с использованием платформы Huron River. Такие ноутбуки, как серии ThinkPad T, W и X от Lenovo, выпущенные в марте–апреле 2011 года, поддерживают карту mSATA SSD в слоте для карты WWAN . ThinkPad Edge E220s/E420s и Lenovo IdeaPad Y460/Y560/Y570/Y580 также поддерживают mSATA. [43] Напротив, серия L среди прочих может поддерживать только карты M.2, использующие стандарт PCIe в слоте WWAN.

Некоторые ноутбуки (в частности, Asus Eee PC , Apple MacBook Air , а также Dell mini9 и mini10) используют вариант карты PCI Express Mini Card в качестве SSD . Этот вариант использует зарезервированные и несколько незарезервированных контактов для реализации сквозного интерфейса SATA и IDE, оставляя нетронутыми только USB, линии заземления и иногда основную шину PCIe x1. [44] Это делает флэш-накопители miniPCIe и твердотельные накопители, продаваемые для нетбуков, в значительной степени несовместимыми с настоящими реализациями PCI Express Mini.

Кроме того, типичный Asus miniPCIe SSD имеет длину 71 мм, из-за чего модель Dell 51 мм часто (неправильно) называют половинной длиной. Настоящий 51 мм Mini PCIe SSD был анонсирован в 2009 году с двумя сложенными слоями печатной платы, что обеспечивает большую емкость хранения. Анонсированная конструкция сохраняет интерфейс PCIe, что делает ее совместимой со стандартным слотом mini PCIe. Пока не разработано ни одного рабочего продукта.

У Intel есть множество настольных плат с разъемом PCIe x1 Mini-Card, которые обычно не поддерживают mSATA SSD. Список настольных плат, которые изначально поддерживают mSATA в разъеме PCIe x1 Mini-Card (обычно мультиплексированном с портом SATA), представлен на сайте поддержки Intel. [45]

M.2 заменяет стандарт mSATA и Mini PCIe. [46] Интерфейсы компьютерной шины, предоставляемые через разъем M.2, — это PCI Express 3.0 (до четырех полос), Serial ATA 3.0 и USB 3.0 (один логический порт для каждого из последних двух). Выбор поддерживаемых интерфейсов остается за производителем хоста или устройства M.2 в зависимости от желаемого уровня поддержки хоста и типа устройства.

Спецификации внешнего кабеля PCI Express (также известного как внешний PCI Express , кабельный PCI Express или ePCIe ) были опубликованы PCI-SIG в феврале 2007 года. [47] [48]

Стандартные кабели и разъемы были определены для ширины соединения x1, x4, x8 и x16 со скоростью передачи 250 МБ/с на полосу. PCI-SIG также ожидает, что норма будет развиваться до 500 МБ/с, как в PCI Express 2.0. Примером использования Cabled PCI Express является металлический корпус, содержащий несколько слотов PCIe и схему адаптера PCIe-to-ePCIe. Это устройство было бы невозможно без спецификации ePCIe.

OCuLink (сокращение от «optical-copper link», поскольку Cu — химический символ меди ) — это расширение для «кабельной версии PCI Express». Версия 1.0 OCuLink, выпущенная в октябре 2015 года, поддерживает до 4 линий PCIe 3.0 (3,9 ГБ/с) по медному кабелю; в будущем может появиться оптоволоконная версия.

Последняя версия OCuLink, OCuLink-2, поддерживает скорость до 16 ГБ/с (PCIe 4.0 x8) [49] , тогда как максимальная пропускная способность кабеля USB 4 составляет 10 ГБ/с.

Первоначально OCuLink предназначался для использования в ноутбуках для подключения мощных внешних графических процессоров, однако популярность OCuLink в первую очередь обусловлена его использованием для соединений PCIe в серверах, что является более распространенным применением. [50]

Множество других форм-факторов используют или могут использовать PCIe. К ним относятся:

Разъем слота PCIe может также переносить протоколы, отличные от PCIe. Некоторые наборы микросхем Intel серии 9xx поддерживают Serial Digital Video Out , фирменную технологию, которая использует слот для передачи видеосигналов от интегрированной графики центрального процессора вместо PCIe, используя поддерживаемую надстройку.

Протокол уровня транзакций PCIe может также использоваться в некоторых других соединениях, которые электрически не являются PCIe:

На ранних этапах разработки PCIe изначально назывался HSI ( High Speed Interconnect ), а затем был переименован в 3GIO ( 3rd Generation I/O ), прежде чем окончательно остановиться на названии PCI-SIG PCI Express . Техническая рабочая группа под названием Arapaho Work Group (AWG) разработала стандарт. Для первоначальных проектов AWG состояла только из инженеров Intel; впоследствии AWG расширилась, включив в себя партнеров по отрасли.

С тех пор PCIe претерпел несколько крупных и мелких изменений, улучшивших производительность и другие характеристики.

В 2003 году PCI-SIG представила PCIe 1.0a со скоростью передачи данных на линию 250 МБ/с и скоростью передачи данных 2,5 гигатранзакций в секунду (ГТ/с).

Скорость передачи выражается в передачах в секунду, а не в битах в секунду, поскольку количество передач включает служебные биты, которые не обеспечивают дополнительную пропускную способность; [56] PCIe 1.x использует схему кодирования 8b/10b , что приводит к 20% (= 2/10) накладных расходов на необработанную полосу пропускания канала. [57] Таким образом, в терминологии PCIe скорость передачи относится к кодированной скорости передачи битов: 2,5 ГТ/с — это 2,5 Гбит/с на кодированном последовательном канале. Это соответствует 2,0 Гбит/с предварительно кодированных данных или 250 МБ/с, что в PCIe называется пропускной способностью.

В 2005 году PCI-SIG [58] представила PCIe 1.1. Эта обновленная спецификация включает в себя разъяснения и несколько улучшений, но полностью совместима с PCI Express 1.0a. Никаких изменений в скорости передачи данных не было.

PCI-SIG объявила о доступности спецификации PCI Express Base 2.0 15 января 2007 года. [59] Стандарт PCIe 2.0 удваивает скорость передачи по сравнению с PCIe 1.0 до 5 ГТ/с, а пропускная способность на полосу увеличивается с 250 МБ/с до 500 МБ/с. Следовательно, 16-полосный разъем PCIe (x16) может поддерживать совокупную пропускную способность до 8 ГБ/с.

Слоты материнской платы PCIe 2.0 полностью обратно совместимы с картами PCIe v1.x. Карты PCIe 2.0 также, как правило, обратно совместимы с материнскими платами PCIe 1.x, используя доступную пропускную способность PCI Express 1.1. В целом, работают графические карты или материнские платы, разработанные для v2.0, а другие — v1.1 или v1.0a.

PCI-SIG также заявила, что PCIe 2.0 отличается усовершенствованиями протокола передачи данных «точка-точка» и его программной архитектуры. [60]

Первым чипсетом Intel с поддержкой PCIe 2.0 был X38 , и платы начали поставляться от различных поставщиков ( Abit , Asus , Gigabyte ) с 21 октября 2007 года. [61] AMD начала поддерживать PCIe 2.0 с серии чипсетов AMD 700 , а nVidia начала с MCP72 . [62] Все предыдущие чипсеты Intel, включая чипсет Intel P35 , поддерживали PCIe 1.1 или 1.0a. [63]

Как и 1.x, PCIe 2.0 использует схему кодирования 8b/10b , обеспечивая тем самым эффективную максимальную скорость передачи данных 4 Гбит/с на линию при скорости необработанных данных 5 ГТ/с.

PCI Express 2.1 (со спецификацией от 4 марта 2009 года) поддерживает большую часть систем управления, поддержки и устранения неполадок, запланированных для полной реализации в PCI Express 3.0. Однако скорость такая же, как у PCI Express 2.0. Увеличение мощности от слота нарушает обратную совместимость между картами PCI Express 2.1 и некоторыми старыми материнскими платами с 1.0/1.0a, но большинство материнских плат с разъемами PCI Express 1.1 поставляются с обновлением BIOS их производителями через утилиты для поддержки обратной совместимости карт с PCIe 2.1.

Спецификация PCI Express 3.0 Base revision 3.0 была выпущена в ноябре 2010 года после нескольких задержек. В августе 2007 года PCI-SIG объявила, что PCI Express 3.0 будет поддерживать скорость передачи данных 8 гигатранзакций в секунду (ГТ/с) и что она будет обратно совместима с существующими реализациями PCI Express. В то же время было также объявлено, что окончательная спецификация для PCI Express 3.0 будет отложена до второго квартала 2010 года. [64] Новые функции для спецификации PCI Express 3.0 включали ряд оптимизаций для улучшенной сигнализации и целостности данных, включая выравнивание передатчика и приемника, улучшения ФАПЧ , восстановление данных часов и улучшения каналов в текущих поддерживаемых топологиях. [65]

После шестимесячного технического анализа возможности масштабирования пропускной способности межсоединений PCI Express, анализ PCI-SIG показал, что 8 гигатранзакций в секунду могут быть изготовлены с использованием основного кремниевого технологического процесса и развернуты с использованием существующих недорогих материалов и инфраструктуры, сохраняя при этом полную совместимость (с незначительным влиянием) со стеком протоколов PCI Express.

PCI Express 3.0 обновил схему кодирования до 128b/130b с предыдущей кодировки 8b/10b , сократив накладные расходы на полосу пропускания с 20% PCI Express 2.0 до приблизительно 1,54% (= 2/130). Скорость передачи данных PCI Express 3.0 8 ГТ/с эффективно обеспечивает 985 МБ/с на полосу, почти удваивая полосу пропускания по сравнению с PCI Express 2.0. [55]

18 ноября 2010 года PCI Special Interest Group официально опубликовала окончательную версию спецификации PCI Express 3.0 для своих членов, чтобы они могли создавать устройства на основе этой новой версии PCI Express. [66]

В сентябре 2013 года было объявлено о выпуске спецификации PCI Express 3.1 в конце 2013 или начале 2014 года, объединяющей различные улучшения опубликованной спецификации PCI Express 3.0 в трех областях: управление питанием, производительность и функциональность. [53] [67] Она была выпущена в ноябре 2014 года. [68]

29 ноября 2011 года PCI-SIG предварительно анонсировала PCI Express 4.0, [69] обеспечивая скорость передачи данных 16 ГТ/с, что удваивает пропускную способность, предоставляемую PCI Express 3.0, до 31,5 ГБ/с в каждом направлении для конфигурации с 16 линиями, сохраняя при этом обратную и прямую совместимость как в программной поддержке, так и в используемом механическом интерфейсе. [70] Спецификации PCI Express 4.0 также приносят OCuLink-2, альтернативу Thunderbolt . OCuLink версии 2 имеет до 16 ГТ/с ( всего 16 ГБ/с для линий x8), [49] в то время как максимальная пропускная способность соединения Thunderbolt 3 составляет 5 ГБ/с.

В июне 2016 года компании Cadence, PLDA и Synopsys продемонстрировали физический уровень PCIe 4.0, контроллер, коммутатор и другие IP-блоки на ежегодной конференции разработчиков PCI SIG. [71]

Mellanox Technologies анонсировала первый сетевой адаптер 100 Гбит/с с PCIe 4.0 15 июня 2016 года [72] , а первый сетевой адаптер 200 Гбит/с с PCIe 4.0 — 10 ноября 2016 года [73].

В августе 2016 года Synopsys представила тестовую установку с FPGA, тактирующей линию до скоростей PCIe 4.0 на форуме разработчиков Intel . Их IP была лицензирована несколькими фирмами, планирующими представить свои чипы и продукты в конце 2016 года. [74]

На симпозиуме IEEE Hot Chips в августе 2016 года IBM анонсировала первый процессор с поддержкой PCIe 4.0 — POWER9 . [75] [76]

PCI-SIG официально объявила о выпуске окончательной спецификации PCI Express 4.0 8 июня 2017 года. [77] Спецификация включает улучшения в плане гибкости, масштабируемости и пониженного энергопотребления.

5 декабря 2017 года IBM анонсировала первую систему со слотами PCIe 4.0 — Power AC922. [78] [79]

NETINT Technologies представила первый твердотельный накопитель NVMe на базе PCIe 4.0 17 июля 2018 года, в преддверии Flash Memory Summit 2018 [80]

9 января 2019 года AMD объявила, что ее будущие процессоры на базе Zen 2 и чипсет X570 будут поддерживать PCIe 4.0. [81] AMD надеялась включить частичную поддержку старых чипсетов, но нестабильность, вызванная трассировками материнской платы, не соответствующими спецификациям PCIe 4.0, сделала это невозможным. [82] [83]

Intel выпустила свои первые мобильные процессоры с поддержкой PCI Express 4.0 в середине 2020 года как часть микроархитектуры Tiger Lake . [84]

В июне 2017 года PCI-SIG анонсировала предварительную спецификацию PCI Express 5.0. [77] Ожидалось, что пропускная способность увеличится до 32 ГТ/с, что даст 63 ГБ/с в каждом направлении в 16-полосной конфигурации. Ожидалось, что проект спецификации будет стандартизирован в 2019 году. [ необходима цитата ] Первоначально 25,0 ГТ/с также рассматривались для технической осуществимости.

7 июня 2017 года на конференции PCI-SIG DevCon компания Synopsys записала первую демонстрацию PCI Express 5.0 на скорости 32 ГТ/с. [85]

31 мая 2018 года компания PLDA объявила о доступности своего контроллера XpressRICH5 PCIe 5.0 IP на основе проекта 0.7 спецификации PCIe 5.0 в тот же день. [86] [87]

10 декабря 2018 года PCI SIG выпустила версию 0.9 спецификации PCIe 5.0 для своих членов [88] , а 17 января 2019 года PCI SIG объявила, что версия 0.9 была ратифицирована, а версия 1.0 запланирована к выпуску в первом квартале 2019 года [89].

29 мая 2019 года PCI-SIG официально объявила о выпуске финальной спецификации PCI Express 5.0. [90]

20 ноября 2019 года компания Jiangsu Huacun представила первый контроллер PCIe 5.0 HC9001, изготовленный по 12-нм техпроцессу. [91] Производство началось в 2020 году.

17 августа 2020 года IBM анонсировала процессор Power10 с PCIe 5.0 и до 32 полос на однокристальный модуль (SCM) и до 64 полос на двухкристальный модуль (DCM). [92]

9 сентября 2021 года IBM анонсировала сервер Power E1080 Enterprise с запланированной датой выпуска 17 сентября. [93] Он может иметь до 16 модулей Power10 SCM с максимум 32 слотами на систему, которые могут работать как PCIe 5.0 x8 или PCIe 4.0 x16. [94] В качестве альтернативы их можно использовать как слоты PCIe 5.0 x16 для дополнительных оптических адаптеров-преобразователей CXP, подключаемых к внешним отсекам расширения PCIe.

27 октября 2021 года компания Intel анонсировала семейство процессоров Intel Core 12-го поколения — первые в мире потребительские процессоры x86-64 с возможностью подключения PCIe 5.0 (до 16 линий). [95]

22 марта 2022 года компания Nvidia анонсировала графический процессор Nvidia Hopper GH100 — первый в мире графический процессор PCIe 5.0. [96]

23 мая 2022 года AMD анонсировала архитектуру Zen 4 с поддержкой до 24 линий PCIe 5.0 на потребительских платформах и 128 линий на серверных платформах. [97] [98]

18 июня 2019 года PCI-SIG объявила о разработке спецификации PCI Express 6.0. Ожидается, что пропускная способность увеличится до 64 ГТ/с, что составит 128 ГБ/с в каждом направлении в 16-полосной конфигурации, с целевой датой выпуска в 2021 году. [99] Новый стандарт использует 4-уровневую импульсно-амплитудную модуляцию (PAM-4) с малозадерживаемой прямой коррекцией ошибок (FEC) вместо модуляции без возврата к нулю (NRZ). [100] В отличие от предыдущих версий PCI Express, прямая коррекция ошибок используется для повышения целостности данных, а PAM-4 используется в качестве линейного кода, так что за передачу передаются два бита. При скорости передачи данных 64 ГТ/с (сырая скорость передачи данных) в конфигурации x16 возможно до 121 ГБ/с в каждом направлении. [99]

24 февраля 2020 года была выпущена спецификация PCI Express 6.0 версии 0.5 («первый черновик» со всеми определенными архитектурными аспектами и требованиями). [101]

5 ноября 2020 года была выпущена спецификация PCI Express 6.0 версии 0.7 («полный проект» с электрическими характеристиками, проверенными с помощью тестовых чипов). [102]

6 октября 2021 года была выпущена спецификация PCI Express 6.0 версии 0.9 («окончательный черновик»). [103]

11 января 2022 года PCI-SIG официально объявила о выпуске финальной спецификации PCI Express 6.0. [104]

18 марта 2024 года компания Nvidia анонсировала графический процессор Nvidia Blackwell GB100 — первый в мире графический процессор PCIe 6.0. [105]

Кодирование PAM-4 приводит к значительно более высокому коэффициенту битовых ошибок (BER) 10−6 ( по сравнению с 10−12 ранее ), поэтому вместо кодирования 128b/130b используется 3-стороннее чередующееся прямое исправление ошибок (FEC) в дополнение к циклическому избыточному кодированию (CRC). Фиксированный 256-байтовый блок Flow Control Unit (FLIT) переносит 242 байта данных, которые включают пакеты уровня транзакций переменного размера (TLP) и полезную нагрузку канального уровня (DLLP); оставшиеся 14 байт зарезервированы для 8-байтового CRC и 6-байтового FEC. [106] [107] 3-сторонний код Грея используется в режиме PAM-4/FLIT для снижения коэффициента ошибок; интерфейс не переключается на NRZ и кодирование 128/130b даже при переобучении на более низкие скорости передачи данных. [108] [109]

21 июня 2022 года PCI-SIG объявила о разработке спецификации PCI Express 7.0. [110] Она будет обеспечивать сырую скорость передачи данных 128 ГТ/с и до 242 ГБ/с на направление в конфигурации x16, используя ту же сигнализацию PAM4, что и версия 6.0. Удвоение скорости передачи данных будет достигнуто за счет тонкой настройки параметров канала для уменьшения потерь сигнала и повышения энергоэффективности, но ожидается, что целостность сигнала станет проблемой. Ожидается, что спецификация будет завершена в 2025 году.

2 апреля 2024 года PCI-SIG объявила о выпуске спецификации PCIe 7.0 версии 0.5; выпуск PCI Express 7.0 по-прежнему запланирован на 2025 год. [111]

Некоторые поставщики предлагают продукты PCIe по оптоволокну [112] [113] [114] с активными оптическими кабелями (AOC) для коммутации PCIe на увеличенном расстоянии в отсеках расширения PCIe [115] [94] или в особых случаях, когда прозрачное мостовое соединение PCIe предпочтительнее использования более распространенного стандарта (такого как InfiniBand или Ethernet ), для поддержки которого может потребоваться дополнительное программное обеспечение.

Thunderbolt был совместно разработан Intel и Apple как высокоскоростной интерфейс общего назначения, объединяющий логическое соединение PCIe с DisplayPort , и изначально планировался как полностью оптоволоконный интерфейс, но из-за ранних трудностей в создании удобного для потребителя оптоволоконного соединения почти все реализации представляют собой медные системы. Заметным исключением является Sony VAIO Z VPC-Z2, использующий нестандартный порт USB с оптическим компонентом для подключения к внешнему адаптеру дисплея PCIe. Apple была основным драйвером принятия Thunderbolt до 2011 года, хотя несколько других поставщиков [116] анонсировали новые продукты и системы с Thunderbolt. Thunderbolt 3 составляет основу стандарта USB4 .

Спецификация Mobile PCIe (сокращенно M-PCIe ) позволяет архитектуре PCI Express работать поверх технологии физического уровня M-PHY MIPI Alliance . Опираясь на уже существующее широкое распространение M-PHY и его маломощную конструкцию, Mobile PCIe позволяет мобильным устройствам использовать PCI Express. [117]

В спецификации PCI-SIG есть 5 основных выпусков/контрольных точек: [118]

Исторически сложилось так, что самые ранние последователи новой спецификации PCIe обычно начинают проектирование с Draft 0.5, поскольку они могут уверенно выстраивать свою прикладную логику вокруг нового определения пропускной способности и часто даже начинать разработку для любых новых функций протокола. Однако на этапе Draft 0.5 все еще существует высокая вероятность изменений в фактической реализации уровня протокола PCIe, поэтому проектировщики, ответственные за разработку этих блоков внутри компании, могут быть более нерешительными, чтобы начать работу, чем те, кто использует интерфейс IP из внешних источников.

Канал PCIe построен вокруг выделенных однонаправленных пар последовательных (1-битных) соединений типа «точка-точка», известных как линии . Это резко контрастирует с более ранним соединением PCI, которое представляет собой систему на основе шины, где все устройства совместно используют одну и ту же двунаправленную, 32-битную или 64-битную параллельную шину.

PCI Express — это многоуровневый протокол , состоящий из транзакционного уровня , канального уровня и физического уровня . Канальный уровень подразделяется на подуровень управления доступом к среде (MAC). Физический уровень подразделяется на логический и электрический подуровни. Физический логический подуровень содержит физический подуровень кодирования (PCS). Термины заимствованы из модели сетевого протокола IEEE 802 .

Спецификация физического уровня PCIe ( PHY , PCIEPHY , PCI Express PHY или PCIe PHY ) разделена на два подуровня, соответствующих электрическим и логическим спецификациям. Логический подуровень иногда дополнительно делится на подуровень MAC и PCS, хотя это разделение формально не является частью спецификации PCIe. Спецификация, опубликованная Intel, PHY Interface for PCI Express (PIPE), [120] определяет функциональное разделение MAC/PCS и интерфейс между этими двумя подуровнями. Спецификация PIPE также определяет уровень физического подключения носителя (PMA), который включает сериализатор/десериализатор (SerDes) и другие аналоговые схемы; однако, поскольку реализации SerDes сильно различаются у поставщиков ASIC , PIPE не определяет интерфейс между PCS и PMA.

На электрическом уровне каждая полоса состоит из двух однонаправленных дифференциальных пар, работающих на скорости 2,5, 5, 8, 16 или 32 Гбит /с, в зависимости от согласованных возможностей. Передача и прием — это отдельные дифференциальные пары, всего четыре провода данных на полосу.

Соединение между любыми двумя устройствами PCIe называется ссылкой и создается из набора из одной или нескольких полос . Все устройства должны как минимум поддерживать однополосную (x1) связь. Устройства могут опционально поддерживать более широкие связи, состоящие из 32 полос. [121] [122] Это обеспечивает очень хорошую совместимость двумя способами:

В обоих случаях PCIe согласовывает наибольшее взаимно поддерживаемое количество полос. Многие видеокарты, материнские платы и версии BIOS проверены на поддержку подключений x1, x4, x8 и x16 в одном и том же подключении.

Ширина разъема PCIe составляет 8,8 мм, высота — 11,25 мм, а длина может быть переменной. Фиксированная часть разъема имеет длину 11,65 мм и содержит два ряда по 11 контактов в каждом (всего 22 контакта), а длина другой части может быть переменной в зависимости от количества полос. Контакты расположены с интервалом в 1 мм, а толщина карты, входящей в разъем, составляет 1,6 мм. [123] [124]

PCIe отправляет все управляющие сообщения, включая прерывания, по тем же каналам, которые используются для данных. Последовательный протокол никогда не может быть заблокирован, поэтому задержка по-прежнему сопоставима с обычной PCI, которая имеет выделенные линии прерываний. Если принять во внимание проблему совместного использования IRQ прерываний на основе выводов и тот факт, что прерывания, сигнализируемые сообщениями (MSI), могут обходить I/O APIC и доставляться непосредственно в ЦП, производительность MSI оказывается существенно лучше. [125]

Данные, передаваемые по многополосным каналам, чередуются, что означает, что каждый последующий байт отправляется по последовательным каналам. Спецификация PCIe называет это чередование чередованием данных . Требуя значительной аппаратной сложности для синхронизации (или выравнивания ) входящих чередующихся данных, чередование может значительно сократить задержку n -го байта на канале. Хотя каналы не синхронизированы жестко, существует ограничение на перекос между каналами в 20/8/6 нс для 2,5/5/8 ГТ/с, поэтому аппаратные буферы могут повторно выровнять чередующиеся данные. [126] Из-за требований к заполнению чередование не обязательно может сократить задержку небольших пакетов данных на канале.

Как и в других высокоскоростных последовательных протоколах передачи данных, часы встроены в сигнал. На физическом уровне PCI Express 2.0 использует схему кодирования 8b/10b [55] (линейный код), чтобы гарантировать, что строки последовательных идентичных цифр (нулей или единиц) ограничены по длине. Это кодирование использовалось для того, чтобы приемник не терял следа, где находятся края битов. В этой схеме кодирования каждые восемь (некодированных) битов полезной нагрузки данных заменяются 10 (кодированными) битами передаваемых данных, что приводит к 20% накладных расходов в электрической полосе пропускания. Чтобы улучшить доступную полосу пропускания, PCI Express версии 3.0 вместо этого использует кодирование 128b/130b (1,54% накладных расходов). Линейное кодирование ограничивает длину строк идентичных цифр в потоках данных и обеспечивает синхронизацию приемника с передатчиком посредством восстановления тактовой частоты .

Желаемый баланс (и, следовательно, спектральная плотность ) битов 0 и 1 в потоке данных достигается путем применения операции XOR известного двоичного полинома в качестве « скремблера » к потоку данных в топологии обратной связи. Поскольку полином скремблирования известен, данные можно восстановить, применив операцию XOR во второй раз. Оба этапа скремблирования и дескремблирования выполняются на аппаратном уровне.

Двойной симплекс в PCIe означает, что на каждой полосе PCIe есть два симплексных канала. Симплекс означает, что связь возможна только в одном направлении. При наличии двух симплексных каналов возможна двусторонняя связь. Для каждого канала используется одна дифференциальная пара. [127] [128] [129]

Уровень канала передачи данных выполняет три важные функции для канала PCIe:

На стороне передачи уровень канала передачи данных генерирует увеличивающийся порядковый номер для каждого исходящего TLP. Он служит уникальным идентификационным тегом для каждого переданного TLP и вставляется в заголовок исходящего TLP. 32-битный циклический избыточный код проверки (известный в этом контексте как Link CRC или LCRC) также добавляется в конец каждого исходящего TLP.

На стороне приема LCRC и порядковый номер полученного TLP проверяются на уровне канала. Если проверка LCRC не пройдена (что указывает на ошибку данных) или порядковый номер выходит за пределы диапазона (не является последовательным с последним действительным полученным TLP), то плохой TLP, а также любые TLP, полученные после плохого TLP, считаются недействительными и отбрасываются. Получатель отправляет сообщение с отрицательным подтверждением (NAK) с порядковым номером недействительного TLP, запрашивая повторную передачу всех TLP вперед этого порядкового номера. Если полученный TLP проходит проверку LCRC и имеет правильный порядковый номер, он рассматривается как действительный. Получатель канала увеличивает порядковый номер (который отслеживает последний полученный хороший TLP) и пересылает действительный TLP на уровень транзакций получателя. Сообщение ACK отправляется удаленному передатчику, указывая на то, что TLP был успешно получен (и, соответственно, все TLP с прошлыми порядковыми номерами).

Если передатчик получает сообщение NAK или не получает подтверждения (NAK или ACK) до истечения периода тайм-аута, передатчик должен повторно передать все TLP, которые не имеют положительного подтверждения (ACK). За исключением случаев постоянной неисправности устройства или среды передачи, канальный уровень обеспечивает надежное соединение с уровнем транзакций, поскольку протокол передачи обеспечивает доставку TLP через ненадежную среду.

В дополнение к отправке и получению TLP, сгенерированных транзакционным уровнем, канальный уровень также генерирует и потребляет пакеты канального уровня (DLLP). Сигналы ACK и NAK передаются через DLLP, как и некоторые сообщения управления питанием и информация о кредите управления потоком (от имени транзакционного уровня).

На практике количество неподтвержденных TLP в канале ограничено двумя факторами: размером буфера воспроизведения передатчика (который должен хранить копию всех переданных TLP до тех пор, пока удаленный приемник не подтвердит их) и кредитами управления потоком, выданными приемником передатчику. PCI Express требует, чтобы все приемники выдавали минимальное количество кредитов, чтобы гарантировать, что канал позволяет отправлять PCIConfig TLP и сообщения TLP.

PCI Express реализует разделенные транзакции (транзакции с запросом и ответом, разделенными по времени), что позволяет каналу передавать другой трафик, пока целевое устройство собирает данные для ответа.

PCI Express использует управление потоком на основе кредитов. В этой схеме устройство объявляет начальную сумму кредита для каждого полученного буфера на своем уровне транзакций. Устройство на противоположном конце соединения при отправке транзакций на это устройство подсчитывает количество кредитов, которые каждый TLP потребляет со своего счета. Отправляющее устройство может передавать TLP только в том случае, если это не приводит к тому, что его потребленный счет кредитов превышает его кредитный лимит. Когда принимающее устройство заканчивает обработку TLP из своего буфера, оно сигнализирует о возврате кредитов отправляющему устройству, что увеличивает кредитный лимит на восстановленную сумму. Счетчики кредитов являются модульными счетчиками, и сравнение потребленных кредитов с кредитным лимитом требует модульной арифметики . Преимущество этой схемы (по сравнению с другими методами, такими как состояния ожидания или протоколы передачи на основе рукопожатия) заключается в том, что задержка возврата кредита не влияет на производительность, при условии, что кредитный лимит не встречается. Это предположение обычно выполняется, если каждое устройство спроектировано с адекватными размерами буфера.

PCIe 1.x часто цитируется как поддерживающий скорость передачи данных 250 МБ/с в каждом направлении на полосу. Эта цифра является расчетом физической скорости передачи сигналов (2,5 гигабод ), деленной на накладные расходы на кодирование (10 бит на байт). Это означает, что шестнадцатиполосная (x16) карта PCIe теоретически могла бы обеспечить 16x250 МБ/с = 4 ГБ/с в каждом направлении. Хотя это верно с точки зрения байтов данных, более значимые расчеты основаны на скорости полезной нагрузки данных, которая зависит от профиля трафика, который является функцией высокоуровневого (программного) приложения и промежуточных уровней протокола.

Как и другие высокоскоростные последовательные системы соединения, PCIe имеет протокол и накладные расходы на обработку из-за дополнительной надежности передачи (CRC и подтверждения). Длительные непрерывные однонаправленные передачи (например, типичные для высокопроизводительных контроллеров хранения) могут приближаться к >95% от сырой (полосной) скорости передачи данных PCIe. Эти передачи также больше всего выигрывают от увеличенного количества полос (x2, x4 и т. д.). Но в более типичных приложениях (таких как контроллер USB или Ethernet ) профиль трафика характеризуется как короткие пакеты данных с частыми принудительными подтверждениями. [130] Этот тип трафика снижает эффективность канала из-за накладных расходов на анализ пакетов и принудительных прерываний (либо в хост-интерфейсе устройства, либо в ЦП ПК). Будучи протоколом для устройств, подключенных к одной и той же печатной плате , он не требует такой же толерантности к ошибкам передачи, как протокол для связи на больших расстояниях, и, таким образом, эта потеря эффективности не является специфической для PCIe.

Что касается любых «сетевых» каналов связи, часть «сырой» полосы пропускания потребляется накладными расходами протокола: [131]

Например, линия PCIe 1.x обеспечивает скорость передачи данных поверх физического уровня 250 МБ/с (симплекс). Это не пропускная способность полезной нагрузки, а пропускная способность физического уровня — линия PCIe должна переносить дополнительную информацию для полной функциональности. [131]

Накладные расходы Gen2 составляют 20, 24 или 28 байт на транзакцию. [ необходимо разъяснение ] [ необходима цитата ]

Накладные расходы Gen3 составляют 22, 26 или 30 байт на транзакцию. [ необходимо разъяснение ] [ необходима цитата ]

Для полезной нагрузки в 128 байт это 86%, а для полезной нагрузки в 1024 байта это 98%. Для небольших обращений, таких как настройки регистра (4 байта), эффективность падает до 16%. [ необходима цитата ]

Максимальный размер полезной нагрузки (MPS) устанавливается на всех устройствах на основе наименьшего максимума на любом устройстве в цепочке. Если одно устройство имеет MPS 128 байт, все устройства дерева должны установить свои MPS на 128 байт. В этом случае шина будет иметь пиковую эффективность 86% для записи. [131] : 3

PCI Express работает в потребительских, серверных и промышленных приложениях в качестве межсоединения на уровне материнской платы (для соединения периферийных устройств, установленных на материнской плате), пассивного межсоединения объединительной платы и в качестве интерфейса платы расширения для дополнительных плат.

Практически во всех современных (по состоянию на 2012 год [update]) ПК, от потребительских ноутбуков и настольных компьютеров до корпоративных серверов данных, шина PCIe служит основным межсоединением на уровне материнской платы, соединяя хост-систему-процессор как с интегрированными периферийными устройствами (поверхностно-монтируемыми ИС), так и с дополнительными периферийными устройствами (картами расширения). В большинстве этих систем шина PCIe сосуществует с одной или несколькими устаревшими шинами PCI для обратной совместимости с большим количеством устаревших периферийных устройств PCI.

С 2013 года [update]PCI Express заменил AGP в качестве интерфейса по умолчанию для видеокарт в новых системах. Почти все модели видеокарт, выпущенные с 2010 года AMD (ATI) и Nvidia, используют PCI Express. Nvidia использовала высокоскоростную передачу данных PCIe для своей технологии Scalable Link Interface (SLI), которая позволяла нескольким видеокартам с одинаковым набором микросхем и номером модели работать в тандеме, что позволяло повысить производительность. [ необходима цитата ] С тех пор этот интерфейс был прекращен. AMD также разработала многопроцессорную систему на основе PCIe под названием CrossFire . [ необходима цитата ] AMD, Nvidia и Intel выпустили наборы микросхем для материнских плат, которые поддерживают до четырех слотов PCIe x16, что позволяет использовать конфигурации с тремя и четырьмя графическими процессорами.

Теоретически внешний PCIe может дать ноутбуку графическую мощь настольного компьютера, подключив ноутбук к любой видеокарте PCIe для настольного компьютера (заключенной в собственный внешний корпус, с блоком питания и охлаждением); это возможно с интерфейсом ExpressCard или Thunderbolt . Интерфейс ExpressCard обеспечивает скорость передачи данных 5 Гбит/с (пропускная способность 0,5 ГБ/с), тогда как интерфейс Thunderbolt обеспечивает скорость передачи данных до 40 Гбит/с (пропускная способность 5 ГБ/с).

В 2006 году компания Nvidia разработала семейство внешних графических процессоров Quadro Plex PCIe , которые можно использовать для расширенных графических приложений для профессионального рынка. [132] Эти видеокарты требуют слота PCI Express x8 или x16 для карты на стороне хоста, которая подключается к Plex через VHDCI, несущий восемь линий PCIe. [133]

В 2008 году AMD анонсировала технологию ATI XGP , основанную на фирменной кабельной системе, совместимой с передачей сигналов PCIe x8. [134] Этот разъем доступен на ноутбуках Fujitsu Amilo и Acer Ferrari One. Вскоре после этого Fujitsu выпустила корпус AMILO GraphicBooster для XGP. [135] Около 2010 года Acer выпустила графическую док-станцию Dynavivid для XGP. [136]

В 2010 году были представлены внешние концентраторы карт, которые можно подключать к ноутбуку или настольному компьютеру через слот PCI ExpressCard. Эти концентраторы могут принимать полноразмерные видеокарты. Примерами служат MSI GUS, [137] ViDock от Village Instrument, [138] Asus XG Station , адаптер Bplus PE4H V3.2, [139], а также более импровизированные устройства DIY. [140] Однако такие решения ограничены размером (часто только x1) и версией доступного слота PCIe на ноутбуке.

Интерфейс Intel Thunderbolt предоставил новую возможность подключения к внешней карте PCIe. Magma выпустила ExpressBox 3T, который может вмещать до трех карт PCIe (две в формате x8 и одну в формате x4). [141] MSI также выпустила Thunderbolt GUS II, шасси PCIe, предназначенное для видеокарт. [142] Другие продукты, такие как Echo Express от Sonnet [143] и mLink от mLogic, представляют собой шасси Thunderbolt PCIe в меньшем форм-факторе. [144]

В 2017 году были представлены более полнофункциональные внешние концентраторы карт, такие как Razer Core, имеющий полноразмерный интерфейс PCIe x16. [145]

Протокол PCI Express может использоваться в качестве интерфейса передачи данных для устройств флэш-памяти , таких как карты памяти и твердотельные накопители (SSD).

Карта XQD — это формат карты памяти, использующий PCI Express, разработанный ассоциацией CompactFlash, со скоростью передачи данных до 1 ГБ/с. [146]

Многие высокопроизводительные твердотельные накопители корпоративного класса разработаны как карты контроллеров PCI Express RAID . [ необходима цитата ] До того, как NVMe был стандартизирован, многие из этих карт использовали фирменные интерфейсы и специальные драйверы для взаимодействия с операционной системой; они имели гораздо более высокую скорость передачи данных (более 1 ГБ/с) и IOPS (более миллиона операций ввода-вывода в секунду) по сравнению с дисками Serial ATA или SAS . [ количественно ] [147] [148] Например, в 2011 году OCZ и Marvell совместно разработали собственный контроллер твердотельного накопителя PCI Express для слота PCI Express 3.0 x16 с максимальной емкостью 12 ТБ и производительностью до 7,2 ГБ/с при последовательных передачах и до 2,52 миллиона IOPS при случайных передачах. [149] [ актуально? ]

SATA Express был интерфейсом для подключения SSD через порты, совместимые с SATA, опционально предоставляя несколько линий PCI Express в качестве чистого соединения PCI Express с подключенным устройством хранения данных. [150] M.2 — это спецификация для внутренних карт расширения компьютера и связанных с ними разъемов, которая также использует несколько линий PCI Express. [151]

Устройства хранения PCI Express могут реализовывать как логический интерфейс AHCI для обратной совместимости, так и логический интерфейс NVM Express для гораздо более быстрых операций ввода-вывода, обеспечиваемых за счет использования внутреннего параллелизма, предлагаемого такими устройствами. SSD-накопители корпоративного класса также могут реализовывать SCSI через PCI Express . [152]

Некоторые приложения центров обработки данных (например, большие компьютерные кластеры ) требуют использования оптоволоконных соединений из-за ограничений расстояния, присущих медным кабелям. Обычно для этих приложений достаточно сетевого стандарта, такого как Ethernet или Fibre Channel , но в некоторых случаях накладные расходы, вносимые маршрутизируемыми протоколами, нежелательны, и требуется соединение более низкого уровня, такое как InfiniBand , RapidIO или NUMAlink . Стандарты локальной шины, такие как PCIe и HyperTransport, в принципе, могут использоваться для этой цели, [153] но по состоянию на 2015 год [update]решения доступны только от нишевых поставщиков, таких как Dolphin ICS и TTTech Auto.

Другие стандарты связи, основанные на последовательной архитектуре с высокой пропускной способностью, включают InfiniBand , RapidIO , HyperTransport , Intel QuickPath Interconnect , Mobile Industry Processor Interface (MIPI) и NVLink . Различия основаны на компромиссах между гибкостью и расширяемостью по сравнению с задержкой и накладными расходами. Например, для обеспечения возможности горячего подключения системы, как в случае с Infiniband, но не с PCI Express, требуется, чтобы программное обеспечение отслеживало изменения топологии сети. [ необходима цитата ]

Другой пример — сокращение пакетов для уменьшения задержки (что требуется, если шина должна работать как интерфейс памяти). Более мелкие пакеты означают, что заголовки пакетов занимают больший процент пакета, тем самым уменьшая эффективную пропускную способность. Примерами протоколов шины, разработанных для этой цели, являются RapidIO и HyperTransport. [ необходима цитата ]

PCI Express находится где-то посередине, [ необходимо уточнение ] предназначенный по замыслу как системное соединение ( локальная шина ), а не как межсоединение устройств или маршрутизируемый сетевой протокол. Кроме того, его цель по разработке прозрачности программного обеспечения ограничивает протокол и несколько увеличивает его задержку. [ необходимо цитирование ]

Задержки в реализации PCIe 4.0 привели к тому, что к концу 2016 года были анонсированы консорциум Gen-Z , проект CCIX и открытый интерфейс когерентного ускорителя процессора (CAPI) . [154]

11 марта 2019 года Intel представила Compute Express Link (CXL) , новую соединительную шину, основанную на инфраструктуре физического уровня PCI Express 5.0. Первоначальными промоутерами спецификации CXL были: Alibaba , Cisco , Dell EMC , Facebook , Google , HPE , Huawei , Intel и Microsoft . [155]

Список интеграторов PCI-SIG содержит продукты, произведенные компаниями-членами PCI-SIG, которые прошли тестирование на соответствие. Список включает коммутаторы, мосты, сетевые карты, твердотельные накопители и т. д. [156]

{{cite web}}: CS1 maint: numeric names: authors list (link)Этот ECN определяет кодировки типа разъема для нового разъема 12V-2x6. Этот разъем, определенный в CEM 5.1, заменяет разъем 12VHPWR.