В архитектуре компьютера кэш трассировки или кэш трассировки выполнения — это специализированный кэш инструкций , который хранит динамический поток инструкций , известный как трассировка . Он помогает увеличить пропускную способность выборки инструкций и снизить энергопотребление (в случае Intel Pentium 4 ) за счет хранения трассировок инструкций, которые уже были извлечены и декодированы. [1] Процессор трассировки [2] — это архитектура, разработанная вокруг кэша трассировки и обрабатывающая инструкции на гранулярности уровня трассировки. Формальная математическая теория трассировок описывается моноидами трассировки .

Самая ранняя академическая публикация о кэше трассировки была "Trace Cache: a Low Latency Approach to High Bandwidth Instruction Fetching". [1] Эта широко известная работа была представлена Эриком Ротенбергом, Стивом Беннеттом и Джимом Смитом на конференции International Symposium on Microarchitecture (MICRO) 1996 года. Более ранняя публикация - патент США 5381533, [3] Алекса Пелега и Ури Вайзера из Intel, "Dynamic flow instructions cache memory, organization around trace segments independent of virtual address line", продолжение заявки, поданной в 1992 году, позже отклоненной.

Более широкие суперскалярные процессоры требуют, чтобы несколько инструкций были извлечены в одном цикле для более высокой производительности. Инструкции, которые должны быть извлечены, не всегда находятся в смежных ячейках памяти ( базовых блоках ) из-за инструкций ветвления и перехода . Поэтому процессорам нужна дополнительная логика и аппаратная поддержка для извлечения и выравнивания таких инструкций из несмежных базовых блоков. Если несколько ветвей предсказаны как не-принятые , то процессоры могут извлекать инструкции из нескольких смежных базовых блоков в одном цикле. Однако, если какая-либо из ветвей предсказана как принятая , то процессор должен извлекать инструкции из принятого пути в том же цикле. Это ограничивает возможности извлечения процессора.

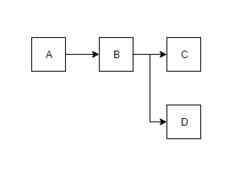

Рассмотрим эти четыре базовых блока ( A, B, C, D), показанные на рисунке, которые соответствуют простому циклу if-else . Эти блоки будут храниться смежно , как ABCDв памяти. Если ветвь Dпредсказана как непринятая, блок выборки может извлечь базовые блоки A, B, Cкоторые размещены смежно. Однако, если Dпредсказано как принятое , блок выборки должен извлечь A, B, Dкоторые размещены несмежно. Следовательно, извлечение этих блоков, которые размещены несмежно, за один цикл будет очень сложным. Поэтому в таких ситуациях на помощь процессору приходит кэш трассировки.

После извлечения кэш трассировки сохраняет инструкции в их динамической последовательности. Когда эти инструкции встречаются снова, кэш трассировки позволяет блоку извлечения инструкций процессора извлекать из него несколько базовых блоков, не беспокоясь о ветвлениях в потоке выполнения. Инструкции будут сохраняться в кэше трассировки либо после того, как они были декодированы, либо по мере их удаления. Однако последовательность инструкций является спекулятивной, если они сохраняются сразу после стадии декодирования.

Трассировка, также называемая динамической последовательностью инструкций, представляет собой запись в кэше трассировки. Она может быть охарактеризована максимальным числом инструкций и максимальным количеством базовых блоков . Трассировки могут начинаться с любой динамической инструкции. Несколько трассировок могут иметь одну и ту же начальную инструкцию, т. е. один и тот же начальный счетчик программ (PC) и инструкции из разных базовых блоков в соответствии с результатами ветвления. Для рисунка выше ABC и ABD являются допустимыми трассировками. Они обе начинаются с одного и того же PC (адрес A) и имеют разные базовые блоки в соответствии с предсказанием D.

Трассировки обычно прекращаются, когда происходит одно из следующих событий:

Отдельный след будет содержать следующую информацию:

Ниже приведены факторы, которые необходимо учитывать при проектировании кэша трассировки.

Кэш трассировки не находится на критическом пути выборки инструкций [4]

Строки трассировки хранятся в кэше трассировки на основе PC первой инструкции в трассировке и набора предсказаний ветвлений. Это позволяет хранить различные пути трассировки, которые начинаются с одного и того же адреса, каждый из которых представляет различные результаты ветвления. Этот метод тегирования помогает обеспечить ассоциативность пути с кэшем трассировки. Другой метод может включать наличие только начального PC в качестве тега в кэше трассировки. На этапе выборки инструкций конвейера текущий PC вместе с набором предсказаний ветвлений проверяется в кэше трассировки на наличие попадания . Если есть попадание, то в блок выборки подается строка трассировки, которая не должна идти в обычный кэш или в память для этих инструкций. Кэш трассировки продолжает подавать данные в блок выборки до тех пор, пока строка трассировки не закончится или пока в конвейере не возникнет неправильное предсказание . Если есть пропуск, то начинает строиться новая трассировка.

Кэш трассировки выполнения Pentium 4 хранит микрооперации , полученные в результате декодирования инструкций x86 , предоставляя также функциональность кэша микроопераций. Имея это, в следующий раз, когда инструкция понадобится, ее не придется снова декодировать в микрооперации. [5]

Недостатки кэширования трассировки:

В кэш L1 процессоров NetBurst компания Intel включила свой кэш трассировки выполнения. [7] [8] Он хранит декодированные микрооперации , так что при выполнении новой инструкции вместо повторной выборки и декодирования инструкции процессор напрямую обращается к декодированным микрооперациям из кэша трассировки, тем самым экономя значительное время. Более того, микрооперации кэшируются в их прогнозируемом пути выполнения, что означает, что когда инструкции извлекаются процессором из кэша, они уже присутствуют в правильном порядке выполнения. Позже Intel представила похожую, но более простую концепцию с Sandy Bridge, называемую кэшем микроопераций (кешем UOP).