Intel 5 Series — это вычислительная архитектура, представленная в 2008 году, которая повышает эффективность и балансирует использование каналов связи на материнской плате . Архитектура в основном состоит из центрального процессора (ЦП) (подключенного к графической карте и памяти) и одного чипсета (подключенного к компонентам материнской платы). Все коммуникации и действия материнской платы вращаются вокруг этих двух устройств.

Архитектура является результатом изменений, внесенных в Intel 4 Series для обеспечения более высокой производительности материнских плат при сохранении эффективности и низкого энергопотребления. Изменения касаются дизайна чипсета и процессора в сочетании с перераспределением функций и контроллеров. Результатом стало первое крупное изменение за многие годы вычислений.

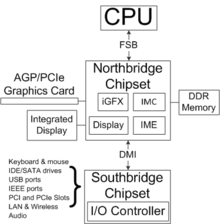

Концепция архитектуры заключалась в улучшении механики материнской платы, чтобы она не отставала от ЦП по мере того, как он набирал скорость и увеличивал количество ядер. В предыдущей архитектуре ЦП активно взаимодействовал с центральным компонентом материнской платы, чипсетом северного моста , поскольку он был посредником между ЦП, памятью и, в большинстве случаев, графической картой. ЦП взаимодействовал с чипсетом северного моста, когда ему требовались данные из памяти или когда ему требовалось вывести графику на дисплей. Такая компоновка приводила к интенсивному использованию канала связи, известного как передняя шина (FSB). Прошло совсем немного времени, прежде чем либо FSB достигла полной мощности, либо работала неэффективно с большим количеством ядер. С перемещением контроллера памяти и/или графического ядра в процессор зависимость отдельных чипсетов материнской платы для этих функций снизилась.

Чипсет Ibex Peak включает в себя только Platform Controller Hub (PCH) на модель, который обеспечивает периферийные соединения и контроллеры отображения для ЦП со встроенной графикой через Flexible Display Interface (кроме моделей P). Кроме того, PCH подключается к ЦП через Direct Media Interface (DMI).

Используя преимущества процессоров Nehalem с интегрированной графикой и портами PCI Express , Intel Management Engine (ME) и контроллер дисплея для интегрированной графики, ранее размещавшиеся в северном мосту, перемещены в Platform Controller Hub (PCH). Функция I/O Controller Hub (ICH) интегрирована в PCH, что устраняет необходимость в отдельных северном и южном мостах .

Семейство чипсетов Tylersburg предназначено для Socket LGA 1366 , поддерживающего процессоры с трехканальными контроллерами памяти. В отличие от чипсетов Ibex Peak , семейство чипсетов Tylersburg не включает PCH, а концентратор ввода-вывода в основном обеспечивает дополнительные порты PCI Express 2.0. Периферийные соединения обеспечиваются концентратором контроллера ввода-вывода (ICH), подключенным к интерфейсу DMI. Intel 5 series IOH поддерживает ICH10, в то время как Intel 5500 Series IOH поддерживает ICH9 или ICH10.

Xeon на базе Nehalem для двухсокетных систем, изначально выпущенных как серия Xeon 55xx, имеют совершенно иную структуру системы: контроллеры памяти находятся на ЦП, а ЦП могут взаимодействовать друг с другом как одноранговые узлы без использования чипсета. Это означает, что чипсеты 5500 и 5520 (первоначальное кодовое название Tylersburg-EP) по сути являются интерфейсами QPI to PCI Express ; 5520 больше предназначен для графических рабочих станций, а 5500 — для серверов, которым не требуется большое количество подключений PCI Express