В производстве полупроводников процесс «7 нм» — это термин для узла технологии MOSFET , следующего за узлом «10 нм» , определенного Международной дорожной картой для приборов и систем (IRDS), которой предшествовала Международная технологическая дорожная карта для полупроводников (ITRS). Он основан на технологии FinFET (fin field-effect transistor), типе технологии многозатворных MOSFET .

По состоянию на 2021 год стандарт литографии IRDS дает таблицу размеров для узла «7 нм» [1] с примерами, приведенными ниже:

Стандарт литографии IRDS 2021 года является ретроспективным документом, поскольку первое массовое производство фирменного процесса «7 нм» было начато в 2016 году компанией Taiwan Semiconductor Manufacturing Company ( TSMC ) с выпуском 256-мегабитных чипов памяти SRAM с использованием процесса «7 нм » под названием N7. [2] Samsung начала массовое производство своих устройств по процессу «7 нм» (7LPP) в 2018 году. [3] Эти технологические узлы имели такую же приблизительную плотность транзисторов , как и узел Intel « 10 нм Enhanced Superfin », позже переименованный в «Intel 7» . [4]

Начиная по крайней мере с 1997 года шкала длины узла процесса не ссылалась ни на какое конкретное измерение на интегральных схемах, например, на длину затвора, шаг металла или шаг затвора, поскольку новые литографические процессы больше не уменьшали равномерно все элементы на чипе. К концу 2010-х годов шкала длины стала коммерческим названием [5] , которое указывало на новое поколение технологических процессов, без какой-либо связи с физическими свойствами. [6] [7] [8] Предыдущие стандарты ITRS и IRDS не содержали достаточных указаний по соглашениям об именовании узлов процесса для учета сильно различающихся размеров на чипе, что приводило к расхождению между тем, как литейные заводы называли свою литографию, и фактическими размерами, которых достигали их узлы процесса.

Первый массовый мобильный процессор «7 нм», предназначенный для использования на массовом рынке, Apple A12 Bionic , был анонсирован на мероприятии Apple в сентябре 2018 года . [9] Хотя Huawei анонсировала свой собственный процессор «7 нм» до Apple A12 Bionic, Kirin 980 31 августа 2018 года, Apple A12 Bionic был выпущен для публичного использования на массовом рынке потребителями до Kirin 980. Оба чипа были произведены TSMC. [10]

В 2019 году [11] AMD выпустила свои процессоры « Rome » (EPYC 2) для серверов и центров обработки данных, которые основаны на узле N7 компании TSMC [12] и имеют до 64 ядер и 128 потоков. Они также выпустили свои потребительские настольные процессоры « Matisse » с 16 ядрами и 32 потоками. Однако кристалл ввода-вывода на многочиповом модуле Rome (MCM) изготовлен с использованием 14-нм (14HP) процесса GlobalFoundries , в то время как кристалл ввода-вывода Matisse использует 12-нм (12LP+) процесс GlobalFoundries . Серия Radeon RX 5000 также основана на процессе N7 компании TSMC.

В начале 2000-х годов исследователи начали демонстрировать 7-нм МОП-транзисторы , а команда IBM, в которую входили Брюс Дорис, Омер Докумачи, Мейкей Ионг и Анда Мокута, успешно изготовила 6-нм МОП-транзистор на основе кремния на изоляторе (SOI). [13] [14] Вскоре после этого, в 2003 году, исследователи из NEC Хитоши Вакабаяши и Шигехару Ямагами продвинулись дальше, изготовив 5-нм МОП-транзистор. [15] [16]

В июле 2015 года IBM объявила, что создала первые функциональные транзисторы с технологией «7 нм», используя кремний-германиевый процесс. [17] [18] [19] [20] С дальнейшим развитием в феврале 2017 года TSMC произвела ячейки памяти SRAM емкостью 256 Мбит с использованием своего «7 нм» процесса, с площадью ячейки 0,027 квадратных микрометров , [21] что дает минимальный размер квадратного элемента:

Накопленный в TSMC начальный объем этого 7-нм производства в 2018 году. [2]

В 2015 году Intel ожидала, что на 7-нм технологическом процессе в транзисторах придется использовать полупроводники III-V групп, что станет сигналом к отходу от кремния. [22]

В апреле 2016 года TSMC объявила, что пробное производство «7 нм» начнется в первой половине 2017 года. [23] В апреле 2017 года TSMC начала рискованное производство 256-мегабитных чипов памяти SRAM с использованием процесса «7 нм» (N7FF+) [2] с литографией в экстремальном ультрафиолете (EUV). [24] Планы производства «7 нм» TSMC по состоянию на начало 2017 года [ требуется обновление ] заключались в использовании иммерсионной литографии в глубоком ультрафиолете (DUV) изначально на этом технологическом узле (N7FF) и переходе от рискового к коммерческому массовому производству со второго квартала 2017 года по второй квартал 2018 года. Кроме того, их более позднее поколение производства «7 нм» (N7FF+) было запланировано [ требуется обновление ] для использования множественного шаблонирования EUV и предполагаемого перехода от рискового к массовому производству между 2018 и 2019 годами. [25]

В сентябре 2016 года компания GlobalFoundries объявила о начале пробного производства во второй половине 2017 года и рискованном производстве в начале 2018 года, при этом тестовые чипы уже запущены. [26]

В феврале 2017 года Intel анонсировала Fab 42 в Чандлере, штат Аризона , который, согласно пресс-релизам того времени, должен был [ требуется обновление ] производить микропроцессоры с использованием производственного процесса «7 нм» (Intel 4 [27] ). [28] На тот момент компания не опубликовала никаких ожидаемых значений длин элементов на этом технологическом узле. [ требуется обновление ]

В апреле 2018 года TSMC объявила о массовом производстве чипов «7 нм» (CLN7FF, N7). В июне 2018 года компания объявила о наращивании массового производства. [3]

В мае 2018 года Samsung объявила о производстве чипов «7 нм» (7LPP) в этом году. ASML Holding NV является их основным поставщиком машин EUV-литографии. [29]

В августе 2018 года компания GlobalFoundries объявила о прекращении разработки чипов «7 нм» из-за их стоимости. [30]

28 октября 2018 года компания Samsung объявила, что ее второе поколение технологического процесса «7 нм» (7LPP) вошло в стадию рискованного производства и, как на тот момент ожидалось, выйдет в массовое производство к 2019 году. [ требуется обновление ]

17 января 2019 года в рамках отчета о доходах за четвертый квартал 2018 года компания TSMC упомянула, что разные клиенты будут иметь «разные вкусы» второго поколения «7 нм». [31] [ требуется обновление ]

16 апреля 2019 года компания TSMC анонсировала свой «6-нм» процесс под названием (CLN6FF, N6), который, согласно пресс-релизу от 16 апреля 2019 года, на тот момент должен был появиться в массовых продуктах с 2021 года. [32] [ требуется обновление ] На тот момент ожидалось, что N6 будет использовать EUVL в 5 слоях по сравнению с 4 слоями в их процессе N7+. [33]

28 июля 2019 года TSMC анонсировала свой второй процесс "7 нм" под названием N7P, который, как и их процесс N7, должен был быть основан на DUV. [34] Поскольку N7P был полностью совместим по IP с оригинальным "7 нм", в то время как N7+ (который использует EUV) не был, N7+ (анонсированный ранее как "7 нм+") должен был стать отдельным от "7 нм" процессом. N6 ("6 нм"), еще один процесс на основе EUV, в то время планировалось выпустить позже, чем даже процесс TSMC "5 нм" (N5), с совместимостью по IP с N7. В своем отчете о доходах за первый квартал 2019 года TSMC повторила свое заявление за четвертый квартал 2018 года [31] , что на тот момент ожидалось, что N7+ принесет менее 1 миллиарда тайваньских долларов дохода в 2019 году. [35] [ требуется обновление ]

5 октября 2019 года AMD анонсировала свою дорожную карту EPYC , включающую чипы Milan, созданные с использованием процесса TSMC N7+. [36] [ требуется обновление ]

7 октября 2019 года компания TSMC объявила о начале поставок продукции N7+ на рынок в больших объемах. [37] [ требуется обновление ]

26 июля 2021 года Intel объявила о своей новой дорожной карте производства, переименовав все свои будущие технологические узлы. [27] «10-нм» Enhanced SuperFin (10ESF) от Intel, который был примерно эквивалентен процессу N7 от TSMC, с этого момента будет называться «Intel 7», в то время как их более ранний «7-нм» процесс раньше назывался «Intel 4». [27] [38] В результате первые процессоры Intel на базе Intel 7 в то время планировалось начать поставлять ко второй половине 2022 года, [ нужно обновление ] тогда как Intel ранее объявляла, что планирует выпустить «7-нм» процессоры в 2023 году. [39] [ нужно обновление ]

В июне 2018 года AMD объявила о запуске 7-нм графических процессоров Radeon Instinct во второй половине 2018 года. [40] В августе 2018 года компания подтвердила выпуск графических процессоров. [41]

21 августа 2018 года компания Huawei объявила о том, что чипсет HiSilicon Kirin 980 будет использоваться в смартфонах Huawei Mate 20 и Mate 20 Pro, изготовленных по 7-нм техпроцессу (N7) компании TSMC. [ требуется обновление ]

12 сентября 2018 года Apple анонсировала чип A12 Bionic , используемый в iPhone XS и iPhone XR, созданный с использованием 7-нм (N7) процесса TSMC. Процессор A12 стал первым 7-нм чипом для массового рынка, поскольку он был выпущен до Huawei Mate 20. [42] [43] 30 октября 2018 года Apple анонсировала чип A12X Bionic , используемый в iPad Pro, созданный с использованием 7-нм (N7) процесса TSMC. [44]

4 декабря 2018 года Qualcomm анонсировала свои Snapdragon 855 и 8cx, созданные с использованием 7-нм (N7) процесса TSMC. [45] Первым массовым продуктом с Snapdragon 855 стал Lenovo Z5 Pro GT, анонсированный 18 декабря 2018 года. [46]

29 мая 2019 года компания MediaTek анонсировала свою 5G SoC, созданную с использованием 7-нм техпроцесса TSMC. [47]

7 июля 2019 года компания AMD официально представила серию центральных процессоров Ryzen 3000, созданных на базе 7-нм техпроцесса TSMC и микроархитектуры Zen 2 .

6 августа 2019 года Samsung анонсировала свой Exynos 9825 SoC, первый чип, созданный с использованием их процесса 7LPP. Exynos 9825 — первый чип для массового рынка, созданный с использованием EUVL . [48]

6 сентября 2019 года компания Huawei анонсировала свои чипсеты HiSilicon Kirin 990 4G и 990 5G , созданные с использованием процессов TSMC N7 и N7+. [49]

10 сентября 2019 года Apple анонсировала чип A13 Bionic , используемый в iPhone 11 и iPhone 11 Pro, созданный с использованием процесса TSMC N7P второго поколения. [50]

Производство 7 нм (узлы N7) составило 36% выручки TSMC во втором квартале 2020 года. [51]

17 августа 2020 года IBM анонсировала свой процессор Power10 . [50]

26 июля 2021 года Intel объявила, что ее процессоры Alder Lake будут производиться с использованием их нового ребрендированного процесса «Intel 7», ранее известного как «10nm Enhanced SuperFin». [27] В то время, согласно пресс-релизам, ожидалось, что эти процессоры будут выпущены во второй половине 2021 года. [ требуется обновление ] Ранее компания подтвердила, что 7-нм семейство микропроцессоров, теперь называемое «Intel 4», [27] под названием Meteor Lake будет выпущено в 2023 году. [52] [53] [ требуется обновление ]

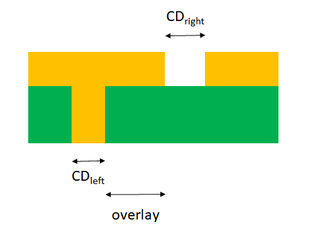

Ожидается, что узел литейного производства «7 нм» будет использовать любую из или комбинацию следующих технологий формирования шаблонов: расщепление шага , самосовмещенное формирование шаблонов и литография EUV . Каждая из этих технологий несет в себе значительные проблемы в контроле критических размеров (CD), а также в размещении шаблонов, все из которых затрагивают соседние элементы.

Разделение шага подразумевает разделение слишком близко расположенных друг к другу элементов на разные маски, которые экспонируются последовательно, а затем подвергаются обработке литографическим травлением. Из-за использования разных экспозиций всегда существует риск ошибки наложения между двумя экспозициями, а также разных компакт-дисков, возникающих из-за разных экспозиций.

Формирование шаблона проставки включает в себя нанесение слоя на предварительно сформированные элементы, а затем обратное травление для формирования прокладок на боковых стенках этих элементов, называемых основными элементами. После удаления основных элементов проставки используются в качестве маски травления для определения канавок в нижележащем слое. Хотя контроль CD проставки, как правило, превосходен, CD траншеи может попасть в одну из двух популяций из-за двух возможностей расположения там, где была расположена основная деталь, или в оставшемся зазоре. Это известно как «шаг шага». [54] Как правило, шаг = CD ядра + CD зазора + 2 * CD проставки, но это не гарантирует, что CD ядра = CD зазора. Для элементов FEOL , таких как изоляция затвора или активной области (например, ребра), CD траншеи не так критичен, как CD, определяемый проставкой, и в этом случае формирование шаблона проставки фактически является предпочтительным подходом к формированию шаблона.

При использовании самовыравнивающегося четверного паттерна (SAQP) используется второй спейсер, который заменяет первый. В этом случае основной CD заменяется основным CD - 2* 2-й спейсерный CD, а зазорный CD заменяется зазорным CD - 2 * 2-й спейсерный CD. Таким образом, некоторые размеры элементов строго определяются вторым спейсерным CD, в то время как остальные размеры элементов определяются основным CD, шагом сердечника и первым и вторым спейсерными CD. Основной CD и шаг сердечника определяются обычной литографией, в то время как спейсерные CD не зависят от литографии. На самом деле ожидается, что это будет иметь меньше вариаций, чем разделение шага, где дополнительная экспозиция определяет свой собственный CD, как напрямую, так и через наложение.

Линии, определенные спейсером, также требуют резки. Места резки могут смещаться при экспонировании, что приводит к искажению концов линий или вторжениям в соседние линии.

Для создания шаблонов BEOL «7 нм» была реализована технология самовыравнивающегося литографического травления-литографического травления (SALELE). [55]

Литография в экстремальном ультрафиолете (также известная как EUV или EUVL ) способна разрешать элементы размером менее 20 нм в обычном стиле литографии. Однако трехмерная отражательная природа маски EUV приводит к новым аномалиям в изображении. Одной из особых неприятностей является эффект двух полос, когда пара идентичных полосовых элементов не фокусируется одинаково. Один элемент по сути находится в «тени» другого. Следовательно, два элемента обычно имеют разные CD, которые изменяются через фокус, и эти элементы также меняют положение через фокус. [56] [57] [58] Этот эффект может быть похож на тот, который можно встретить при разделении шага. Связанная с этим проблема заключается в разнице наилучшего фокуса между элементами с разным шагом. [59]

EUV также имеет проблемы с надежной печатью всех признаков в большой популяции; некоторые контакты могут полностью отсутствовать или линии могут быть перекрыты. Это известно как стохастические сбои печати. [60] [61] Уровень дефекта составляет порядка 1К/мм 2 . [62]

Зазор между кончиками трудно контролировать для EUV, в основном из-за ограничений освещения. [63] Предпочтительнее использовать отдельную экспозицию(и) для линий разреза.

Маски с ослабленным фазовым сдвигом использовались в производстве для узла 90 нм для адекватных окон фокусировки для произвольно расположенных контактов с длиной волны лазера ArF (193 нм), [64] [65] , тогда как это улучшение разрешения недоступно для EUV. [66] [67]

На конференции SPIE 2021 года по EUV-литографии клиент TSMC сообщил, что выход EUV-контакта сопоставим с выходом иммерсионного мультишаблона. [68]

Из-за этих проблем «7 нм» создает беспрецедентную сложность шаблонизации в задней части линии (BEOL). Предыдущий крупносерийный, долгоживущий литейный узел (Samsung «10 нм», TSMC «16 нм») использовал разделение шага для более плотных металлических слоев. [69] [70] [71]

Поскольку инструменты иммерсии в настоящее время стали быстрее, мультипаттернинг по-прежнему используется на большинстве слоев. На слоях, требующих иммерсионного квадро-паттернинга, пропускная способность завершения слоя с помощью EUV сопоставима. На других слоях иммерсия была бы более производительной при завершении слоя даже с мультипаттернингом.

Металлический рисунок «7 нм», который в настоящее время практикуется TSMC, включает линии самовыравнивающегося двойного рисунка (SADP) с надрезами, вставленными в ячейку на отдельной маске по мере необходимости для уменьшения высоты ячейки. [74] Однако самовыравнивающийся четырехугольный рисунок (SAQP) используется для формирования ребра, самого важного фактора для производительности. [75] Проверки правил проектирования также позволяют избегать многослойного рисунка и обеспечивают достаточные зазоры для надрезов, так что требуется только одна маска надреза. [75]

Наименование узлов процесса четырьмя различными производителями (TSMC, Samsung, SMIC , Intel) частично обусловлено маркетинговыми соображениями и не связано напрямую с каким-либо измеримым расстоянием на чипе — например, узел TSMC «7 нм» ранее был похож по некоторым ключевым параметрам на запланированный Intel узел первой итерации «10 нм», прежде чем Intel выпустила дальнейшие итерации, завершившиеся «10 нм Enhanced SuperFin», который позже был переименован в «Intel 7» по маркетинговым причинам. [76] [77]

Поскольку реализация EUV на уровне "7 нм" все еще ограничена, многошаблонность все еще играет важную роль в стоимости и выходе; EUV добавляет дополнительные соображения. Разрешение для большинства критических слоев все еще определяется многошаблонностью. Например, для "7 нм" Samsung, даже с EUV одинарными слоями шага 36 нм, слои шага 44 нм все еще будут иметь четырехшаблонную структуру. [78]

Процесс GlobalFoundries «7 нм» 7LP (Leading Performance) мог бы предложить на 40% более высокую производительность или на 60% более низкую мощность с 2-кратным масштабированием плотности и на 30-45% более низкой стоимостью за кристалл по сравнению с его «14 нм» процессом. Контактный шаг поли (CPP) был бы 56 нм, а минимальный шаг металла (MMP) был бы 40 нм, произведенный с помощью самовыравнивающегося двойного шаблона (SADP). Ячейка SRAM 6T имела бы размер 0,269 квадратных микрон. GlobalFoundries планировала в конечном итоге использовать литографию EUV в улучшенном процессе под названием 7LP+. [100] Позже GlobalFoundries прекратила все разработки «7 нм» и более поздних процессов. [101]

Новый процесс Intel "Intel 7", ранее известный как "10nm Enhanced SuperFin" (10ESF), основан на его предыдущем узле "10nm". Узел будет отличаться 10-15% увеличением производительности на ватт . Между тем, их старый процесс "7nm", теперь называемый "Intel 4", в то время должен был быть выпущен в 2023 году. [102] [ требуется обновление ] В то время было обнародовано немного подробностей об узле "Intel 4", хотя в то время его плотность транзисторов оценивалась как минимум в 202 миллиона транзисторов на квадратный миллиметр. [27] [103] [ требуется обновление ] По состоянию на 2020 год Intel испытывала проблемы со своим процессом "Intel 4" вплоть до аутсорсинга производства своих графических процессоров Ponte Vecchio. [104] [105] [ требуется обновление ]