Микросхема программируемого периферийного интерфейса (PPI) Intel 8255 (или i8255 ) была разработана и произведена компанией Intel в первой половине 1970-х годов для микропроцессора Intel 8080. 8255 обеспечивает 24 параллельные линии ввода/вывода с различными программируемыми режимами работы.

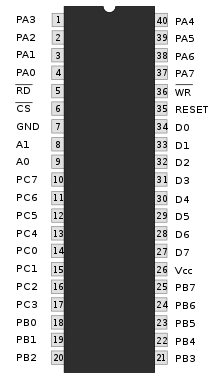

8255 является членом семейства микросхем MCS-85 , разработанных Intel для использования с микропроцессорами 8085 и 8086 и их потомками. [1] Сначала он был доступен в 40-контактном DIP- корпусе , а затем в 44-контактном PLCC- корпусе. [2] Он нашел широкое применение в цифровых системах обработки данных и позже был клонирован другими производителями. 82C55 — это версия CMOS для более высокой скорости и меньшего потребления тока.

Функциональность 8255 в настоящее время в основном встроена в более крупные микросхемы обработки VLSI в качестве подфункции. Версия CMOS 8255 все еще производится [3] компанией Renesas, но в основном используется для расширения ввода-вывода микроконтроллеров .

8255 имеет функцию, аналогичную Motorola 6820 PIA (Peripheral Interface Adapter) из семейства Motorola 6800 , также изначально упакованную как 40-контактный DIL. 8255 обеспечивает 24 контакта ввода-вывода с четырьмя программируемыми битами направления: один для порта A (7:0) (т. е. все контакты в порту), один для порта B (7:0), один для порта C (3:0) и один для порта C (7:4). Напротив, чипы Motorola и MOS обеспечивают только 16 контактов ввода-вывода плюс 4 контрольных контакта, но чипы Motorola/MOS позволяют индивидуально программировать направление (вход или выход) всех контактов ввода-вывода. Оба имеют конфигурации, которые будут выполнять определенное количество автоматического квитирования и генерации прерываний.

Другие сопоставимые микросхемы ввода-вывода микропроцессора — это программируемый периферийный интерфейс 2655 из семейства Signetics 2650 , Z80 PIO , Western Design Center WDC 65C21 (эквивалент Motorola 6820/6821), а также MOS Technology 6522 VIA и 6526 CIA , которые имели значительную дополнительную функциональность, такую как таймеры и сдвиговые регистры.

Промышленная версия Intel ID8255A была доступна по цене 17,55 долларов США в партиях от 100 штук и более. [4] Доступная версия Intel 8255A-5 была доступна по цене 6,55 долларов США в партиях от 100 штук и более. [5] Доступная версия 82C55A CMOS была передана на аутсорсинг компании Oki Electronic Industry Co., Ltd. [ 6] Доступный корпус от Intel имел марку 82C55 в 44-контактном PLCC выборки в четвертом квартале 1985 года. [7] В Восточной Европе эквивалентные схемы производились как KR580VV55A в Советском Союзе и как MHB8255A компанией Tesla в Чехословакии.

8255 широко использовался во многих микрокомпьютерных/микроконтроллерных системах и домашних компьютерах, таких как SV-328 и все модели MSX . 8255 использовался в оригинальном IBM-PC , [8] PC/XT, PC/jr и клонах, а также в многочисленных домашних компьютерах, таких как N8VEM .

8255 предоставляет процессору или цифровой системе доступ к программируемому параллельному вводу /выводу . [9] 8255 имеет 24 контакта ввода/вывода. [10] Они разделены на три 8-битных порта (A, B, C). [11] Порт A и порт B могут использоваться как 8-битные порты ввода/вывода. Порт C может использоваться как 8-битный порт ввода/вывода или как два 4-битных порта ввода/вывода или для создания сигналов квитирования для портов A и B.

Три порта далее сгруппированы следующим образом:

Восемь линий данных (D0–D7) доступны (с 8-битным буфером данных) для чтения/записи данных в порты или регистр управления при статусе RD (контакт 5) и WR (контакт 36), которые являются сигналами с активным низким уровнем для операций чтения и записи соответственно. Адресные линии A 1 и A 0 позволяют получить доступ к регистру данных для каждого порта или регистру управления, как указано ниже:

Сигнал управления выбором микросхемы CS (контакт 6) используется для включения микросхемы 8255. Это сигнал с активным низким уровнем, т. е. когда CS = 0, 8255 включен. Вход RESET (контакт 35) подключен к линии RESET системы, такой как 8085, 8086 и т. д., так что при сбросе системы все порты инициализируются как входные линии. Это делается для предотвращения выхода из строя 8255 и/или любого периферийного устройства, подключенного к нему, из-за несоответствия настроек направления порта. В качестве примера рассмотрим входное устройство, подключенное к 8255 через порт A. Если из предыдущей операции порт A инициализируется как выходной порт и если 8255 не был сброшен перед использованием текущей конфигурации, то существует вероятность повреждения либо подключенного входного устройства, либо 8255, либо обоих, поскольку и 8255, и подключенное устройство будут отправлять данные.

Регистр управления (или логика управления, или регистр командного слова) представляет собой 8-битный регистр, используемый для выбора режимов работы и обозначения входов/выходов портов. [12]

Существует два основных режима работы 8255:

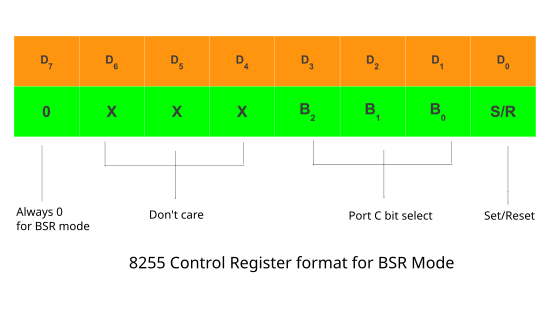

Два режима выбираются на основе значения, присутствующего в бите D 7 регистра управляющего слова. Когда D 7 = 1, 8255 работает в режиме ввода-вывода, а когда D 7 = 0, он работает в режиме BSR.

Режим установки/сброса бита (BSR) доступен только на порту C. Каждая линия порта C (PC 7 - PC 0 ) может быть установлена или сброшена путем записи соответствующего значения в регистр управляющего слова. Режим BSR и режим ввода-вывода независимы, и выбор режима BSR не влияет на работу других портов в режиме ввода-вывода. [13]

Выбор вывода порта C определяется следующим образом:

Например, если необходимо установить PC 5 , то в контрольном слове

Таким образом, согласно приведенным выше значениям, в регистр управляющего слова (CWR) будет загружено 0B (Hex).

Этот режим выбирается, когда бит D 7 регистра управляющего слова равен 1. Существует три режима ввода-вывода: [14]

Например, если порт B и верхний порт C должны быть инициализированы как входные порты, а нижний порт C и порт A — как выходные порты (все в режиме 0):

Следовательно, для требуемой операции регистр управляющего слова должен быть загружен значением «10001010» = 8A (шестнадцатеричное) .

В этом режиме порты могут использоваться для простых операций ввода-вывода без сигналов подтверждения связи. Порт A, порт B обеспечивают простую операцию ввода-вывода. Две половины порта C могут использоваться вместе как дополнительный 8-битный порт или как отдельные 4-битные порты. Поскольку две половины порта C независимы, их можно использовать так, чтобы одна половина была инициализирована как входной порт, а другая — как выходной порт.

Функции ввода/вывода в режиме 0 следующие:

«Зафиксированный» означает, что биты помещаются в регистр хранения (массив триггеров), который сохраняет свои выходные данные постоянными, даже если входные данные изменяются после фиксации.

Выходы 8255 защелкиваются для хранения последних записанных на них данных. Это необходимо, поскольку данные остаются на шине только в течение одного цикла. Таким образом, без защелкивания выходы станут недействительными, как только завершится цикл записи.

Входы не фиксируются, поскольку ЦП должен только считывать их текущие значения, а затем сохранять данные в регистре ЦП или памяти, если к ним нужно будет обратиться позже. Если вход изменяется во время чтения порта, то результат может быть неопределенным.

Когда мы хотим использовать порт A или порт B для квитирования (стробируемого) ввода или вывода, мы инициализируем этот порт в режиме 1 (порт A и порт B могут быть инициализированы для работы в разных режимах, т. е., например, порт A может работать в режиме 0, а порт B — в режиме 1). Некоторые из контактов порта C функционируют как линии квитирования.

Для порта B в этом режиме (независимо от того, действует ли он как входной или выходной порт) контакты PC0, PC1 и PC2 функционируют как линии квитирования.

Если порт A инициализирован как входной порт режима 1, то PC3, PC4 и PC5 функционируют как сигналы квитирования. Контакты PC6 и PC7 доступны для использования в качестве линий ввода/вывода.

Режим 1, поддерживающий квитирование, имеет следующие особенности:

Входные сигналы подтверждения связи

Выходные сигналы подтверждения связи

В этом режиме может быть инициализирован только порт A. Порт A может использоваться для двунаправленной передачи данных подтверждения связи. Это означает, что данные могут быть введены или выведены на одних и тех же восьми линиях (PA0 - PA7). Контакты PC3 - PC7 используются как линии подтверждения связи для порта A. Остальные контакты порта C (PC0 - PC2) могут использоваться как линии ввода/вывода, если группа B инициализирована в режиме 0, или как линии подтверждения связи для порта B, если группа B инициализирована в режиме 1. В этом режиме 8255 может использоваться для расширения системной шины до подчиненного микропроцессора или для передачи байтов данных на контроллер гибких дисков и с него . Сигналы подтверждения и подтверждения связи предоставляются для поддержания надлежащего потока данных и синхронизации между передатчиком и приемником данных.