Флэш-память — это электронная энергонезависимая компьютерная память , которая может быть электрически стерта и перепрограммирована. Два основных типа флэш-памяти, NOR flash и NAND flash , названы в честь логических вентилей NOR и NAND . Оба используют одинаковую конструкцию ячейки, состоящую из плавающих затворов MOSFET . Они различаются на уровне схемы в зависимости от того, подтянуто ли состояние битовой линии или линий слов к высокому или низкому уровню: в NAND flash связь между битовой линией и линиями слов напоминает вентиль NAND; в NOR flash она напоминает вентиль NOR.

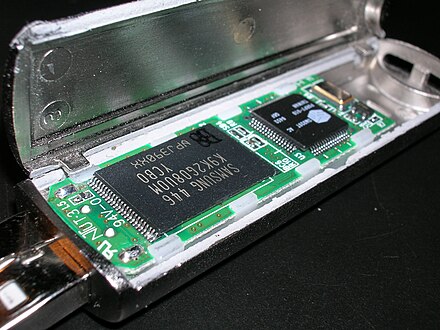

Флэш-память, тип памяти с плавающим затвором , была изобретена Фудзио Масуокой в Toshiba в 1980 году и основана на технологии EEPROM . Toshiba начала продавать флэш-память в 1987 году. [1] EPROM должны были быть полностью стерты, прежде чем их можно было перезаписать. Флэш-память NAND, однако, может быть стерта, записана и считана блоками (или страницами), которые, как правило, намного меньше, чем все устройство. Флэш-память NOR позволяет записывать одно машинное слово — в стертое место — или считывать его независимо. Устройство флэш-памяти обычно состоит из одной или нескольких микросхем флэш-памяти (каждая из которых содержит много ячеек флэш-памяти), а также отдельной микросхемы контроллера флэш-памяти .

Тип NAND в основном используется в картах памяти , USB-флеш-накопителях , твердотельных накопителях (выпущенных с 2009 года), телефонах с функциями , смартфонах и подобных продуктах для общего хранения и передачи данных. Флэш-память NAND или NOR также часто используется для хранения данных конфигурации в цифровых продуктах, что ранее было возможно благодаря EEPROM или статической оперативной памяти с питанием от батареи . Ключевым недостатком флэш-памяти является то, что она может выдержать лишь относительно небольшое количество циклов записи в определенном блоке. [2]

Флэш-память NOR известна своими возможностями прямого произвольного доступа, что делает ее пригодной для непосредственного выполнения кода. Ее архитектура допускает доступ к отдельным байтам, что обеспечивает более высокую скорость чтения по сравнению с флэш-памятью NAND. Флэш-память NAND работает с другой архитектурой, полагаясь на последовательный подход к доступу. Это делает NAND подходящей для хранения данных высокой плотности, но менее эффективной для задач произвольного доступа. Флэш-память NAND часто используется в сценариях, где решающее значение имеет экономически эффективное хранилище большой емкости, например, в USB-накопителях, картах памяти и твердотельных накопителях ( SSD ).

Основное отличие заключается в вариантах использования и внутренних структурах. Флэш-память NOR оптимальна для приложений, требующих быстрого доступа к отдельным байтам, например, во встроенных системах для выполнения программ. Флэш-память NAND, с другой стороны, блистает в сценариях, требующих экономически эффективного, высокоемкого хранилища с последовательным доступом к данным.

Флэш-память [3] используется в компьютерах , КПК , цифровых аудиоплеерах , цифровых камерах , мобильных телефонах , синтезаторах , видеоиграх , научных приборах , промышленной робототехнике и медицинской электронике . Флэш-память имеет быстрое время доступа для чтения , но она не такая быстрая, как статическая RAM или ROM. В портативных устройствах предпочтительнее использовать флэш-память из-за ее механической ударопрочности, поскольку механические приводы более подвержены механическим повреждениям. [4]

Поскольку циклы стирания медленные, большие размеры блоков, используемые при стирании флэш-памяти, дают ей значительное преимущество в скорости по сравнению с не-флеш-EEPROM при записи больших объемов данных. По состоянию на 2019 год [update]флэш-память стоит значительно меньше, чем байт-программируемая EEPROM, и стала доминирующим типом памяти везде, где система требует значительного объема энергонезависимого твердотельного хранилища . Однако EEPROM по-прежнему используются в приложениях, которым требуется лишь небольшой объем хранилища, например, в реализациях SPD на модулях компьютерной памяти. [5] [6]

Корпуса флэш-памяти могут использовать стекирование кристаллов со сквозными кремниевыми переходами и несколько десятков слоев ячеек 3D TLC NAND (на кристалл) одновременно для достижения емкости до 1 терабайта на корпус с использованием 16 сложенных кристаллов и интегрированного контроллера флэш-памяти в качестве отдельного кристалла внутри корпуса. [7] [8] [9] [10]

Истоки флэш-памяти можно проследить до разработки плавающего затвора MOSFET (FGMOS) , также известного как транзистор с плавающим затвором. [11] [12] Оригинальный MOSFET был изобретен в Bell Labs между 1955 и 1960 годами, после того как Фрош и Дерик открыли пассивацию поверхности и использовали свое открытие для создания первых планарных транзисторов. [13] [14] [ 15] [16] [17] [18] В 1967 году Давон Канг совместно с тайваньско-американским инженером Саймоном Минь Сзе в Bell Labs разработали его вариант — плавающий затвор MOSFET. [19] Они предложили использовать его в качестве ячеек памяти с плавающим затвором для хранения формы программируемой постоянной памяти ( PROM ), которая является как энергонезависимой, так и перепрограммируемой. [19]

Ранние типы памяти с плавающим затвором включали EPROM (стираемое PROM) и EEPROM (электрически стираемое PROM) в 1970-х годах. [19] Однако ранняя память с плавающим затвором требовала от инженеров создания ячейки памяти для каждого бита данных, что оказалось громоздким, [20] медленным, [21] и дорогим, что ограничило память с плавающим затвором узкоспециализированными приложениями в 1970-х годах, такими как военное оборудование и первые экспериментальные мобильные телефоны . [11]

Современная EEPROM , основанная на туннелировании Фаулера-Нордхайма для стирания данных, была изобретена Бернвардом и запатентована Siemens в 1974 году. [22] И далее доработана между 1976 и 1978 годами Элияху Харари из Hughes Aircraft Company и Джорджем Перлегосом и другими в Intel. [23] [24] Это привело к изобретению Масуокой флэш-памяти в Toshiba в 1980 году. [20] [25] [26] Улучшение между EEPROM и флэш-памятью заключается в том, что флэш-память программируется блоками, тогда как EEPROM программируется байтами. По словам Toshiba, название «флэш» было предложено коллегой Масуоки, Сёдзи Ариидзуми, потому что процесс стирания содержимого памяти напомнил ему вспышку камеры . [27] Масуока и его коллеги представили изобретение флэш-памяти NOR в 1984 году, [28] [29] , а затем флэш-память NAND на Международной конференции по электронным приборам IEEE 1987 года (IEDM), состоявшейся в Сан-Франциско. [30]

Toshiba коммерчески запустила флэш-память NAND в 1987 году. [1] [19] Корпорация Intel представила первый коммерческий чип флэш-памяти типа NOR в 1988 году. [31] Флэш-память на основе NOR имеет длительное время стирания и записи, но обеспечивает полный адрес и шины данных , позволяя произвольный доступ к любой ячейке памяти . Это делает ее подходящей заменой для старых чипов постоянной памяти (ПЗУ), которые используются для хранения программного кода, который редко нуждается в обновлении, например, BIOS компьютера или прошивки телевизионных приставок . Ее выносливость может составлять от всего лишь 100 циклов стирания для встроенной флэш-памяти, [32] до более типичных 10 000 или 100 000 циклов стирания, до 1 000 000 циклов стирания. [33] Флэш-память на основе NOR была основой ранних съемных носителей на основе флэш-памяти; CompactFlash изначально была основана на ней, хотя более поздние карты перешли на менее дорогую флэш-память NAND.

NAND flash имеет сокращенное время стирания и записи и требует меньше площади чипа на ячейку, что обеспечивает большую плотность хранения и меньшую стоимость за бит, чем NOR flash. Однако интерфейс ввода-вывода NAND flash не обеспечивает внешнюю адресную шину с произвольным доступом. Вместо этого данные должны считываться поблочно, с типичными размерами блоков от сотен до тысяч бит. Это делает NAND flash непригодной в качестве замены для программного ПЗУ, поскольку большинство микропроцессоров и микроконтроллеров требуют произвольного доступа на уровне байтов. В этом отношении NAND flash похожа на другие вторичные устройства хранения данных , такие как жесткие диски и оптические носители , и, таким образом, отлично подходит для использования в устройствах массового хранения, таких как карты памяти и твердотельные накопители (SSD). Например, SSD хранят данные с использованием нескольких чипов NAND flash-памяти.

Первым форматом сменных карт памяти на основе NAND был SmartMedia , выпущенный в 1995 году. За ним последовали многие другие, включая MultiMediaCard , Secure Digital , Memory Stick и xD-Picture Card .

Новое поколение форматов карт памяти, включая RS-MMC , miniSD и microSD , отличается чрезвычайно малыми форм-факторами. Например, карта microSD имеет площадь чуть более 1,5 см2 , а толщина менее 1 мм.

Флэш-память NAND достигла значительных уровней плотности памяти в результате нескольких крупных технологий, которые были коммерциализированы в конце 2000-х — начале 2010-х годов. [34]

Флэш-память NOR была наиболее распространенным типом флэш-памяти, продаваемым до 2005 года, пока флэш-память NAND не обогнала флэш-память NOR по продажам. [35]

Технология многоуровневых ячеек (MLC) позволяет хранить более одного бита в каждой ячейке памяти . NEC продемонстрировала технологию многоуровневых ячеек (MLC) в 1998 году с чипом флэш-памяти 80 Мб , хранящим 2 бита на ячейку. [36] STMicroelectronics также продемонстрировала MLC в 2000 году с чипом флэш-памяти NOR 64 МБ . [37] В 2009 году Toshiba и SanDisk представили чипы флэш-памяти NAND с технологией QLC, хранящие 4 бита на ячейку и имеющие емкость 64 Гбит. [38] [39] Samsung Electronics представила технологию трехуровневых ячеек (TLC), хранящую 3 бита на ячейку, и начала массовое производство чипов NAND с технологией TLC в 2010 году. [40]

Технология флэш-памяти с зарядовой ловушкой (CTF) заменяет плавающий затвор поликремния, который зажат между блокирующим оксидом затвора сверху и туннелирующим оксидом снизу, на электроизолирующий слой нитрида кремния; слой нитрида кремния улавливает электроны. Теоретически, CTF менее склонен к утечке электронов, обеспечивая улучшенное сохранение данных. [41] [42] [43] [44] [45] [46]

Поскольку CTF заменяет поликремний на электроизолирующий нитрид, он позволяет использовать ячейки меньшего размера и более высокую долговечность (меньшую деградацию или износ). Однако электроны могут захватываться и накапливаться в нитриде, что приводит к деградации. Утечка усиливается при высоких температурах, поскольку электроны становятся более возбужденными с ростом температуры. Однако технология CTF по-прежнему использует туннельный оксид и блокирующий слой, которые являются слабыми местами технологии, поскольку они все еще могут быть повреждены обычными способами (туннельный оксид может деградировать из-за чрезвычайно высоких электрических полей, а блокирующий слой из-за инжекции горячих дырок анода (AHHI). [47] [48]

Деградация или износ оксидов является причиной того, что флэш-память имеет ограниченную долговечность, а сохранение данных снижается (потенциал потери данных увеличивается) с увеличением деградации, поскольку оксиды теряют свои электроизоляционные свойства по мере деградации. Оксиды должны изолировать от электронов, чтобы предотвратить их утечку, которая может привести к потере данных.

В 1991 году исследователи NEC, включая Н. Кодаму, К. Ояму и Хироки Шираи, описали тип флэш-памяти с методом захвата заряда. [49] В 1998 году Боаз Эйтан из Saifun Semiconductors (позже приобретенный Spansion ) запатентовал технологию флэш-памяти под названием NROM, которая использовала слой захвата заряда для замены обычного плавающего затвора, используемого в обычных конструкциях флэш-памяти. [50] В 2000 году исследовательская группа Advanced Micro Devices (AMD) под руководством Ричарда М. Фастоу, египетского инженера Халеда З. Ахмеда и иорданского инженера Самира Хаддада (который позже присоединился к Spansion) продемонстрировала механизм захвата заряда для ячеек флэш-памяти NOR. [ 51] Позднее CTF был коммерциализирован AMD и Fujitsu в 2002 году . [52] Технология 3D V-NAND (вертикальная NAND) позволяет вертикально размещать ячейки флэш-памяти NAND внутри чипа с использованием технологии 3D-зарядной ловушки (CTP). Технология 3D V-NAND была впервые анонсирована Toshiba в 2007 году [53] , а первое устройство с 24 слоями было впервые выпущено в продажу компанией Samsung Electronics в 2013 году [54] [55].

Технология 3D-интегральных схем (3D IC) позволяет вертикально размещать микросхемы интегральных схем (ИС) в одном корпусе 3D-микросхемы. [34] Toshiba представила технологию 3D IC для флэш-памяти NAND в апреле 2007 года, когда они дебютировали с 16 ГБ eMMC-совместимым (номер продукта THGAM0G7D8DBAI6, часто сокращенно THGAM на потребительских веб-сайтах) встроенным чипом флэш-памяти NAND, который был изготовлен из восьми сложенных друг на друга 2 ГБ чипов флэш-памяти NAND. [56] В сентябре 2007 года Hynix Semiconductor (теперь SK Hynix ) представила 24-слойную технологию 3D IC с чипом флэш-памяти 16 ГБ, который был изготовлен из 24 сложенных друг на друга чипов флэш-памяти NAND с использованием процесса соединения пластин. [57] Toshiba также использовала восьмислойную 3D IC для своего 32 ГБ флэш-чипа THGBM в 2008 году . [58] В 2010 году Toshiba использовала 16-слойную 3D IC для своего 128 ГБ флэш-чипа THGBM2, который был изготовлен из 16 сложенных друг на друга 8 ГБ чипов. [59] В 2010-х годах 3D IC стали широко использоваться в коммерческих целях для флэш-памяти NAND в мобильных устройствах . [34]

В 2016 году Micron и Intel представили технологию, известную как CMOS Under the Array/CMOS Under Array (CUA), Core over Periphery (COP), Periphery Under Cell (PUA) или Xtacking, [60] , в которой схема управления для флэш-памяти размещается под или над массивом ячеек флэш-памяти. Это позволило увеличить количество плоскостей или секций чипа флэш-памяти с 2 до 4, не увеличивая площадь, выделенную для схем управления или периферии. Это увеличивает количество операций ввода-вывода на чип флэш-памяти или кристалл, но также создает проблемы при создании конденсаторов для зарядовых насосов, используемых для записи во флэш-память. [61] [62] [63] Некоторые кристаллы флэш-памяти имеют до 6 плоскостей. [64]

По состоянию на август 2017 года доступны карты microSD емкостью до 400 ГБ (400 миллиардов байт). [65] [66] В том же году Samsung объединила технологию 3D IC stacking с технологиями 3D V-NAND и TLC для производства чипа флэш-памяти KLUFG8R1EM емкостью 512 ГБ с восемью сложенными 64-слойными чипами V-NAND. [8] В 2019 году Samsung выпустила чип флэш-памяти емкостью 1024 ГБ с восемью сложенными 96-слойными чипами V-NAND и технологией QLC. [67] [68]

Флэш-память хранит информацию в массиве ячеек памяти, изготовленных из транзисторов с плавающим затвором . В устройствах с одноуровневыми ячейками (SLC) каждая ячейка хранит только один бит информации. Устройства с многоуровневыми ячейками (MLC), включая устройства с трехуровневыми ячейками (TLC), могут хранить более одного бита на ячейку.

Плавающий затвор может быть проводящим (обычно поликремний в большинстве видов флэш-памяти) или непроводящим (как во флэш-памяти SONOS ). [69]

В флэш-памяти каждая ячейка памяти напоминает стандартный полевой транзистор металл-оксид-полупроводник (MOSFET), за исключением того, что транзистор имеет два затвора вместо одного. Ячейки можно рассматривать как электрический переключатель, в котором ток течет между двумя клеммами (источник и сток) и управляется плавающим затвором (FG) и управляющим затвором (CG). CG похож на затвор в других МОП-транзисторах, но под ним находится FG, изолированный со всех сторон оксидным слоем. FG расположен между CG и каналом MOSFET. Поскольку FG электрически изолирован своим изолирующим слоем, электроны, размещенные на нем, захватываются. Когда FG заряжается электронами, этот заряд экранирует электрическое поле от CG, тем самым увеличивая пороговое напряжение (V T ) ячейки. Это означает, что V T ячейки можно изменять между пороговым напряжением незаряженного FG (V T1 ) и более заряженного порогового напряжения FG (V T2 ) путем изменения заряда FG. Для считывания значения из ячейки к CG подается промежуточное напряжение (V I ) между V T1 и V T2 . Если канал проводит ток при V I , FG должен быть незаряженным (если бы он был заряжен, проводимости бы не было, поскольку V I меньше V T2 ). Если канал не проводит ток при V I , это означает, что FG заряжен. Двоичное значение ячейки определяется путем определения того, протекает ли ток через транзистор, когда V I подается на CG. В многоуровневом устройстве ячейки, которое хранит более одного бита на ячейку, определяется величина тока (а не просто его наличие или отсутствие), чтобы точнее определить уровень заряда на FG.

Плавающий затвор MOSFET так называется потому, что между плавающим затвором и кремнием находится электрически изолирующий туннельный оксидный слой, поэтому затвор «плавает» над кремнием. Оксид удерживает электроны в плавающем затворе. Деградация или износ (и ограниченная долговечность флэш-памяти с плавающим затвором) происходит из-за чрезвычайно высокого электрического поля (10 миллионов вольт на сантиметр), испытываемого оксидом. Такие высокие плотности напряжения могут со временем разрушать атомные связи в относительно тонком оксиде, постепенно ухудшая его электроизолирующие свойства и позволяя электронам захватываться и свободно проходить (просачиваться) из плавающего затвора в оксид, увеличивая вероятность потери данных, поскольку электроны (количество которых используется для представления различных уровней заряда, каждый из которых назначается различной комбинации битов в MLC Flash) обычно находятся в плавающем затворе. Вот почему сохранение данных снижается, а риск потери данных увеличивается с увеличением деградации. [70] [71] [45] [72] [73] Оксид кремния в ячейке деградирует с каждой операцией стирания. Деградация увеличивает количество отрицательного заряда в ячейке с течением времени из-за захваченных электронов в оксиде и сводит на нет часть напряжения управляющего затвора, это со временем также делает стирание ячейки более медленным, поэтому для поддержания производительности и надежности чипа NAND ячейку необходимо вывести из эксплуатации. Износостойкость также уменьшается с количеством бит в ячейке. С большим количеством бит в ячейке количество возможных состояний (каждое представлено различным уровнем напряжения) в ячейке увеличивается и становится более чувствительным к напряжениям, используемым для программирования. Напряжения можно регулировать для компенсации деградации оксида кремния, и по мере увеличения количества бит количество возможных состояний также увеличивается, и, таким образом, ячейка менее терпима к корректировкам программных напряжений, поскольку между уровнями напряжения, которые определяют каждое состояние в ячейке, меньше пространства. [74]

Процесс перемещения электронов из управляющего затвора в плавающий затвор называется туннелированием Фаулера-Нордхейма , и он фундаментально изменяет характеристики ячейки, увеличивая пороговое напряжение МОП-транзистора. Это, в свою очередь, изменяет ток сток-исток, который протекает через транзистор для заданного напряжения затвора, которое в конечном итоге используется для кодирования двоичного значения. Эффект туннелирования Фаулера-Нордхейма обратим, поэтому электроны могут быть добавлены или удалены из плавающего затвора, процессы традиционно известны как запись и стирание. [75]

Несмотря на необходимость относительно высоких напряжений программирования и стирания, практически все флэш-чипы сегодня требуют только одного напряжения питания и вырабатывают требуемые высокие напряжения с помощью встроенных в чип зарядовых насосов .

Более половины энергии, потребляемой 1,8 В флэш-чипом NAND, теряется в самом зарядовом насосе. Поскольку повышающие преобразователи по своей природе более эффективны, чем зарядовые насосы, исследователи, разрабатывающие маломощные SSD, предложили вернуться к двойным напряжениям питания Vcc/Vpp, которые использовались во всех ранних флэш-чипах, управляя высоким напряжением Vpp для всех флэш-чипов в SSD с помощью одного общего внешнего повышающего преобразователя. [76] [77] [78] [79] [80] [81] [82] [83]

В космических аппаратах и других средах с высоким уровнем радиации встроенный в чип зарядовый насос является первой частью флэш-чипа, которая выходит из строя, хотя флэш-память будет продолжать работать — в режиме только для чтения — при гораздо более высоких уровнях радиации. [84]

В NOR flash каждая ячейка имеет один конец, подключенный непосредственно к земле, а другой конец, подключенный непосредственно к битовой линии. Такое расположение называется «NOR flash», потому что оно действует как вентиль NOR: когда одна из линий слов (подключенная к CG ячейки) переводится на высокий уровень, соответствующий транзистор хранения действует, чтобы понизить выходную битовую линию. NOR flash продолжает оставаться технологией выбора для встраиваемых приложений, требующих дискретного энергонезависимого запоминающего устройства. [ необходима цитата ] Низкие задержки чтения, характерные для устройств NOR, позволяют как прямое выполнение кода, так и хранение данных в одном продукте памяти. [85]

Одноуровневая ячейка флэш-памяти NOR в состоянии по умолчанию логически эквивалентна двоичному значению "1", поскольку ток будет протекать через канал при подаче соответствующего напряжения на управляющий затвор, так что напряжение битовой линии будет понижено. Ячейка флэш-памяти NOR может быть запрограммирована или установлена на двоичное значение "0" с помощью следующей процедуры:

Чтобы стереть ячейку флэш-памяти NOR (сбросив ее в состояние «1»), между CG и клеммой источника подается большое напряжение противоположной полярности , вытягивая электроны из FG через туннелирование Фаулера-Нордгейма (туннелирование FN). [86] Это известно как стирание источника-источника с отрицательным затвором. Более новые запоминающие устройства NOR могут стирать данные с использованием стирания канала отрицательного затвора, которое смещает линию слова на блоке ячеек памяти NOR и P-well блока ячеек памяти, чтобы обеспечить выполнение туннелирования FN, стирая блок ячеек. Более старые запоминающие устройства использовали стирание источника, при котором высокое напряжение подавалось на источник, а затем электроны из FG перемещались в источник. [87] [88] Современные чипы флэш-памяти NOR разделены на сегменты стирания (часто называемые блоками или секторами). Операция стирания может быть выполнена только поблочно; все ячейки в сегменте стирания должны быть стерты вместе. [89] Однако программирование ячеек NOR обычно может выполняться по одному байту или слову за раз.

Флэш-память NAND также использует транзисторы с плавающим затвором , но они соединены способом, который напоминает вентиль NAND : несколько транзисторов соединены последовательно, и линия бита подтянута к низкому уровню только в том случае, если все линии слов подтянуты к высокому уровню (выше V T транзисторов ) . Затем эти группы соединены через несколько дополнительных транзисторов в массив битовых линий в стиле NOR таким же образом, как отдельные транзисторы соединены в флэш-памяти NOR.

По сравнению с NOR flash, замена отдельных транзисторов на последовательно связанные группы добавляет дополнительный уровень адресации. В то время как NOR flash может адресовать память постранично, а затем пословно, NAND flash может адресовать ее постранично, пословно и побитно. Адресация на уровне бит подходит для приложений с последовательной передачей битов (таких как эмуляция жесткого диска), которые обращаются только к одному биту за раз. С другой стороны, приложения Execute-in-place требуют, чтобы к каждому биту в слове был доступ одновременно. Для этого требуется адресация на уровне слов. В любом случае, как режимы адресации битов, так и режимы адресации слов возможны как с NOR, так и с NAND flash.

Для считывания данных сначала выбирается нужная группа (так же, как выбирается один транзистор из массива NOR). Затем большинство линий слов подтягиваются выше V T2 , а одна из них подтягивается к V I . Последовательная группа будет проводить (и подтягивать линию бита к низкому уровню), если выбранный бит не был запрограммирован.

Несмотря на дополнительные транзисторы, сокращение заземляющих проводов и битовых линий позволяет плотнее расположить и увеличить емкость памяти на кристалл. (Заземляющие провода и битовые линии на самом деле намного шире линий на схемах.) Кроме того, флэш-память NAND обычно может содержать определенное количество неисправностей (флеш-память NOR, используемая для ПЗУ BIOS , как ожидается, будет безошибочной). Производители пытаются максимально увеличить объем полезной памяти, уменьшая размер транзисторов или ячеек, однако отрасль может избежать этого и достичь более высокой плотности памяти на кристалл, используя 3D NAND, которая располагает ячейки друг над другом.

Ячейки флэш-памяти NAND считываются путем анализа их реакции на различные напряжения. [72]

Флэш-память NAND использует туннельную инъекцию для записи и туннельный выпуск для стирания. Флэш-память NAND является основой съемных USB- накопителей, известных как USB-флеш-накопители , а также большинства форматов карт памяти и твердотельных накопителей, доступных сегодня.

Иерархическая структура флэш-памяти NAND начинается на уровне ячеек, которая устанавливает строки, затем страницы, блоки, плоскости и, в конечном счете, кристалл. Строка представляет собой ряд соединенных ячеек NAND, в которых источник одной ячейки соединен со стоком следующей. В зависимости от технологии NAND строка обычно состоит из 32–128 ячеек NAND. Строки организованы в страницы, которые затем организованы в блоки, в которых каждая строка соединена с отдельной линией, называемой битовой линией. Все ячейки с одинаковым положением в строке соединены через управляющие вентили с помощью словарной линии. Плоскость содержит определенное количество блоков, соединенных через одну и ту же битовую линию. Кристалл флэш-памяти состоит из одной или нескольких плоскостей и периферийной схемы, которая необходима для выполнения всех операций чтения, записи и стирания.

Архитектура флэш-памяти NAND означает, что данные могут быть прочитаны и запрограммированы (записаны) страницами, обычно размером от 4 до 16 КБ, но могут быть стерты только на уровне целых блоков, состоящих из нескольких страниц. Когда блок стирается, все ячейки логически устанавливаются в 1. Данные могут быть запрограммированы только за один проход на страницу в блоке, который был стерт. Процесс программирования устанавливает одну или несколько ячеек с 1 на 0. Любые ячейки, которые были установлены в 0 путем программирования, могут быть сброшены в 1 только путем стирания всего блока. Это означает, что перед тем, как новые данные могут быть запрограммированы на страницу, которая уже содержит данные, текущее содержимое страницы плюс новые данные должны быть скопированы на новую стертую страницу. Если доступна подходящая стертая страница, данные могут быть записаны на нее немедленно. Если стертая страница недоступна, блок должен быть стерт перед копированием данных на страницу в этом блоке. Затем старая страница помечается как недействительная и доступна для стирания и повторного использования. [90] Это отличается от представления LBA операционной системы , например, если операционная система записывает 1100 0011 на флэш-накопитель (такой как SSD ), данные, фактически записанные на флэш-память, могут быть 0011 1100.

Вертикальная память NAND (V-NAND) или 3D NAND укладывает ячейки памяти вертикально и использует архитектуру флэш-памяти с зарядовой ловушкой . Вертикальные слои позволяют увеличить плотность битов, не требуя меньших отдельных ячеек. [91] Она также продается под торговой маркой BiCS Flash , которая является торговой маркой Kioxia Corporation (ранее Toshiba Memory Corporation). 3D NAND была впервые анонсирована Toshiba в 2007 году . [53] V-NAND была впервые произведена в коммерческих целях компанией Samsung Electronics в 2013 году. [54] [55] [92] [93]

V-NAND использует геометрию флэш-памяти с ловушкой заряда (которая была коммерчески представлена в 2002 году AMD и Fujitsu ) [52] , которая хранит заряд на встроенной пленке нитрида кремния . Такая пленка более устойчива к точечным дефектам и может быть сделана толще, чтобы удерживать большее количество электронов. V-NAND обертывает плоскую ячейку ловушки заряда в цилиндрическую форму. [91] По состоянию на 2020 год флэш-память 3D NAND от Micron и Intel вместо этого использует плавающие затворы, однако, 128-слойная и выше память 3D NAND от Micron использует обычную структуру ловушки заряда из-за прекращения партнерства между Micron и Intel. Флэш-память 3D NAND с ловушкой заряда тоньше, чем 3D NAND с плавающим затвором. В 3D NAND с плавающим затвором ячейки памяти полностью отделены друг от друга, тогда как в 3D NAND с ловушкой заряда вертикальные группы ячеек памяти используют один и тот же материал нитрида кремния. [94]

Отдельная ячейка памяти состоит из одного плоского слоя поликремния, содержащего отверстие, заполненное несколькими концентрическими вертикальными цилиндрами. Поверхность поликремния отверстия действует как затворный электрод. Самый внешний цилиндр диоксида кремния действует как затворный диэлектрик, заключая в себе цилиндр из нитрида кремния, который хранит заряд, в свою очередь заключая в себе цилиндр из диоксида кремния как туннельный диэлектрик, который окружает центральный стержень из проводящего поликремния, который действует как проводящий канал. [91]

Ячейки памяти в разных вертикальных слоях не мешают друг другу, поскольку заряды не могут перемещаться вертикально через носитель информации из нитрида кремния, а электрические поля, связанные с затворами, тесно ограничены внутри каждого слоя. Вертикальный набор электрически идентичен последовательно связанным группам, в которых сконфигурирована обычная флэш-память NAND. [91] Существует также укладка строк, которая создает несколько массивов памяти 3D NAND или «заглушек» [95] отдельно, но укладываются вместе, чтобы создать продукт с большим количеством слоев 3D NAND на одном кристалле. Часто укладываются два или 3 массива. Несовпадение между заглушками составляет порядка 30–10 нм. [61] [96] [97]

Рост группы ячеек V-NAND начинается с чередующегося набора проводящих (легированных) слоев поликремния и изолирующих слоев диоксида кремния. [91]

Следующий шаг — сформировать цилиндрическое отверстие через эти слои. На практике чип V-NAND емкостью 128 Гбит с 24 слоями ячеек памяти требует около 2,9 миллиарда таких отверстий. Затем внутренняя поверхность отверстия получает несколько покрытий, сначала диоксид кремния, затем нитрид кремния, затем второй слой диоксида кремния. Наконец, отверстие заполняется проводящим (легированным) поликремнием. [91]

По состоянию на 2013 год [update]архитектура флэш-памяти V-NAND позволяет выполнять операции чтения и записи в два раза быстрее, чем обычная NAND, и может работать до 10 раз дольше, потребляя при этом на 50 процентов меньше энергии. Они предлагают сопоставимую физическую плотность битов с использованием 10-нм литографии, но могут увеличить плотность битов до двух порядков, учитывая использование V-NAND до нескольких сотен слоев. [91] По состоянию на 2020 год чипы V-NAND со 160 слоями находятся в стадии разработки Samsung. [98] По мере увеличения количества слоев емкость и выносливость флэш-памяти могут быть увеличены.

Стоимость пластины 3D NAND сопоставима с уменьшенной (32 нм или меньше) планарной флэш-памятью NAND. [99] Однако, при масштабировании планарной NAND, остановившемся на 16 нм, снижение стоимости за бит может продолжаться для 3D NAND, начиная с 16 слоев. Однако из-за невертикальной боковой стенки отверстия, протравленного через слои; даже небольшое отклонение приводит к минимальной стоимости бита, т. е. минимальному эквивалентному правилу проектирования (или максимальной плотности), для заданного количества слоев; это минимальное количество слоев стоимости бита уменьшается для меньшего диаметра отверстия. [100]

Одним из ограничений флэш-памяти является то, что ее можно стирать только по одному блоку за раз. Обычно это устанавливает все биты в блоке в 1. Начиная с только что стертого блока, можно запрограммировать любое местоположение внутри этого блока. Однако после того, как бит был установлен в 0, только стерев весь блок, его можно вернуть в 1. Другими словами, флэш-память (в частности, флэш-память NOR) предлагает операции чтения и программирования с произвольным доступом, но не предлагает произвольные операции перезаписи или стирания с произвольным доступом. Местоположение, однако, может быть перезаписано, пока биты 0 нового значения являются надмножеством перезаписанных значений. Например, значение полубайта может быть стерто до 1111, затем записано как 1110. Последовательные записи в этот полубайт могут изменить его на 1010, затем на 0010 и, наконец, на 0000. По сути, стирание устанавливает все биты в 1, а программирование может очистить биты только до 0. [101] Некоторые файловые системы, разработанные для флэш-устройств, используют эту возможность перезаписи, например YAFFS1 , для представления метаданных сектора. Другие файловые системы флэш-памяти, такие как YAFFS2 , никогда не используют эту возможность «перезаписи» — они выполняют много дополнительной работы, чтобы соответствовать правилу «однократной записи».

Хотя структуры данных во флэш-памяти не могут быть обновлены полностью общими способами, это позволяет "удалять" элементы, помечая их как недействительные. Эту технику может потребоваться модифицировать для многоуровневых устройств ячеек, где одна ячейка памяти содержит более одного бита.

Обычные флэш-устройства, такие как USB-флеш-накопители и карты памяти, предоставляют только интерфейс на уровне блоков или слой трансляции флэш-памяти (FTL), который каждый раз записывает данные в другую ячейку для выравнивания уровня износа устройства. Это предотвращает инкрементную запись в пределах блока; однако это помогает устройству избежать преждевременного износа из-за интенсивных шаблонов записи.

Данные, хранящиеся на флэш-ячейках, постоянно теряются из-за электронного деловушки [ требуется определение ] . Скорость потери увеличивается экспоненциально с ростом абсолютной температуры . Например: для 45 нм NOR-вспышки при 1000 часах потеря порогового напряжения (Vt) при 25°C примерно вдвое меньше, чем при 90°C. [102]

Другим ограничением является то, что флэш-память имеет конечное число циклов стирания программ (обычно обозначаемых как циклы P/E). [103] [104] Micron Technology и Sun Microsystems 17 декабря 2008 года анонсировали чип флэш-памяти SLC NAND, рассчитанный на 1 000 000 циклов P/E. [105]

Гарантированное количество циклов может применяться только к нулевому блоку (как в случае с устройствами TSOP NAND) или ко всем блокам (как в NOR). Этот эффект смягчается в некоторых микропрограммах чипов или драйверах файловой системы путем подсчета записей и динамического переназначения блоков для распределения операций записи между секторами; эта техника называется выравниванием износа . Другой подход заключается в выполнении проверки записи и переназначении на запасные сектора в случае сбоя записи, техника, называемая управлением плохими блоками (BBM). Для портативных потребительских устройств эти методы управления износом обычно продлевают срок службы флэш-памяти сверх срока службы самого устройства, и некоторая потеря данных может быть приемлемой в этих приложениях. Однако для высоконадежного хранения данных не рекомендуется использовать флэш-память, которая должна будет пройти через большое количество циклов программирования. Это ограничение также существует для приложений «только для чтения», таких как тонкие клиенты и маршрутизаторы , которые программируются только один раз или максимум несколько раз в течение своего срока службы из-за помех при чтении (см. ниже).

В декабре 2012 года тайваньские инженеры из Macronix объявили о своем намерении объявить на Международной конференции IEEE по электронным приборам 2012 года, что они выяснили, как улучшить циклы чтения/записи флэш-памяти NAND с 10 000 до 100 миллионов циклов, используя процесс «самовосстановления», который использовал флэш-чип со «встроенными нагревателями, которые могли отжигать небольшие группы ячеек памяти». [106] Встроенный термический отжиг должен был заменить обычный цикл стирания локальным высокотемпературным процессом, который не только стирал сохраненный заряд, но и восстанавливал вызванное электронами напряжение в чипе, обеспечивая циклы записи не менее 100 миллионов. [107] Результатом должен был стать чип, который можно было бы стирать и перезаписывать снова и снова, даже если он теоретически должен был выйти из строя. Однако, каким бы многообещающим ни был прорыв Macronix для мобильной индустрии, не было никаких планов по выпуску коммерческого продукта с такой возможностью в ближайшем будущем. [108]

Метод, используемый для чтения флэш-памяти NAND, может привести к тому, что соседние ячейки в одном и том же блоке памяти со временем изменятся (станут запрограммированными). Это известно как нарушение чтения. Пороговое число чтений обычно составляет сотни тысяч чтений между промежуточными операциями стирания. Если чтение из одной ячейки происходит непрерывно, эта ячейка не выйдет из строя, а одна из соседних ячеек выйдет из строя при последующем чтении. Чтобы избежать проблемы нарушения чтения, контроллер флэш-памяти обычно подсчитывает общее количество чтений блока с момента последнего стирания. Когда счет превышает целевой предел, затронутый блок копируется в новый блок, стирается, а затем высвобождается в пул блоков. Исходный блок после стирания будет как новый. Однако, если контроллер флэш-памяти не вмешается вовремя, произойдет ошибка нарушения чтения с возможной потерей данных, если ошибок слишком много, чтобы исправить их с помощью кода исправления ошибок . [109] [110] [111]

Большинство флэш-микросхем поставляются в корпусах BGA ( ball grid array ), и даже те, которые не имеют таких корпусов, часто монтируются на печатной плате рядом с другими корпусами BGA. После сборки печатной платы платы с корпусами BGA часто просвечиваются рентгеновскими лучами, чтобы увидеть, правильно ли шарики соединяются с правильной площадкой или требуется ли переделка BGA . Эти рентгеновские лучи могут стереть запрограммированные биты во флэш-чипе (преобразовать запрограммированные биты «0» в стертые биты «1»). Стертые биты («биты «1») не подвержены воздействию рентгеновских лучей. [112] [113]

Некоторые производители сейчас выпускают устройства памяти SD [114] и USB [115] , устойчивые к рентгеновскому излучению .

Низкоуровневый интерфейс к микросхемам флэш-памяти отличается от интерфейсов других типов памяти, таких как DRAM , ROM и EEPROM , которые поддерживают возможность изменения битов (как от нуля к единице, так и от единицы к нулю) и произвольный доступ через доступные извне адресные шины .

Память NOR имеет внешнюю адресную шину для чтения и программирования. Для памяти NOR чтение и программирование являются произвольным доступом, а разблокировка и стирание — поблочными. Для памяти NAND чтение и программирование являются страничными, а разблокировка и стирание — поблочными.

Чтение из NOR flash похоже на чтение из памяти с произвольным доступом, при условии, что адрес и шина данных сопоставлены правильно. Из-за этого большинство микропроцессоров могут использовать NOR flash memory как память исполнения на месте (XIP), [116] что означает, что программы, хранящиеся во NOR flash, могут быть выполнены непосредственно из NOR flash без необходимости предварительного копирования в ОЗУ. NOR flash может быть запрограммирована способом произвольного доступа, похожим на чтение. Программирование изменяет биты с логической единицы на ноль. Биты, которые уже равны нулю, остаются неизменными. Стирание должно происходить по блоку за раз и сбрасывает все биты в стертом блоке обратно в единицу. Типичные размеры блоков составляют 64, 128 или 256 КиБ .

Управление плохими блоками — относительно новая функция в чипах NOR. В старых устройствах NOR, не поддерживающих управление плохими блоками, программное обеспечение или драйвер устройства, управляющий чипом памяти, должны корректировать блоки, которые изнашиваются, иначе устройство перестанет работать надежно.

Конкретные команды, используемые для блокировки, разблокировки, программирования или стирания памяти NOR, различаются у каждого производителя. Чтобы избежать необходимости в уникальном программном обеспечении драйвера для каждого изготовленного устройства, специальные команды Common Flash Memory Interface (CFI) позволяют устройству идентифицировать себя и свои критические рабочие параметры.

Помимо использования в качестве ПЗУ с произвольным доступом, флэш-память NOR также может использоваться в качестве устройства хранения данных, используя преимущества программирования с произвольным доступом. Некоторые устройства предлагают функциональность чтения во время записи, так что код продолжает выполняться даже во время выполнения программы или операции стирания в фоновом режиме. Для последовательной записи данных чипы флэш-памяти NOR обычно имеют более низкую скорость записи по сравнению с флэш-памятью NAND.

Типичная флэш-память NOR не нуждается в коде исправления ошибок . [117]

Архитектура флэш-памяти NAND была представлена Toshiba в 1989 году. [118] Доступ к этим запоминающим устройствам осуществляется так же, как к блочным устройствам , таким как жесткие диски. Каждый блок состоит из нескольких страниц. Страницы обычно имеют размер 512, [119] 2048 или 4096 байт. С каждой страницей связано несколько байт (обычно 1/32 размера данных), которые можно использовать для хранения контрольной суммы кода исправления ошибок (ECC) .

Типичные размеры блоков включают:

Современная флэш-память NAND может иметь размер стираемого блока от 1 до 128 МБ. В то время как чтение и программирование выполняются на основе страниц, стирание может выполняться только на основе блоков. [122] Поскольку изменение ячейки с 0 на 1 требует стирания всего блока, а не просто изменения некоторых страниц, изменение данных блока может потребовать процесса чтения-стирания-записи, а новые данные фактически перемещаются в другой блок. Кроме того, на SSD-накопителе NVM Express Zoned Namespaces обычно используется размер блока флэш-памяти в качестве размера зоны.

Устройства NAND также требуют управления плохими блоками с помощью программного обеспечения драйвера устройства или отдельной микросхемы контроллера . Некоторые карты SD, например, включают схему контроллера для управления плохими блоками и выравнивания износа . Когда к логическому блоку обращается программное обеспечение высокого уровня, он сопоставляется с физическим блоком драйвером устройства или контроллером. Ряд блоков на микросхеме флэш-памяти может быть отведен для хранения таблиц сопоставления, чтобы иметь дело с плохими блоками, или система может просто проверять каждый блок при включении питания, чтобы создать карту плохих блоков в ОЗУ. Общая емкость памяти постепенно уменьшается по мере того, как все больше блоков помечаются как плохие.

NAND использует ECC для компенсации битов, которые могут спонтанно выйти из строя во время нормальной работы устройства. Типичный ECC исправит однобитовую ошибку в каждых 2048 битах (256 байтах) с помощью 22 бит ECC или однобитовую ошибку в каждых 4096 битах (512 байтах) с помощью 24 бит ECC. [123] Если ECC не может исправить ошибку во время чтения, он все равно может ее обнаружить. При выполнении операций стирания или программирования устройство может обнаружить блоки, которые не удалось запрограммировать или стереть, и пометить их как плохие. Затем данные записываются в другой, хороший блок, а карта плохих блоков обновляется.

Коды Хэмминга являются наиболее часто используемыми кодами ECC для флэш-памяти SLC NAND. Коды Рида-Соломона и коды BCH (коды Боуза-Чоудхури-Хоквингема) являются обычно используемыми кодами ECC для флэш-памяти MLC NAND. Некоторые микросхемы флэш-памяти MLC NAND генерируют внутри соответствующие коды коррекции ошибок BCH. [117]

Большинство устройств NAND поставляются с завода с некоторыми плохими блоками. Обычно они маркируются в соответствии с определенной стратегией маркировки плохих блоков. Допуская некоторые плохие блоки, производители достигают гораздо более высоких показателей выхода , чем это было бы возможно, если бы все блоки должны были быть проверены на пригодность. Это значительно снижает затраты на флэш-память NAND и лишь немного уменьшает емкость хранения деталей.

При выполнении программного обеспечения из памяти NAND часто используются стратегии виртуальной памяти : содержимое памяти сначала должно быть выгружено или скопировано в отображенную в память RAM и выполнено там (что приводит к распространенной комбинации NAND + RAM). Блок управления памятью (MMU) в системе полезен, но это также может быть достигнуто с помощью оверлеев . По этой причине некоторые системы будут использовать комбинацию памяти NOR и NAND, где меньшая память NOR используется как программное ПЗУ, а большая память NAND разделена файловой системой для использования в качестве энергонезависимой области хранения данных.

NAND жертвует преимуществами NOR в области случайного доступа и выполнения на месте. NAND лучше всего подходит для систем, требующих хранения данных большой емкости. Он обеспечивает более высокую плотность, большую емкость и более низкую стоимость. Он обеспечивает более быстрое стирание, последовательную запись и последовательное чтение.

Группа под названием Open NAND Flash Interface Working Group (ONFI) разработала стандартизированный низкоуровневый интерфейс для чипов NAND flash. Это обеспечивает взаимодействие между соответствующими устройствами NAND от разных поставщиков. Спецификация ONFI версии 1.0 [124] была выпущена 28 декабря 2006 года. Она определяет:

Группа ONFI поддерживается основными производителями флэш-памяти NAND, включая Hynix , Intel , Micron Technology и Numonyx , а также основными производителями устройств, включающих чипы флэш-памяти NAND. [125]

Два основных производителя флэш-устройств, Toshiba и Samsung , решили использовать интерфейс собственной разработки, известный как Toggle Mode (теперь Toggle). Этот интерфейс несовместим по контактам со спецификацией ONFI. В результате продукт, разработанный для устройств одного поставщика, может не поддерживать устройства другого поставщика. [126]

Группа поставщиков, включая Intel , Dell и Microsoft , сформировала рабочую группу Non-Volatile Memory Host Controller Interface (NVMHCI). [127] Целью группы является предоставление стандартных программных и аппаратных интерфейсов программирования для подсистем энергонезависимой памяти, включая устройство «флэш-кэш», подключенное к шине PCI Express .

Флэш-память NOR и NAND отличается двумя важными моментами:

NOR [134] и NAND flash получили свои названия от структуры взаимосвязей между ячейками памяти. [135] В NOR flash ячейки подключены параллельно к битовым линиям, что позволяет считывать и программировать ячейки по отдельности. [136] Параллельное соединение ячеек напоминает параллельное соединение транзисторов в вентиле CMOS NOR. [137] В NAND flash ячейки подключены последовательно, [136] напоминая вентили CMOS NAND. Последовательные соединения занимают меньше места, чем параллельные, что снижает стоимость NAND flash. [136] Само по себе это не препятствует считыванию и программированию ячеек NAND по отдельности. [ необходима цитата ]

Каждая ячейка флэш-памяти NOR больше, чем ячейка флэш-памяти NAND – 10 F 2 против 4 F 2 – [ неопределенно ] даже при использовании точно такого же изготовления полупроводникового устройства , и поэтому каждый транзистор, контакт и т. д. имеют точно такой же размер – поскольку для ячеек флэш-памяти NOR требуется отдельный металлический контакт для каждой ячейки. [138] [139]

Из-за последовательного соединения и удаления контактов словесной шины большая сетка ячеек флэш-памяти NAND будет занимать, возможно, только 60% площади эквивалентных ячеек NOR [140] (предполагая то же разрешение процесса CMOS , например, 130 нм , 90 нм или 65 нм). Разработчики флэш-памяти NAND поняли, что площадь чипа NAND, а значит, и стоимость, можно еще больше уменьшить, удалив внешнюю адресную и шинную схему данных. Вместо этого внешние устройства могли бы взаимодействовать с флэш-памятью NAND через последовательно доступные регистры команд и данных, которые бы внутренне извлекали и выводили необходимые данные. Такой выбор конструкции сделал невозможным произвольный доступ к флэш-памяти NAND, но целью флэш-памяти NAND была замена механических жестких дисков , а не замена ПЗУ.

Первые телефоны GSM и многие телефоны с функциями имели флэш-память NOR, из которой инструкции процессора могли выполняться напрямую в архитектуре исполнения на месте и обеспечивали короткое время загрузки. В смартфонах была принята флэш-память NAND, поскольку она имеет большую емкость хранения и более низкую стоимость, но приводит к более длительному времени загрузки, поскольку инструкции не могут быть выполнены из нее напрямую, и должны быть скопированы в память RAM перед выполнением. [141]

Длительность записи у SLC плавающего затвора NOR flash обычно равна или превышает таковую у NAND flash, в то время как MLC NOR и NAND flash имеют схожие показатели длительности. Приведены примеры циклических рейтингов длительности, приведенные в технических описаниях для NAND и NOR flash, а также в устройствах хранения, использующих флэш-память. [143]

Однако, применяя определенные алгоритмы и парадигмы проектирования, такие как выравнивание износа и избыточное выделение памяти , можно настроить долговечность системы хранения данных в соответствии с конкретными требованиями. [174]

Для расчета долговечности флэш-памяти NAND необходимо учитывать размер микросхемы памяти, тип памяти (например, SLC/MLC/TLC) и характер использования. Промышленная NAND и серверная NAND пользуются спросом из-за своей емкости, большей выносливости и надежности в чувствительных средах.

По мере увеличения количества бит на ячейку производительность и срок службы флэш-памяти NAND могут снижаться, увеличивая время случайного чтения до 100 мкс для TLC NAND, что в 4 раза превышает время, необходимое для SLC NAND, и в два раза превышает время, необходимое для MLC NAND, для случайного чтения. [74]

Из-за особых характеристик флэш-памяти ее лучше всего использовать либо с контроллером для выполнения выравнивания износа и исправления ошибок, либо со специально разработанными флэш-файловыми системами, которые распределяют записи по носителям и справляются с длительным временем стирания блоков флэш-памяти NOR. Основная концепция флэш-файловых систем заключается в следующем: когда флэш-хранилище должно быть обновлено, файловая система запишет новую копию измененных данных в новый блок, переназначит указатели файлов, а затем сотрет старый блок позже, когда у нее будет время.

На практике файловые системы флэш-памяти используются только для устройств с технологией памяти (MTD), которые представляют собой встроенную флэш-память без контроллера. Съемные карты флэш-памяти , твердотельные накопители, чипы eMMC / eUFS и USB-флеш-накопители имеют встроенные контроллеры для выравнивания износа и исправления ошибок, поэтому использование определенной файловой системы флэш-памяти может не принести пользы.

Несколько чипов часто объединяются в массив или складывают кристаллы для достижения более высокой емкости [175] для использования в потребительских электронных устройствах, таких как мультимедийные проигрыватели или GPS . Масштабирование (увеличение) емкости флэш-чипов обычно следовало закону Мура, поскольку они изготавливались с использованием многих из тех же методов и оборудования интегральных схем . С появлением 3D NAND масштабирование больше не обязательно связано с законом Мура, поскольку все меньшие транзисторы (ячейки) больше не используются.

Потребительские флэш-накопители обычно рекламируются с полезными размерами, выраженными как небольшая целая степень двойки (2, 4, 8 и т. д.) и условное обозначение мегабайт (МБ) или гигабайт (ГБ); например, 512 МБ, 8 ГБ. Это включает в себя SSD, продаваемые как замена жестким дискам, в соответствии с традиционными жесткими дисками , которые используют десятичные префиксы . [176] Таким образом, SSD, помеченный как «64 ГБ », имеет по крайней мере 64 × 1000 3 байта (64 ГБ). У большинства пользователей будет немного меньше емкости, чем эта, доступная для их файлов, из-за пространства, занимаемого метаданными файловой системы, и потому, что некоторые операционные системы сообщают емкость SSD, используя двоичные префиксы , которые несколько больше обычных префиксов.

Чипы флэш-памяти внутри них имеют размеры в строгих двоичных кратных, но фактическая общая емкость чипов не может быть использована на интерфейсе привода. Она значительно больше, чем заявленная емкость, чтобы обеспечить распределение записей ( выравнивание износа ), резервирование, коды исправления ошибок и другие метаданные, необходимые внутренней прошивке устройства.

В 2005 году Toshiba и SanDisk разработали чип флэш-памяти NAND, способный хранить 1 ГБ данных с использованием технологии многоуровневых ячеек (MLC), способной хранить два бита данных на ячейку. В сентябре 2005 года Samsung Electronics объявила о разработке первого в мире чипа емкостью 2 ГБ. [177]

В марте 2006 года Samsung анонсировала флэш-накопители емкостью 4 ГБ, по сути, того же порядка, что и меньшие жесткие диски для ноутбуков, а в сентябре 2006 года Samsung анонсировала чип емкостью 8 ГБ, произведенный с использованием 40-нм производственного процесса. [178] В январе 2008 года SanDisk объявила о выпуске своих карт MicroSDHC емкостью 16 ГБ и SDHC Plus емкостью 32 ГБ. [179] [180]

Более поздние флэш-накопители (по состоянию на 2012 год) имеют гораздо большую емкость, вмещая 64, 128 и 256 ГБ. [181]

Совместная разработка Intel и Micron позволит производить 32-слойные 3,5 терабайтные (ТБ [ требуется разъяснение ] ) флеш-накопители NAND и стандартные твердотельные накопители объемом 10 ТБ. Устройство включает 5 пакетов по 16 × 48 ГБ кристаллов TLC, используя конструкцию ячейки с плавающим затвором. [182]

Флэш-чипы по-прежнему производятся с емкостью менее или около 1 МБ (например, для BIOS-ROM и встроенных приложений).

В июле 2016 года Samsung анонсировала 4 ТБ [ необходимо разъяснение ] Samsung 850 EVO, который использует их 256 Гбит 48-слойную TLC 3D V-NAND. [183] В августе 2016 года Samsung анонсировала 32 ТБ 2,5-дюймовый SAS SSD на основе их 512 Гбит 64-слойной TLC 3D V-NAND. Кроме того, Samsung рассчитывает представить SSD с объемом хранения до 100 ТБ к 2020 году. [184]

Устройства флэш-памяти обычно намного быстрее считывают, чем записывают. [185] Производительность также зависит от качества контроллеров хранения, которые становятся более критичными, когда устройства частично заполнены. [ неопределенно ] [185] Даже если единственным изменением в производстве является усадка кристалла, отсутствие соответствующего контроллера может привести к снижению скорости. [186]

Последовательная флэш-память — это небольшая маломощная флэш-память, которая обеспечивает только последовательный доступ к данным — вместо того, чтобы адресовать отдельные байты, пользователь последовательно считывает или записывает большие непрерывные группы байтов в адресном пространстве. Последовательная периферийная интерфейсная шина (SPI) — это типичный протокол для доступа к устройству. При включении во встраиваемую систему последовательная флэш-память требует меньше проводов на печатной плате , чем параллельная флэш-память, поскольку она передает и получает данные по одному биту за раз. Это может позволить сократить пространство на плате, энергопотребление и общую стоимость системы.

Существует несколько причин, по которым последовательное устройство с меньшим количеством внешних контактов, чем параллельное устройство, может значительно снизить общую стоимость:

Существует два основных типа SPI flash. Первый тип характеризуется небольшими блоками и одним внутренним буфером блока SRAM, что позволяет считывать полный блок в буфер, частично изменять его и затем записывать обратно (например, Atmel AT45 DataFlash или Micron Technology Page Erase NOR Flash). Второй тип имеет более крупные сектора, где наименьшие сектора, обычно встречающиеся в этом типе SPI flash, составляют 4 кБ, но они могут быть и 64 кБ. Поскольку этот тип SPI flash не имеет внутреннего буфера SRAM, весь блок должен быть считан и изменен перед записью обратно, что делает его медленным в управлении. Однако второй тип дешевле первого и поэтому является хорошим выбором, когда приложение представляет собой затенение кода.

Эти два типа нелегко заменить, поскольку у них разная распиновка, а наборы команд несовместимы.

Большинство ПЛИС основаны на ячейках конфигурации SRAM и требуют внешнего устройства конфигурации, часто последовательного флэш-чипа, для перезагрузки потока битов конфигурации при каждом цикле питания. [187]

С ростом скорости современных ЦП параллельные флэш-устройства часто намного медленнее, чем шина памяти компьютера, к которому они подключены. Наоборот, современная SRAM обеспечивает время доступа менее 10 нс , в то время как DDR2 SDRAM обеспечивает время доступа менее 20 нс. Из-за этого часто желательно скопировать код, хранящийся во флэш-памяти, в ОЗУ; то есть код копируется из флэш-памяти в ОЗУ перед выполнением, чтобы ЦП мог получить к нему доступ на полной скорости. Прошивка устройства может храниться в последовательном флэш-чипе, а затем копироваться в SDRAM или SRAM при включении устройства. [188] Использование внешнего последовательного флэш-устройства вместо встроенной флэш-памяти устраняет необходимость в значительном компромиссе процесса (производственный процесс, который хорош для высокоскоростной логики, как правило, не подходит для флэш-памяти и наоборот). После того, как принято решение считывать прошивку как один большой блок, обычно добавляют сжатие, чтобы можно было использовать меньший флэш-чип. С 2005 года многие устройства используют последовательную флэш-память NOR, чтобы отказаться от параллельной флэш-памяти NOR для хранения прошивки. Типичные области применения последовательной флэш-памяти NOR включают хранение прошивки для жестких дисков , BIOS , дополнительных ПЗУ плат расширения , DSL-модемов и т. д.

Еще одно недавнее применение флэш-памяти — замена жестких дисков . Флэш-память не имеет механических ограничений и задержек жестких дисков, поэтому твердотельный накопитель (SSD) привлекателен с точки зрения скорости, шума, энергопотребления и надежности. Флэш-накопители набирают популярность в качестве вторичных устройств хранения данных для мобильных устройств; они также используются в качестве замены жестких дисков в высокопроизводительных настольных компьютерах и некоторых серверах с архитектурами RAID и SAN .

Остаются некоторые аспекты твердотельных накопителей на основе флэш-памяти, которые делают их непривлекательными. Стоимость за гигабайт флэш-памяти остается значительно выше, чем у жестких дисков. [189] Кроме того, флэш-память имеет конечное число циклов P/E ( программирование/стирание ), но это, похоже, в настоящее время находится под контролем, поскольку гарантии на твердотельные накопители на основе флэш-памяти приближаются к гарантиям современных жестких дисков. [190] Кроме того, удаленные файлы на твердотельных накопителях могут оставаться в течение неопределенного периода времени, прежде чем будут перезаписаны новыми данными; методы стирания или уничтожения или программное обеспечение, которые хорошо работают на магнитных жестких дисках, не оказывают влияния на твердотельные накопители, что ставит под угрозу безопасность и судебную экспертизу. Однако из-за так называемой команды TRIM , используемой большинством твердотельных накопителей, которая помечает логические адреса блоков, занятые удаленным файлом, как неиспользуемые для включения сбора мусора , программное обеспечение для восстановления данных не может восстановить файлы, удаленные с таких.

Для реляционных баз данных или других систем, требующих транзакций ACID , даже скромный объем флэш-памяти может обеспечить значительное ускорение по сравнению с массивами дисковых накопителей. [191]

В мае 2006 года Samsung Electronics анонсировала два ПК на базе флэш-памяти, Q1-SSD и Q30-SSD, которые, как ожидалось, поступят в продажу в июне 2006 года, оба из которых использовали твердотельные накопители объемом 32 ГБ и были изначально доступны только в Южной Корее . [192] Запуск Q1-SSD и Q30-SSD был отложен и, наконец, был отправлен в конце августа 2006 года. [193]

Первым доступным ПК на базе флэш-памяти стал Sony Vaio UX90, предварительный заказ на который был объявлен 27 июня 2006 года, а поставки в Японию начались 3 июля 2006 года с жестким диском флэш-памяти объемом 16 ГБ. [194] В конце сентября 2006 года Sony увеличила флэш-память в Vaio UX90 до 32 ГБ. [195]

Твердотельный накопитель был предложен в качестве опции с первым MacBook Air, представленным в 2008 году, а с 2010 года все модели поставлялись с SSD. Начиная с конца 2011 года, в рамках инициативы Intel Ultrabook , все большее количество ультратонких ноутбуков поставляются со стандартными SSD.

Существуют также гибридные технологии, такие как гибридный диск и ReadyBoost , которые пытаются объединить преимущества обеих технологий, используя флэш-память в качестве высокоскоростного энергонезависимого кэша для файлов на диске, которые часто используются, но редко изменяются, например, исполняемые файлы приложений и операционной системы.

На смартфонах в качестве устройств хранения файлов используются флэш-память NAND, например, eMMC и eUFS .

По состоянию на 2012 год [update]предпринимаются попытки использовать флэш-память в качестве основной компьютерной памяти, DRAM . [196]

Транзисторы с плавающим затвором в устройстве флэш-памяти удерживают заряд, который представляет данные. Этот заряд постепенно утекает с течением времени, что приводит к накоплению логических ошибок , также известных как « битовая гниль » или «битовое затухание». [197]

Неясно, как долго данные на флэш-памяти будут сохраняться в архивных условиях (т. е. при благоприятной температуре и влажности с редким доступом с профилактической перезаписью или без нее). Технические описания микроконтроллеров Atmel на основе флэш-памяти " ATmega " обычно обещают время хранения 20 лет при 85 °C (185 °F) и 100 лет при 25 °C (77 °F). [198]

Продолжительность хранения различается в зависимости от типа и модели флэш-накопителя. При подаче питания и бездействии заряд транзисторов, хранящих данные, регулярно обновляется прошивкой флэш -накопителя. [197] Способность сохранять данные различается в зависимости от флэш-накопителя из-за различий в прошивке, избыточности данных и алгоритмах исправления ошибок . [199]

В статье CMU от 2015 года говорится: «Современные флэш-устройства, не требующие обновления флэш-памяти, имеют типичный срок хранения 1 год при комнатной температуре». И это время хранения уменьшается экспоненциально с ростом температуры. Это явление можно смоделировать с помощью уравнения Аррениуса . [200] [201]

Некоторые ПЛИС основаны на ячейках флэш-конфигурации, которые используются непосредственно как (программируемые) переключатели для соединения внутренних элементов вместе, используя тот же тип транзистора с плавающим затвором, что и ячейки флэш-памяти в устройствах хранения данных. [187]

Один источник утверждает, что в 2008 году объем производства и продаж флэш-памяти составил около 9,1 млрд долларов США. Другие источники оценивают рынок флэш-памяти в размере более 20 млрд долларов США в 2006 году, что составляет более восьми процентов от общего рынка полупроводников и более 34 процентов от общего рынка полупроводниковой памяти. [202] В 2012 году рынок оценивался в 26,8 млрд долларов США. [203] Производство чипа флэш-памяти может занять до 10 недель. [204]

Ниже приведены крупнейшие производители флэш-памяти NAND по состоянию на второй квартал 2023 года. [205]

По состоянию на первый квартал 2022 года Samsung остается крупнейшим производителем флэш-памяти NAND. [208]

Помимо отдельных чипов флэш-памяти, флэш-память также встроена в чипы микроконтроллеров (MCU) и устройства «система на кристалле» (SoC). [225] Флэш-память встроена в чипы ARM , [225] которых было продано 150 миллиардов единиц по всему миру по состоянию на 2019 год [update], [226] и в программируемые устройства «система на кристалле» (PSoC), которые были проданы 1,1 миллиарда единиц по состоянию на 2012 год [update]. [227] Это составляет не менее 151,1 миллиарда чипов MCU и SoC со встроенной флэш-памятью, в дополнение к 45,4 миллиардам известных продаж отдельных чипов флэш-памяти по состоянию на 2015 год [update], что в общей сложности составляет не менее 196,5 миллиардов чипов, содержащих флэш-память.

Благодаря своей относительно простой структуре и высокому спросу на более высокую емкость, флэш-память NAND является наиболее агрессивно масштабируемой технологией среди электронных устройств . Жесткая конкуренция среди нескольких ведущих производителей только добавляет агрессивности в сокращении правила проектирования MOSFET с плавающим затвором или узла технологического процесса. [110] В то время как ожидаемый график сокращения составляет фактор два каждые три года в соответствии с первоначальной версией закона Мура , в случае флэш-памяти NAND он недавно был ускорен до фактора два каждые два года.

Поскольку размер элемента MOSFET ячеек флэш-памяти достигает минимального предела в 15–16 нм, дальнейшее увеличение плотности флэш-памяти будет обусловлено TLC (3 бита/ячейка) в сочетании с вертикальной укладкой плоскостей памяти NAND. Уменьшение выносливости и увеличение неисправимых ошибок битов, которые сопровождают уменьшение размера элемента, могут быть компенсированы улучшенными механизмами исправления ошибок. [233] Даже с этими достижениями может оказаться невозможным экономично масштабировать флэш-память до все меньших и меньших размеров, поскольку количество удерживающих электронов уменьшается. Многие многообещающие новые технологии (такие как FeRAM , MRAM , PMC , PCM , ReRAM и другие) исследуются и разрабатываются как возможные более масштабируемые замены для флэш-памяти. [234]

-память можно перепрограммировать до 100 раз.

предлагают работу с одним источником питания (от 2,7 В до 3,6 В), секторную архитектуру, встроенные алгоритмы, высокую производительность и гарантию на срок службы в 1 000 000 циклов программирования/стирания.

(PDF) , AN2209, архивировано из оригинала (PDF) 31 октября 2009 г.,

PSoC

... использует уникальный процесс Flash:

SONOS

проверки надежности показывают, что прогнозируемая частота сбоев при хранении данных намного меньше 1 PPM за 20 лет при 85 °C или за 100 лет при 25 °C

Поставки единиц продукции увеличились на 64% в 1999 году по сравнению с предыдущим годом, и, по прогнозам, увеличатся на 44% до 1,8 млрд единиц в 2000 году.