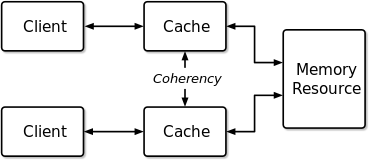

В компьютерной архитектуре согласованность кэша — это единообразие данных общих ресурсов, которые в конечном итоге сохраняются в нескольких локальных кэшах . Когда клиенты в системе поддерживают кэши общего ресурса памяти, могут возникнуть проблемы с некогерентными данными, что особенно характерно для процессоров в многопроцессорной системе.

На рисунке справа предположим, что у обоих клиентов есть кэшированная копия определенного блока памяти из предыдущего чтения. Предположим, что клиент внизу обновляет/изменяет этот блок памяти, клиент вверху может остаться с недействительным кешем памяти без какого-либо уведомления об изменении. Согласованность кэша предназначена для управления такими конфликтами путем поддержания согласованного представления значений данных в нескольких кэшах.

В многопроцессорной системе с общей памятью и отдельной кэш-памятью для каждого процессора можно иметь множество копий общих данных: одну копию в основной памяти и одну в локальном кэше каждого процессора, который их запросил. Когда одна из копий данных изменяется, другие копии должны отражать это изменение. Согласованность кэша — это дисциплина, которая гарантирует, что изменения в значениях общих операндов (данных) своевременно распространяются по всей системе. [1]

Ниже приведены требования к согласованности кэша: [2]

Теоретически когерентность может быть реализована при степени детализации загрузки/сохранения . Однако на практике это обычно выполняется с учетом детализации блоков кэша. [3]

Когерентность определяет поведение операций чтения и записи по одному адресу. [2]

Один тип данных, одновременно встречающихся в разных кэш-памятях, называется когерентностью кэша или, в некоторых системах, глобальной памятью.

В многопроцессорной системе учтите, что более чем один процессор кэширует копию ячейки памяти X. Для достижения согласованности кэша необходимы следующие условия: [4]

Вышеупомянутые условия удовлетворяют критериям распространения записи, необходимым для согласованности кэша. Однако их недостаточно, поскольку они не удовлетворяют условию сериализации транзакций. Чтобы лучше это проиллюстрировать, рассмотрим следующий пример:

Многопроцессорная система состоит из четырех процессоров — P1, P2, P3 и P4, каждый из которых содержит кэшированные копии общей переменной S , начальное значение которой равно 0. Процессор P1 изменяет значение S (в ее кэшированной копии) на 10, после чего процессор P2 меняет значение S в своей кэшированной копии на 20. Если мы обеспечим только распространение записи, то P3 и P4 обязательно увидят изменения, внесенные в S P1 и P2. Однако P3 может увидеть изменение, внесенное P1, после просмотра изменения, внесенного P2, и, следовательно, вернуть 10 при чтении в S. P4, с другой стороны, может видеть изменения, сделанные P1 и P2, в том порядке, в котором они были сделаны, и, следовательно, возвращать 20 при чтении в S. Процессоры P3 и P4 теперь имеют бессвязное представление о памяти.

Следовательно, чтобы обеспечить сериализацию транзакций и, следовательно, достичь согласованности кэша, наряду с двумя предыдущими, упомянутыми в этом разделе, должно быть выполнено следующее условие:

Альтернативное определение когерентной системы заключается в определении модели памяти последовательной согласованности : «когерентная система кэша должна выполнять загрузку и сохранение всех потоков в одной ячейке памяти в общем порядке, который соответствует программному порядку каждого потока». . [3] Таким образом, единственная разница между системой с когерентным кэшем и последовательно-согласованной системой заключается в количестве адресных ячеек, о которых говорится в определении (одна ячейка памяти для системы с когерентным кешем и все ячейки памяти для последовательно-согласованной системы).

Другое определение: «Мультипроцессор является согласованным кеш-памятью, если все записи в одну и ту же ячейку памяти выполняются в некотором последовательном порядке». [6]

Редко, но особенно в алгоритмах, когерентность может вместо этого относиться к локальности ссылки . Несколько копий одних и тех же данных могут одновременно существовать в разных кэшах, и если процессорам разрешено свободно обновлять свои собственные копии, это может привести к несогласованному представлению памяти.

Двумя наиболее распространенными механизмами обеспечения согласованности являются отслеживание и использование каталогов , каждый из которых имеет свои преимущества и недостатки. [7] Протоколы, основанные на отслеживании, обычно работают быстрее, если имеется достаточная полоса пропускания , поскольку все транзакции представляют собой запрос/ответ, видимый всеми процессорами. Недостатком является то, что отслеживание не масштабируется. Каждый запрос должен передаваться всем узлам системы. Это означает, что по мере увеличения размера системы размер шины (логической или физической) и пропускная способность, которую она обеспечивает, должны расти. С другой стороны, каталоги, как правило, имеют более длительные задержки (с 3-х прыжковыми запросами/пересылками/ответами), но используют гораздо меньшую пропускную способность, поскольку сообщения передаются «точка-точка», а не широковещательно. По этой причине многие более крупные системы (>64 процессоров) используют этот тип когерентности кэша.

Системы с распределенной общей памятью имитируют эти механизмы, пытаясь поддерживать согласованность между блоками памяти в слабосвязанных системах. [10]

Протоколы когерентности применяют когерентность кэша в многопроцессорных системах. Цель состоит в том, чтобы два клиента никогда не видели разные значения для одних и тех же общих данных.

Протокол должен реализовывать основные требования к согласованности. Он может быть адаптирован для целевой системы или приложения.

Протоколы также можно классифицировать как отслеживающие или основанные на каталогах. Как правило, ранние системы использовали протоколы на основе каталогов, где каталог отслеживал совместно используемые данные и участников. В протоколах отслеживания запросы транзакций (на чтение, запись или обновление) отправляются всем процессорам. Все процессоры отслеживают запрос и отвечают соответствующим образом.

Распространение записи в протоколах отслеживания может быть реализовано любым из следующих методов:

Если в конструкции протокола указано, что всякий раз, когда изменяется какая-либо копия общих данных, все остальные копии должны быть «обновлены», чтобы отразить это изменение, то это протокол обновления-записи. Если в конструкции указано, что запись в кэшированную копию любым процессором требует, чтобы другие процессоры отбросили или сделали недействительными свои кэшированные копии, то это протокол недействительности записи.

Однако масштабируемость является одним из недостатков широковещательных протоколов.

Для поддержания согласованности были разработаны различные модели и протоколы, такие как MSI , MESI (он же Illinois), MOSI , MOESI , MERSI , MESIF , протокол однократной записи , Synapse, Berkeley, Firefly и Dragon . [1] В 2011 году компания ARM Ltd предложила AMBA 4 ACE [11] для обеспечения согласованности в SoC . Спецификация AMBA CHI (Coherent Hub Interface) [12] от ARM Ltd , принадлежащая к группе спецификаций AMBA5, определяет интерфейсы для подключения полностью когерентных процессоров.