В вычислительной технике арифметико -логическое устройство ( АЛУ ) представляет собой комбинационную цифровую схему , которая выполняет арифметические и побитовые операции над целыми двоичными числами . [1] [2] Это отличается от устройства с плавающей точкой (FPU), которое работает с числами с плавающей точкой . Это фундаментальный строительный блок многих типов вычислительных схем, включая центральный процессор (ЦП) компьютеров, FPU и графические процессоры (GPU). [3]

Входы в АЛУ — это данные, над которыми нужно работать, называемые операндами , и код, указывающий операцию, которую нужно выполнить; выход АЛУ — это результат выполненной операции. Во многих конструкциях АЛУ также имеет входы или выходы состояния, или и то, и другое, которые передают информацию о предыдущей операции или текущей операции, соответственно, между АЛУ и внешними регистрами состояния .

ALU имеет множество входных и выходных сетей , которые являются электрическими проводниками , используемыми для передачи цифровых сигналов между ALU и внешними цепями. Когда ALU работает, внешние цепи подают сигналы на входы ALU, и в ответ ALU вырабатывает и передает сигналы внешним цепям через свои выходы.

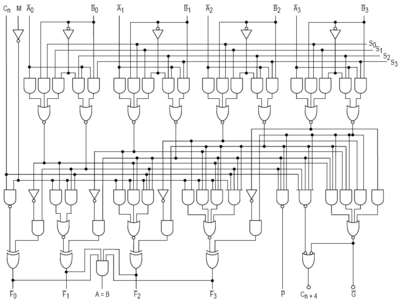

Базовый ALU имеет три параллельные шины данных , состоящие из двух входных операндов ( A и B ) и выходного результата ( Y ). Каждая шина данных представляет собой группу сигналов, которая передает одно двоичное целое число. Обычно ширина шин A, B и Y (количество сигналов, составляющих каждую шину) одинакова и соответствует собственному размеру слова внешней схемы (например, инкапсулирующего ЦП или другого процессора).

Входной код операции — это параллельная шина, которая передает в ALU код выбора операции, который является перечислимым значением , указывающим желаемую арифметическую или логическую операцию, которая должна быть выполнена ALU. Размер кода операции (его ширина шины) определяет максимальное количество различных операций, которые может выполнить ALU; например, четырехбитный код операции может указать до шестнадцати различных операций ALU. Как правило, код операции ALU — это не то же самое, что инструкция машинного языка , хотя в некоторых случаях он может быть напрямую закодирован как битовое поле внутри таких инструкций.

Выходы состояния — это различные индивидуальные сигналы, которые передают дополнительную информацию о результате текущей операции АЛУ. АЛУ общего назначения обычно имеют сигналы состояния, такие как:

Входы статуса позволяют сделать дополнительную информацию доступной для АЛУ при выполнении операции. Обычно это один бит "переноса", который является сохраненным переносом из предыдущей операции АЛУ.

ALU — это комбинационная логическая схема, то есть ее выходы будут изменяться асинхронно в ответ на изменения входов. В нормальном режиме работы стабильные сигналы подаются на все входы ALU и, когда проходит достаточно времени (известное как « задержка распространения ») для распространения сигналов по схеме ALU, результат работы ALU появляется на выходах ALU. Внешняя схема, подключенная к ALU, отвечает за обеспечение стабильности входных сигналов ALU на протяжении всей операции и за предоставление достаточного времени для распространения сигналов по схеме ALU перед выборкой выходов ALU.

В общем, внешняя схема управляет АЛУ, подавая сигналы на входы АЛУ. Обычно внешняя схема использует последовательную логику для генерации сигналов, которые управляют работой АЛУ. Внешняя последовательная логика задается тактовым сигналом достаточно низкой частоты, чтобы обеспечить достаточно времени для установления выходов АЛУ в наихудших условиях (т. е. условиях, приводящих к максимально возможной задержке распространения).

Например, ЦП начинает операцию сложения, направляя операнды из их источников (обычно регистры процессора ) на входы операндов АЛУ, одновременно применяя значение к входу кода операции АЛУ, который настраивает его на выполнение операции сложения. В то же время ЦП позволяет регистру назначения сохранять выход АЛУ (результирующую сумму от операции сложения) по завершении операции. Входные сигналы АЛУ, которые остаются стабильными до следующего такта, могут распространяться через АЛУ и в регистр назначения, пока ЦП ждет следующего такта. Когда приходит следующий такт, регистр назначения сохраняет результат АЛУ, и, поскольку операция АЛУ завершена, входы АЛУ могут быть настроены для следующей операции АЛУ.

Ряд основных арифметических и побитовых логических функций обычно поддерживаются АЛУ. Основные, общего назначения АЛУ обычно включают в свой репертуар следующие операции: [1] [2] [4]

Операции сдвига ALU заставляют операнд A (или B) сдвигаться влево или вправо (в зависимости от кода операции), а сдвинутый операнд появляется в Y. Простые ALU обычно могут сдвигать операнд только на одну битовую позицию, тогда как более сложные ALU используют барабанные сдвигатели , которые позволяют им сдвигать операнд на произвольное количество битов за одну операцию. Во всех операциях сдвига с одним битом бит, сдвинутый из операнда, появляется при переносе; значение бита, сдвинутого в операнд, зависит от типа сдвига.

После завершения каждой операции ALU выходные сигналы статуса ALU обычно сохраняются во внешних регистрах, чтобы сделать их доступными для будущих операций ALU (например, для реализации арифметики с многократной точностью ) и для управления условным переходом . Битовые регистры, в которых хранятся выходные сигналы статуса, часто в совокупности рассматриваются как один многобитовый регистр, который называется «регистром статуса» или «регистром кода условия».

В зависимости от выполняемой операции ALU некоторые биты регистра статуса могут быть изменены, а другие могут остаться неизмененными. Например, в побитовых логических операциях, таких как AND и OR, бит статуса переноса обычно не изменяется, поскольку он не имеет отношения к таким операциям.

В ЦП сохраненный сигнал переноса обычно подключается к сети переноса ALU. Это облегчает эффективное распространение переносов (которые могут представлять переносы сложения, заимствования вычитания или переполнения сдвига) при выполнении операций с множественной точностью, поскольку устраняет необходимость в программном управлении распространением переноса (через условное ветвление на основе бита состояния переноса).

В целочисленных арифметических вычислениях арифметика многократной точности — это алгоритм, который работает с целыми числами, размер которых больше размера слова ALU. Для этого алгоритм обрабатывает каждое целое число как упорядоченную коллекцию фрагментов размера ALU, расположенных от наиболее значимого (MS) к наименее значимому (LS) или наоборот. Например, в случае 8-битного ALU 24-битное целое число 0x123456будет обрабатываться как коллекция из трех 8-битных фрагментов: 0x12(MS), 0x34и 0x56(LS). Поскольку размер фрагмента точно соответствует размеру слова ALU, ALU может напрямую работать с этой «частью» операнда.

Алгоритм использует АЛУ для непосредственной работы с определенными фрагментами операнда и, таким образом, генерирует соответствующий фрагмент («частичный») результата с множественной точностью. Каждый частичный результат, когда он генерируется, записывается в связанную область хранения, которая была назначена для результата с множественной точностью. Этот процесс повторяется для всех фрагментов операнда, чтобы сгенерировать полную коллекцию частичных результатов, которая является результатом операции с множественной точностью.

В арифметических операциях (например, сложении, вычитании) алгоритм начинается с вызова операции ALU на фрагментах LS операндов, тем самым создавая как частичный LS, так и бит переноса. Алгоритм записывает частичный в назначенное хранилище, тогда как конечный автомат процессора обычно сохраняет бит переноса в регистре состояния ALU. Затем алгоритм переходит к следующему фрагменту коллекции каждого операнда и вызывает операцию ALU на этих фрагментах вместе с сохраненным битом переноса из предыдущей операции ALU, тем самым создавая еще один (более значимый) частичный и бит переноса. Как и прежде, бит переноса сохраняется в регистре состояния, а частичный записывается в назначенное хранилище. Этот процесс повторяется до тех пор, пока не будут обработаны все фрагменты операндов, что приводит к полному набору частичных в хранилище, которые составляют результат арифметики с множественной точностью.

В операциях сдвига с множественной точностью порядок обработки фрагментов операндов зависит от направления сдвига. В операциях сдвига влево фрагменты обрабатываются сначала LS, поскольку бит LS каждого парциального числа, который передается через сохраненный бит переноса, должен быть получен из бита MS ранее сдвинутого влево менее значимого операнда. Наоборот, операнды обрабатываются сначала MS в операциях сдвига вправо, поскольку бит MS каждого парциального числа должен быть получен из бита LS ранее сдвинутого вправо более значимого операнда.

В побитовых логических операциях (например, логическое И, логическое ИЛИ) фрагменты операндов могут обрабатываться в любом произвольном порядке, поскольку каждая часть зависит только от соответствующих фрагментов операндов (сохраненный бит переноса из предыдущей операции АЛУ игнорируется).

Хотя возможно спроектировать АЛУ, которые могут выполнять сложные функции, это обычно непрактично из-за результирующего увеличения сложности схемы, энергопотребления, задержки распространения, стоимости и размера. Следовательно, АЛУ обычно ограничиваются простыми функциями, которые могут выполняться на очень высоких скоростях (т. е. очень короткие задержки распространения), а более сложные функции являются обязанностью внешних схем. Например:

ALU обычно реализуется либо как отдельная интегральная схема (ИС), например, 74181 , либо как часть более сложной ИС. В последнем случае ALU обычно создается путем синтеза его из описания, написанного на VHDL , Verilog или каком-либо другом языке описания оборудования . Например, следующий код VHDL описывает очень простое 8-битное ALU:

сущность alu является портом ( -- соединения alu с внешней схемой: A : вход со знаком ( 7 вниз к 0 ); -- операнд A B : вход со знаком ( 7 вниз к 0 ); -- операнд B OP : вход без знака ( 2 вниз к 0 ); -- код операции Y : выход со знаком ( 7 вниз к 0 )); -- результат операции конец alu ; архитектура поведенческая alu - begin case OP - -- декодировать код операции и выполнить операцию: when "000" => Y <= A + B ; -- сложить when "001" => Y < = A - B ; -- вычесть when "010" => Y <= A - 1 ; -- уменьшить when "011" => Y <= A + 1 ; -- увеличить when "100" => Y <= not A ; -- дополнение до 1 when "101" => Y <= A и B ; -- побитовое И when "110" => Y <= A или B ; -- побитовое ИЛИ when "111" => Y <= A xor B ; -- побитовое исключающее ИЛИ when others => Y <= ( others => 'X' ); end case ; end behavioral ; Математик Джон фон Нейман предложил концепцию АЛУ в 1945 году в докладе об основах нового компьютера под названием EDVAC . [5]

Стоимость, размер и энергопотребление электронных схем были относительно высокими на протяжении всего младенчества Информационной эпохи . Следовательно, все ранние компьютеры имели последовательный АЛУ , который работал с одним битом данных за раз, хотя они часто представляли более широкий размер слова для программистов. Первым компьютером, который имел несколько параллельных дискретных однобитовых схем АЛУ, был Whirlwind I 1951 года , который использовал шестнадцать таких «математических единиц», чтобы иметь возможность работать с 16-битными словами.

В 1967 году Fairchild представила первое устройство типа ALU, реализованное в виде интегральной схемы, Fairchild 3800, состоящее из восьмибитного арифметического блока с аккумулятором. Он поддерживал только сложения и вычитания, но не логические функции. [6]

Вскоре появились полноценные интегральные схемы АЛУ, включая четырехбитные АЛУ, такие как Am2901 и 74181. Эти устройства обычно были способны на « бит-слайс », то есть имели сигналы «переноса вперед», которые облегчали использование нескольких взаимосвязанных чипов АЛУ для создания АЛУ с более широким размером слова. Эти устройства быстро стали популярными и широко использовались в мини-компьютерах бит-слайс.

Микропроцессоры начали появляться в начале 1970-х годов. Несмотря на то, что транзисторы стали меньше, иногда не хватало места на кристалле для АЛУ полной ширины слова, и, как следствие, некоторые ранние микропроцессоры использовали узкое АЛУ, которое требовало нескольких циклов на инструкцию машинного языка. Примером этого является популярный Zilog Z80 , который выполнял восьмибитные сложения с четырехбитным АЛУ. [7] Со временем геометрия транзисторов еще больше сжималась, следуя закону Мура , и стало возможным строить более широкие АЛУ на микропроцессорах.

Современные транзисторы интегральных схем (ИС) на порядок меньше, чем у ранних микропроцессоров, что позволяет устанавливать очень сложные АЛУ на ИС. Сегодня многие современные АЛУ имеют большую ширину слова и архитектурные усовершенствования, такие как барабанные сдвигатели и двоичные умножители , которые позволяют им выполнять за один такт операции, которые потребовали бы нескольких операций на более ранних АЛУ.

АЛУ могут быть реализованы в виде механических , электромеханических или электронных схем [8] [ проверка не удалась ] , и в последние годы были проведены исследования биологических АЛУ [9] [10] (например, на основе актина ). [11]