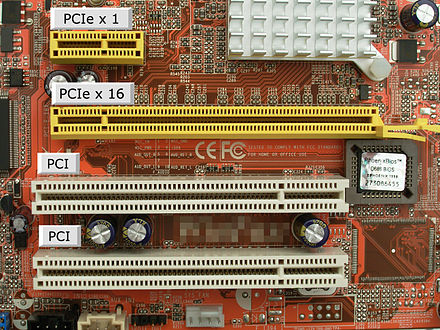

Peripheral Component Interconnect ( PCI ) [3] — это локальная компьютерная шина для подключения аппаратных устройств к компьютеру , которая является частью стандарта PCI Local Bus . Шина PCI поддерживает функции, обнаруженные на шине процессора , но в стандартизированном формате, который не зависит от собственной шины любого данного процессора . Устройства, подключенные к шине PCI, кажутся ведущему устройству шины подключенными непосредственно к его собственной шине и им назначаются адреса в адресном пространстве процессора . [4] Это параллельная шина, синхронизированная с одним тактовым генератором шины . Подключенные устройства могут иметь либо форму интегральной схемы , установленной на материнской плате (называемой планарным устройством в спецификации PCI), либо плату расширения , которая вставляется в слот. Локальная шина PCI была впервые реализована в IBM PC-совместимых компьютерах , где она заменила комбинацию нескольких медленных слотов Industry Standard Architecture (ISA) и одного быстрого слота VESA Local Bus (VLB) в качестве конфигурации шины. Впоследствии она была принята для других типов компьютеров. Типичные карты PCI, используемые в ПК, включают: сетевые карты , звуковые карты , модемы , дополнительные порты, такие как Universal Serial Bus ( USB ) или последовательный порт , карты ТВ-тюнера и хост-адаптеры жестких дисков . Видеокарты PCI заменили карты ISA и VLB, пока растущие потребности в пропускной способности не переросли возможности PCI. Предпочтительным интерфейсом для видеокарт затем стал Accelerated Graphics Port (AGP), надмножество PCI, прежде чем уступить место PCI Express. [5]

Первая версия PCI, которая появилась в розничных настольных компьютерах, представляла собой 32-битную шину, использующуюЧастота шины 33 МГц и5 В сигнализация, хотя стандарт PCI 1.0 предусматривал также 64-битный вариант. [6] Они имеют одну выемку на карте. Версия 2.0 стандарта PCI представила слоты 3,3 В, физически отличающиеся перевернутым физическим разъемом для предотвращения случайной вставки карт 5 В. Универсальные карты, которые могут работать с любым напряжением, имеют две выемки. Версия 2.1 стандарта PCI представила опциональную работу на частоте 66 МГц. Серверно-ориентированный вариант PCI, PCI Extended ( PCI-X ) работал на частотах до 133 МГц для PCI-X 1.0 и до 533 МГц для PCI-X 2.0. Внутренний разъем для карт ноутбуков, называемый Mini PCI , был представлен в версии 2.2 спецификации PCI. Шина PCI была также принята для внешнего стандарта разъема ноутбука — CardBus . [7] Первая спецификация PCI была разработана Intel , но последующая разработка стандарта стала обязанностью PCI Special Interest Group ( PCI-SIG ). [8]

PCI и PCI-X иногда называют либо параллельным PCI , либо обычным PCI [9], чтобы технологически отличить их от их более позднего преемника PCI Express , который принял последовательную архитектуру на основе полос. [10] [11] Расцвет PCI на рынке настольных компьютеров пришелся примерно на 1995–2005 годы. [10] PCI и PCI-X устарели для большинства целей и в значительной степени исчезли из многих других современных материнских плат с 2013 года; однако они все еще распространены на некоторых современных настольных компьютерах по состоянию на 2020 год [обновлять]в целях обратной совместимости и относительно низкой стоимости производства. Другое распространенное современное применение параллельного PCI — промышленные ПК , где многие специализированные карты расширения, используемые здесь, никогда не переходили на PCI Express, как и некоторые карты ISA. Многие виды устройств, ранее доступные на картах расширения PCI, теперь обычно интегрируются в материнские платы или доступны в версиях USB и PCI Express.

Работа над PCI началась в Intel Architecture Labs (IAL, также Architecture Development Lab) около 1990 г. Команда, состоящая в основном из инженеров IAL, определила архитектуру и разработала концептуальный набор микросхем и платформу (Saturn) в партнерстве с командами в настольных ПК-системах компании и подразделениях по производству базовой логики.

PCI был немедленно введен в использование в серверах, заменив архитектуру Micro Channel (MCA) и архитектуру Extended Industry Standard Architecture (EISA) в качестве предпочтительной шины расширения сервера. В обычных ПК PCI медленнее заменял VLB и не получил значительного проникновения на рынок до конца 1994 года во втором поколении ПК Pentium . К 1996 году VLB практически исчез, и производители приняли PCI даже для компьютеров Intel 80486 (486). [12] EISA продолжал использоваться вместе с PCI до 2000 года. Apple Computer приняла PCI для профессиональных компьютеров Power Macintosh (заменив NuBus ) в середине 1995 года, а потребительская линейка продуктов Performa (заменив LC Processor Direct Slot (PDS)) в середине 1996 года.

За пределами рынка серверов 64-битная версия простого PCI на практике оставалась редкостью [13] , хотя она использовалась, например, во всех (после iMac) компьютерах G3 и G4 Power Macintosh . [14]

Более поздние версии PCI добавили новые функции и улучшения производительности, включая стандарт 66 МГц 3,3 В и 133 МГц PCI-X , а также адаптацию сигналов PCI к другим форм-факторам. Как PCI-X 1.0b, так и PCI-X 2.0 обратно совместимы с некоторыми стандартами PCI. Эти версии использовались на серверном оборудовании, но потребительское оборудование ПК оставалось почти полностью 32-битным, 33 МГц и 5 вольт.

PCI-SIG представила последовательный PCI Express в 2004 году . С тех пор производители материнских плат включили все меньше слотов PCI в пользу нового стандарта. Многие новые материнские платы вообще не имеют слотов PCI, по состоянию на конец 2013 года. [ необходима цитата ]

PCI предоставляет отдельные адресные пространства памяти и портов ввода-вывода с отображением в памяти для семейства процессоров x86 , 64 и 32 бита соответственно. Адреса в этих адресных пространствах назначаются программным обеспечением. Третье адресное пространство, называемое PCI Configuration Space , которое использует фиксированную схему адресации, позволяет программному обеспечению определять объем памяти и адресное пространство ввода-вывода, необходимое каждому устройству. Каждое устройство может запрашивать до шести областей пространства памяти или пространства портов ввода-вывода (I/O) через свои регистры пространства конфигурации.

В типичной системе прошивка (или операционная система ) опрашивает все шины PCI во время запуска (через PCI Configuration Space ), чтобы узнать, какие устройства присутствуют и какие системные ресурсы (пространство памяти, пространство ввода-вывода, линии прерываний и т. д.) требуются каждому из них. Затем она выделяет ресурсы и сообщает каждому устройству, каково его распределение.

Пространство конфигурации PCI также содержит небольшое количество информации о типе устройства, которая помогает операционной системе выбирать для него драйверы устройств или, по крайней мере, вести диалог с пользователем о конфигурации системы.

Устройства могут иметь встроенную постоянную память (ПЗУ), содержащую исполняемый код для процессоров x86 или PA-RISC , драйвер Open Firmware или дополнительное ПЗУ . Они обычно необходимы для устройств, используемых во время запуска системы, до того, как драйверы устройств будут загружены операционной системой.

Кроме того, существуют таймеры задержки PCI , которые являются механизмом для устройств PCI Bus-Mastering, позволяющим им справедливо распределять шину PCI. «Справедливо» в данном случае означает, что устройства не будут использовать такую большую часть доступной полосы пропускания шины PCI, что другие устройства не смогут выполнить необходимую работу. Обратите внимание, что это не относится к PCI Express.

Это работает следующим образом: каждое устройство PCI, которое может работать в режиме bus-master, должно реализовать таймер, называемый Latency Timer, который ограничивает время, в течение которого устройство может удерживать шину PCI. Таймер запускается, когда устройство получает право владения шиной, и отсчитывает время со скоростью тактовой частоты PCI. Когда счетчик достигает нуля, устройство должно освободить шину. Если другие устройства не ждут права владения шиной, оно может просто снова захватить шину и передать больше данных. [17]

Устройства должны следовать протоколу, чтобы линии запроса прерывания (IRQ) могли совместно использоваться. Шина PCI включает четыре линии прерывания, INTA# — INTD#, все из которых доступны каждому устройству. До восьми устройств PCI совместно используют одну и ту же линию IRQ (INTINA# — INTINH#) в системах x86 с поддержкой APIC . Линии прерывания не подключены параллельно, как другие линии шины PCI. Положения линий прерывания чередуются между слотами, поэтому то, что одному устройству кажется линией INTA#, для следующего устройства является INTB#, а для следующего — INTC#. Устройства с одной функцией обычно используют свои INTA# для сигнализации прерывания, поэтому нагрузка на устройство распределяется достаточно равномерно по четырем доступным линиям прерывания. Это устраняет распространенную проблему совместного использования прерываний.

Отображение линий прерывания PCI на линии системного прерывания через хост-мост PCI зависит от реализации. Специфическая для платформы прошивка или код операционной системы должны знать это и устанавливать поле «линия прерывания» в пространстве конфигурации каждого устройства, указывающее, к какому IRQ оно подключено.

Линии прерываний PCI запускаются по уровню . Это было выбрано вместо запуска по фронту , чтобы получить преимущество при обслуживании общей линии прерываний, а также для надежности: прерывания, запускаемые по фронту, легко пропустить.

Более поздние версии спецификации PCI добавляют поддержку прерываний, сигнализируемых сообщениями . В этой системе устройство сигнализирует о своей потребности в обслуживании, выполняя запись в память, а не утверждая выделенную линию. Это снимает проблему нехватки линий прерываний. Даже если векторы прерываний по-прежнему являются общими, они не страдают от проблем совместного использования прерываний, запускаемых уровнем. Это также решает проблему маршрутизации, поскольку запись в память не изменяется непредсказуемым образом между устройством и хостом. Наконец, поскольку сигнализация сообщений является внутриполосной , это решает некоторые проблемы синхронизации, которые могут возникнуть с отправленными записями и внеполосными линиями прерываний.

PCI Express вообще не имеет физических линий прерывания. Он использует исключительно прерывания, сигнализируемые сообщениями.

Эти спецификации представляют собой наиболее распространенную версию PCI, используемую в обычных ПК:

Спецификация PCI также предусматривает опции для сигналов 3,3 В, 64-битной ширины шины и тактовой частоты 66 МГц, но они обычно не встречаются за пределами поддержки PCI-X на серверных материнских платах.

Арбитр шины PCI выполняет арбитраж шины между несколькими мастерами на шине PCI. На шине PCI может находиться любое количество мастеров шины, а также запросов на шину. Каждому мастеру шины выделяется одна пара сигналов запроса и предоставления.

Типичные карты PCI имеют один или два ключевых паза в зависимости от их сигнального напряжения. Карты, требующие 3,3 вольта, имеют пазы на расстоянии 56,21 мм от задней пластины карты; те, которым требуется 5 вольт, имеют пазы на расстоянии 104,41 мм от задней пластины. Это позволяет устанавливать карты только в слоты с напряжением, которое они поддерживают. «Универсальные карты», принимающие любое напряжение, имеют оба ключевых паза.

Разъем PCI определяется как имеющий 62 контакта на каждой стороне краевого разъема , но два или четыре из них заменены ключевыми выемками, поэтому карта имеет 60 или 58 контактов на каждой стороне. Сторона A относится к «стороне пайки», а сторона B относится к «стороне компонентов»: если держать карту разъемом вниз, вид на сторону A будет иметь заднюю пластину справа, тогда как вид на сторону B будет иметь заднюю пластину слева. Распиновка сторон B и A следующая, если смотреть вниз на разъем материнской платы (контакты A1 и B1 находятся ближе всего к задней пластине). [16] [18] [19]

64-битный PCI расширяет это за счет дополнительных 32 контактов с каждой стороны, которые обеспечивают AD[63:32], C/BE[7:4]#, сигнал четности PAR64, а также ряд контактов питания и заземления.

Большинство линий подключены к каждому слоту параллельно. Исключениями являются:

Примечания:

Большинство 32-битных карт PCI будут нормально работать в 64-битных слотах PCI-X, но тактовая частота шины будет ограничена тактовой частотой самой медленной карты, что является неотъемлемым ограничением общей топологии шины PCI. Например, когда периферийное устройство PCI 2.3, 66 МГц устанавливается в шину PCI-X, способную работать на частоте 133 МГц, вся объединительная плата шины будет ограничена частотой 66 МГц. Чтобы обойти это ограничение, многие материнские платы имеют две или более шин PCI/PCI-X, одна из которых предназначена для использования с высокоскоростными периферийными устройствами PCI-X, а другая — для периферийных устройств общего назначения.

Многие 64-битные карты PCI-X предназначены для работы в 32-битном режиме, если вставлены в более короткие 32-битные разъемы, с некоторой потерей производительности. [22] [23] Примером этого является 64-битная интерфейсная карта SCSI Adaptec 29160. [24] Однако некоторые 64-битные карты PCI-X не работают в стандартных 32-битных слотах PCI. [25] [ ненадежный источник? ]

Установка 64-битной карты PCI-X в 32-битный слот оставит 64-битную часть краевого разъема карты неподключенной и нависающей. Для этого необходимо, чтобы никакие компоненты материнской платы не были расположены таким образом, чтобы механически препятствовать нависающей части краевого разъема карты.

Высота кронштейнов PCI:

Длина карты PCI (стандартный кронштейн и 3,3 В): [28]

Длина карты PCI (низкопрофильный кронштейн и 3,3 В): [29]

Mini PCI был добавлен в PCI версии 2.2 для использования в ноутбуках и некоторых маршрутизаторах; [ требуется цитата ] он использует 32-битную шину 33 МГц с силовыми соединениями (только 3,3 В; 5 В ограничено 100 мА) и поддержкой управления шиной и DMA . Стандартный размер карт Mini PCI составляет примерно четверть от их полноразмерных аналогов. Доступ к карте снаружи корпуса отсутствует, в отличие от настольных карт PCI с кронштейнами, несущими разъемы. Это ограничивает виды функций, которые может выполнять карта Mini PCI.

Было разработано множество устройств Mini PCI, таких как Wi-Fi , Fast Ethernet , Bluetooth , модемы (часто Winmodems ), звуковые карты , криптографические ускорители , контроллеры SCSI , IDE – ATA , SATA и комбинированные карты. Карты Mini PCI можно использовать с обычным оборудованием, оснащенным PCI, с помощью преобразователей Mini PCI-to-PCI . Mini PCI был заменен гораздо более узкой картой PCI Express Mini Card

Мини-карты PCI имеют максимальную потребляемую мощность 2 Вт, что ограничивает функциональность, которую можно реализовать в этом форм-факторе. Они также должны поддерживать сигнал PCI CLKRUN#, используемый для запуска и остановки тактовой частоты PCI в целях управления питанием.

Существует три форм-фактора карт : карты типа I, типа II и типа III. Разъем карты, используемый для каждого типа, включает: Тип I и II используют 100-контактный стековый разъем, в то время как Тип III использует 124-контактный краевой разъем, т. е. разъем для Типов I и II отличается от разъема для Типа III, где разъем находится на краю карты, как в случае с SO-DIMM . Дополнительные 24 контакта обеспечивают дополнительные сигналы, необходимые для маршрутизации ввода -вывода обратно через системный разъем (аудио, AC-Link , LAN , интерфейс телефонной линии). Карты типа II имеют установленные разъемы RJ11 и RJ45. Эти карты должны быть расположены на краю компьютера или док-станции, чтобы порты RJ11 и RJ45 можно было установить для внешнего доступа.

Mini PCI отличается от 144-контактного Micro PCI. [30]

Трафик шины PCI состоит из серии транзакций шины PCI. Каждая транзакция состоит из адресной фазы, за которой следует одна или несколько фаз данных . Направление фаз данных может быть от инициатора к цели (транзакция записи) или наоборот (транзакция чтения), но все фазы данных должны быть в одном направлении. Любая из сторон может приостановить или остановить фазы данных в любой момент. (Одним из распространенных примеров является низкопроизводительное устройство PCI, которое не поддерживает пакетные транзакции и всегда останавливает транзакцию после первой фазы данных.)

Любое устройство PCI может инициировать транзакцию. Сначала оно должно запросить разрешение у арбитра шины PCI на материнской плате. Арбитр предоставляет разрешение одному из запрашивающих устройств. Инициатор начинает фазу адреса, транслируя 32-битный адрес и 4-битный код команды, затем ждет ответа от цели. Все остальные устройства проверяют этот адрес, и одно из них отвечает через несколько циклов.

64-битная адресация выполняется с использованием двухэтапной адресной фазы. Инициатор транслирует младшие 32 бита адреса, сопровождаемые специальным кодом команды «двойного адресного цикла». Устройства, не поддерживающие 64-битную адресацию, могут просто не ответить на этот код команды. В следующем цикле инициатор передает старшие 32 бита адреса, плюс реальный код команды. С этого момента транзакция работает идентично. Для обеспечения совместимости с 32-битными устройствами PCI запрещено использовать двойной адресный цикл, если в этом нет необходимости, т. е. если старшие биты адреса все равны нулю.

В то время как шина PCI передает 32 бита на фазу данных, инициатор передает 4 сигнала разрешения активного младшего байта, указывающих, какие 8-битные байты следует считать значимыми. В частности, запись должна влиять только на разрешенные байты в целевом устройстве PCI. Они не имеют большого значения для чтения памяти, но чтение ввода-вывода может иметь побочные эффекты. Стандарт PCI явно допускает фазу данных без разрешенных байтов, которая должна вести себя как no-op.

PCI имеет три адресных пространства: память, адрес ввода-вывода и конфигурация.

Адреса памяти имеют размер 32 бита (опционально 64 бита), поддерживают кэширование и могут обрабатывать пакетные транзакции.

Адреса ввода-вывода предназначены для совместимости с адресным пространством порта ввода-вывода архитектуры Intel x86 . Хотя спецификация шины PCI допускает пакетные транзакции в любом адресном пространстве, большинство устройств поддерживают ее только для адресов памяти, а не для ввода-вывода.

Наконец, пространство конфигурации PCI обеспечивает доступ к 256 байтам специальных регистров конфигурации на каждое устройство PCI. Каждый слот PCI получает свой собственный диапазон адресов пространства конфигурации. Регистры используются для настройки памяти устройств и диапазонов адресов ввода-вывода, на которые они должны реагировать от инициаторов транзакций. Когда компьютер включается впервые, все устройства PCI реагируют только на доступ к своему пространству конфигурации. BIOS компьютера сканирует устройства и назначает им диапазоны адресов памяти и ввода-вывода.

Если адрес не заявлен ни одним устройством, фаза адреса инициатора транзакции прервется по тайм-ауту, что приведет к прерыванию операции инициатором. В случае чтения принято предоставлять все единицы для значения считанных данных (0xFFFFFFFF) в этом случае. Поэтому устройства PCI обычно пытаются избегать использования значения все единицы в важных регистрах состояния, чтобы такая ошибка могла быть легко обнаружена программным обеспечением.

Существует 16 возможных 4-битных кодов команд, и 12 из них назначены. За исключением уникального цикла двойного адреса, младший бит кода команды указывает, являются ли следующие фазы данных чтением (данные, отправленные от цели к инициатору) или записью (данные, отправленные от инициатора к цели). Целевые устройства PCI должны проверять код команды, а также адрес и не отвечать на адресные фазы, которые указывают неподдерживаемый код команды.

Команды, которые ссылаются на строки кэша, зависят от правильной настройки регистра размера строки кэша пространства конфигурации PCI ; их нельзя использовать, пока это не будет сделано.

Вскоре после обнародования спецификации PCI было обнаружено, что длительные транзакции некоторых устройств из-за медленных подтверждений, длинных пакетов данных или некоторой комбинации могут вызвать опустошение или переполнение буфера в других устройствах. Рекомендации по времени отдельных фаз в Revision 2.0 стали обязательными в revision 2.1: [32] : 3

Кроме того, начиная с версии 2.1, все инициаторы, способные разрывать более двух фаз данных, должны реализовывать программируемый таймер задержки. Таймер начинает отсчет тактов, когда начинается транзакция (инициатор утверждает FRAME#). Если таймер истек, а арбитр удалил GNT#, то инициатор должен завершить транзакцию при следующей законной возможности. Обычно это следующая фаза данных, но транзакции Memory Write и Invalidate должны продолжаться до конца строки кэша.

Устройства, неспособные соответствовать этим временным ограничениям, должны использовать комбинацию отправленных записей (для записей в память) и отложенных транзакций (для других записей и всех чтений). В отложенной транзакции цель записывает транзакцию (включая данные записи) внутренне и прерывает (устанавливает STOP# вместо TRDY#) первую фазу данных. Инициатор должен повторить точно такую же транзакцию позже. Тем временем цель внутренне выполняет транзакцию и ждет повторной транзакции. Когда повторная транзакция видна, буферизованный результат доставляется.

Устройство может быть целью других транзакций при завершении одной отложенной транзакции; оно должно запомнить тип транзакции, адрес, выбор байтов и (в случае записи) значение данных и завершить только правильную транзакцию.

Если у цели есть ограничение на количество отложенных транзакций, которые она может записать внутренне (простые цели могут устанавливать ограничение в 1), она заставит эти транзакции повторить попытку, не записывая их. Они будут обработаны, когда текущая отложенная транзакция будет завершена. Если два инициатора попытаются выполнить одну и ту же транзакцию, отложенная транзакция, начатая одним, может доставить свой результат другому; это безвредно.

Цель отказывается от отложенной транзакции, когда повторная попытка успешно доставляет буферизованный результат, шина сбрасывается или когда 2 15 =32768 тактов (приблизительно 1 мс) истекает без повторной попытки. Последнее никогда не должно происходить при нормальной работе, но это предотвращает тупик всей шины, если один инициатор сбрасывается или выходит из строя.

Стандарт PCI позволяет подключать несколько независимых шин PCI с помощью шинных мостов, которые будут пересылать операции с одной шины на другую при необходимости. Хотя PCI, как правило, не использует много шинных мостов, системы PCI Express используют много мостов PCI-PCI, обычно называемых корневым портом PCI Express ; каждый слот PCI Express представляется отдельной шиной, подключенной мостом к другим. Мост хоста PCI (обычно северный мост на платформах x86) соединяет ЦП, основную память и шину PCI. [33]

Обычно, когда шинный мост видит транзакцию на одной шине, которую необходимо переслать на другую, исходная транзакция должна ждать, пока пересланная транзакция не завершится, прежде чем результат будет готов. Одно заметное исключение возникает в случае записи в память. Здесь мост может записывать данные записи внутренне (если у него есть место) и сигнализировать о завершении записи до того, как пересланная запись будет завершена. Или, на самом деле, до того, как она начнется. Такие «отправленные, но еще не полученные» записи называются «отправленными записями» по аналогии с почтовым сообщением. Хотя они предлагают большие возможности для повышения производительности, правила, регулирующие то, что допустимо, довольно сложны. [34]

Стандарт PCI позволяет мостам шины преобразовывать несколько транзакций шины в одну большую транзакцию в определенных ситуациях. Это может повысить эффективность шины PCI.

Транзакции записи на последовательные адреса могут быть объединены в более длинную запись всплеска, пока порядок доступа в всплеске такой же, как и порядок исходных записей. Допустимо вставлять дополнительные фазы данных со всеми выключенными разрешениями байтов, если записи почти последовательны.

Несколько записей в непересекающиеся части одного и того же слова могут быть объединены в одну запись с несколькими байтовыми разрешениями. В этом случае записи, представленные шинному мосту в определенном порядке, объединяются, так что они происходят одновременно при пересылке.

Несколько записей в один и тот же байт или байты не могут быть объединены, например, путем выполнения только второй записи и пропуска первой записи, которая была перезаписана. Это связано с тем, что спецификация PCI допускает побочные эффекты записи.

Транзакции шины PCI контролируются пятью основными сигналами управления, два из которых управляются инициатором транзакции (FRAME# и IRDY#), а три управляются целью (DEVSEL#, TRDY# и STOP#). [6] Есть два дополнительных арбитражных сигнала (REQ# и GNT#), которые используются для получения разрешения на инициирование транзакции. [6] Все они являются активно-низкими , что означает, что активное или утвержденное состояние представляет собой низкое напряжение . Подтягивающие резисторы на материнской плате гарантируют, что они останутся высокими (неактивными или неутвержденными ), если не управляются каким-либо устройством, но шина PCI не зависит от резисторов для изменения уровня сигнала; все устройства управляют сигналами на высоком уровне в течение одного цикла, прежде чем прекратить управлять сигналами.

Все сигналы шины PCI опрашиваются по переднему фронту тактового сигнала. Сигналы номинально изменяются по заднему фронту тактового сигнала, давая каждому устройству PCI примерно половину тактового цикла, чтобы решить, как реагировать на сигналы, которые оно наблюдает по переднему фронту, и половину тактового цикла, чтобы передать свой ответ другому устройству.

Шина PCI требует, чтобы каждый раз, когда устройство, управляющее сигналом шины PCI, изменялось, между моментом, когда одно устройство прекращает управлять сигналом, и моментом, когда другое устройство начинает его, должен пройти один цикл оборота . Без этого может быть период, когда оба устройства управляют сигналом, что будет мешать работе шины.

Сочетание этого оборотного цикла и требования управлять линией управления на высоком уровне в течение одного цикла перед прекращением управления означает, что каждая из основных линий управления должна быть на высоком уровне в течение как минимум двух циклов при смене владельцев. Протокол шины PCI разработан таким образом, что это редко является ограничением; только в нескольких особых случаях (особенно быстрые встречные транзакции) необходимо вставить дополнительную задержку для выполнения этого требования.

Любое устройство на шине PCI, способное выступать в качестве мастера шины, может инициировать транзакцию с любым другим устройством. Чтобы гарантировать, что одновременно инициируется только одна транзакция, каждый мастер должен сначала дождаться сигнала предоставления шины, GNT#, от арбитра, расположенного на материнской плате. Каждое устройство имеет отдельную линию запроса REQ#, которая запрашивает шину, но арбитр может «припарковать» сигнал предоставления шины на любом устройстве, если нет текущих запросов.

Арбитр может удалить GNT# в любое время. Устройство, которое теряет GNT#, может завершить свою текущую транзакцию, но не может начать ее (подтвердив FRAME#), если только оно не увидит, что GNT# подтвердил цикл до его начала.

Арбитр также может предоставить GNT# в любое время, в том числе во время транзакции другого мастера. Во время транзакции либо FRAME#, либо IRDY#, либо оба активны; когда оба неактивны, шина простаивает. Устройство может инициировать транзакцию в любое время, когда активен GNT# и шина простаивает.

Транзакция шины PCI начинается с фазы адреса . Инициатор (обычно чипсет ), видя, что у него есть GNT# и шина свободна, передает целевой адрес на линии AD[31:0], соответствующую команду (например, чтение памяти или запись ввода-вывода) на линии C/BE[3:0]# и устанавливает FRAME# на низкий уровень.

Каждое другое устройство проверяет адрес и команду и решает, отвечать ли ему как цели, утверждая DEVSEL#. Устройство должно ответить, утверждая DEVSEL# в течение 3 циклов. Устройства, которые обещают ответить в течение 1 или 2 циклов, называются имеющими "быстрый DEVSEL" или "средний DEVSEL" соответственно. (На самом деле время ответа составляет 2,5 цикла, поскольку устройства PCI должны передавать все сигналы на полцикла раньше, чтобы их можно было получить на три цикла позже.)

Устройство должно зафиксировать адрес на первом цикле; инициатор должен удалить адрес и команду из шины на следующем цикле, даже до получения ответа DEVSEL#. Дополнительное время доступно только для интерпретации адреса и команды после их захвата.

На пятом цикле адресной фазы (или раньше, если все остальные устройства имеют средний DEVSEL или быстрее) для некоторых диапазонов адресов разрешено всеобъемлющее "вычитающее декодирование". Это обычно используется мостом шины ISA для адресов в пределах его диапазона (24 бита для памяти и 16 бит для ввода-вывода).

На шестом цикле, если ответа не было, инициатор может прервать транзакцию, сняв FRAME#. Это известно как прекращение главного прерывания , и в этом случае мосты шины PCI обычно возвращают данные «все единицы» (0xFFFFFFFF). Поэтому устройства PCI, как правило, проектируются так, чтобы избегать использования значения «все единицы» в важных регистрах состояния, чтобы такая ошибка могла быть легко обнаружена программным обеспечением.

Примечания:

На переднем фронте такта 0 инициатор наблюдает FRAME# и IRDY# как высокие, а GNT# как низкие, поэтому он управляет адресом, командой и утверждает FRAME# вовремя для переднего фронта такта 1. Цели фиксируют адрес и начинают его декодировать. Они могут ответить DEVSEL# вовремя для такта 2 (быстрый DEVSEL), 3 (средний) или 4 (медленный). Устройства субтрактивного декодирования, не видя другого ответа на такте 4, могут ответить на такте 5. Если мастер не видит ответа на такте 5, он завершит транзакцию и удалит FRAME# на такте 6.

TRDY# и STOP# неактивны (высокий уровень) во время адресной фазы. Инициатор может активировать IRDY#, как только он будет готов к передаче данных, что теоретически может произойти сразу после такта 2.

Чтобы разрешить 64-битную адресацию, мастер будет представлять адрес в течение двух последовательных циклов. Сначала он отправляет младшие биты адреса со специальной командой "dual-cycle address" на C/BE[3:0]#. В следующем цикле он отправляет старшие биты адреса и фактическую команду. Двойные циклы адреса запрещены, если старшие биты адреса равны нулю, поэтому устройства, не поддерживающие 64-битную адресацию, могут просто не отвечать на команды двойного цикла.

_ 0_ 1_ 2_ 3_ 4_ 5_ 6_ КЛК _/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ ___ GNT# \___/XXXXXXXXXXXXXXXXXXXXXXXXXXX _______ РАМКА# \_______________________ ___ ___ AD[31:0] -------<___X___>--------------- (Низкие, затем высокие биты) ___ ___ _______________ C/BE[3:0]# -------<___X___X_______________ (DAC, затем фактическая команда) ___________________________ ДЕВСЕЛ# \___\___\___\___ Быстро Средне Медленно _ _ _ _ _ _ _ _ КЛК _/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ 0 1 2 3 4 5 6

Адреса для доступа к пространству конфигурации PCI используют специальное декодирование. Для них младшие адресные линии указывают смещение нужного регистра конфигурации PCI, а старшие адресные линии игнорируются. Вместо этого дополнительный адресный сигнал, вход IDSEL, должен быть высоким, прежде чем устройство сможет установить DEVSEL#. Каждый слот подключает отдельную старшую адресную линию к выводу IDSEL и выбирается с помощью прямого кодирования на старших адресных линиях.

После адресной фазы (в частности, начиная с цикла, когда DEVSEL# переходит на низкий уровень) следует пакет из одной или нескольких фаз данных . Во всех случаях инициатор управляет сигналами выбора активного низкого байта на линиях C/BE[3:0]#, но данные на AD[31:0] могут управляться инициатором (в случае записи) или целью (в случае чтения).

Во время фаз данных линии C/BE[3:0]# интерпретируются как активные-низкие байтовые разрешения . В случае записи, утвержденные сигналы указывают, какие из четырех байтов на шине AD должны быть записаны в адресное место. В случае чтения, они указывают, какие байты интересуют инициатора. Для чтения всегда допустимо игнорировать сигналы байтовых разрешений и просто возвращать все 32 бита; для того, чтобы всегда возвращать 32 допустимых бита, требуются ресурсы кэшируемой памяти. Байтовые разрешения в основном полезны для доступа к пространству ввода-вывода, где чтение имеет побочные эффекты.

Фаза данных со всеми четырьмя деактивированными линиями C/BE# явно разрешена стандартом PCI и не должна оказывать никакого влияния на цель, кроме перемещения адреса в выполняемом пакетном доступе.

Фаза данных продолжается до тех пор, пока обе стороны не будут готовы завершить передачу и перейти к следующей фазе данных. Инициатор утверждает IRDY# ( готовность инициатора ), когда ему больше не нужно ждать, в то время как цель утверждает TRDY# ( готовность цели ). Какая бы сторона ни предоставляла данные, она должна запустить их на шине AD, прежде чем утверждать свой сигнал готовности.

После того, как один из участников утверждает свой сигнал готовности, он не может стать неготовым или иным образом изменить свои сигналы управления до конца фазы данных. Получатель данных должен защелкивать шину AD каждый цикл, пока не увидит, что оба IRDY# и TRDY# утверждены, что отмечает конец текущей фазы данных и указывает, что только что защелкнутые данные являются словом для передачи.

Для поддержания полной пакетной скорости отправитель данных затем получает половину тактового цикла после того, как оба сигнала IRDY# и TRDY# были установлены, чтобы передать следующее слово на шину AD.

0_ 1_ 2_ 3_ 4_ 5_ 6_ 7_ 8_ 9_ КЛК _/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ ___ _______ ___ ___ ___ AD[31:0] ---<___XXXXXXXXX_______XXXXX___X___X___ (Если запись) ___ ___ _______ ___ ___ AD[31:0] ---<___>~~~<XXXXXXXXXX___X_______X___X___ (Если прочитано) ___ _______________ _______ ___ ___ C/BE[3:0]# ---<___X_____X_______X___X___ (Всегда должно быть действительным) _______________ | ___ | | | IRDY# х \_______/ х \___________ ___________________ | | | | TRDY# xx \___________________ ___________ | | | | ДЕВСЕЛ# \___________________________ ___ | | | | РАМКА# \___________________________________ _ _ _ _ _ |_ _ |_ |_ |_ КЛК _/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ 0 1 2 3 4 5 6 7 8 9

Это продолжает цикл адреса, показанный выше, предполагая один цикл адреса со средним DEVSEL, поэтому цель отвечает вовремя для такта 3. Однако в это время ни одна из сторон не готова передавать данные. Для такта 4 инициатор готов, но цель нет. На такте 5 оба готовы, и происходит передача данных (как указано вертикальными линиями). Для такта 6 цель готова к передаче, но инициатор нет. На такте 7 инициатор становится готовым, и данные передаются. Для тактов 8 и 9 обе стороны остаются готовыми к передаче данных, и данные передаются с максимально возможной скоростью (32 бита за такт).

В случае чтения тактовый сигнал 2 зарезервирован для реверсирования шины AD, поэтому целевому устройству не разрешается передавать данные по шине, даже если оно поддерживает быстрый DEVSEL.

Целевой объект, поддерживающий быстрый DEVSEL, теоретически может начать отвечать на чтение в цикле после представления адреса. Однако этот цикл зарезервирован для оборота шины AD. Таким образом, целевой объект может не управлять шиной AD (и, следовательно, не может утверждать TRDY#) во втором цикле транзакции. Большинство целевых объектов не будут такими быстрыми и не будут нуждаться в какой-либо специальной логике для обеспечения этого условия.

Любая из сторон может запросить окончание пакета после текущей фазы данных. Простые устройства PCI, не поддерживающие пакеты из нескольких слов, всегда будут запрашивать это немедленно. Даже устройства, поддерживающие пакеты, будут иметь некоторые ограничения на максимальную длину, которую они могут поддерживать, например, конец адресуемой памяти.

Инициатор может пометить любую фазу данных как последнюю в транзакции, сняв FRAME# одновременно с тем, как он устанавливает IRDY#. Цикл после того, как цель устанавливает TRDY#, завершает окончательную передачу данных, обе стороны снимают свои соответствующие сигналы RDY#, и шина снова простаивает. Мастер не может снять FRAME# до установки IRDY#, и не может снять FRAME# во время ожидания, с установленным IRDY#, пока цель не подтвердит TRDY#.

Единственным незначительным исключением является прекращение работы главного устройства , когда ни одна цель не отвечает DEVSEL#. Очевидно, что в таком случае бессмысленно ждать TRDY#. Однако даже в этом случае главный узел должен установить IRDY# по крайней мере на один цикл после снятия FRAME#. (Обычно главный узел устанавливает IRDY# до получения DEVSEL#, поэтому он должен просто удерживать IRDY# установленным на один цикл дольше.) Это необходимо для того, чтобы гарантировать соблюдение правил синхронизации поворота шины на линии FRAME#.

Цель запрашивает у инициатора завершение пакета, утверждая STOP#. Затем инициатор завершит транзакцию, сняв FRAME# при следующей легальной возможности; если он захочет передать больше данных, он продолжит в отдельной транзакции. У цели есть несколько способов сделать это:

Инициатору всегда потребуется не менее одного цикла, чтобы заметить запрос на отключение, инициированный целью, и ответить деактивацией FRAME#. Есть два подслучая, которые занимают одинаковое количество времени, но один требует дополнительной фазы данных:

Если инициатор завершает пакет в то же время, когда цель запрашивает отключение, дополнительный цикл шины не выполняется.

Для доступа к пространству памяти слова в пакете могут быть доступны в нескольких порядках. Ненужные младшие биты адреса AD[1:0] используются для передачи запрошенного инициатором порядка. Целевой объект, который не поддерживает определенный порядок, должен завершить пакет после первого слова. Некоторые из этих порядков зависят от размера строки кэша, который настраивается на всех устройствах PCI.

Если начальное смещение внутри строки кэша равно нулю, все эти режимы приводятся к одному и тому же порядку.

Режимы переключения строки кэша и переноса строки кэша — это две формы выборки строки кэша с критическим словом-сначала. Режим переключения выполняет операцию XOR над предоставленным адресом с увеличивающимся счетчиком. Это собственный порядок для процессоров Intel 486 и Pentium. Его преимущество в том, что для его реализации не требуется знать размер строки кэша.

Версия PCI 2.1 отменила режим переключения и добавила режим переноса строки кэша, [32] : 2 , где выборка выполняется линейно, переносясь в конце каждой строки кэша. Когда одна строка кэша полностью извлечена, выборка переходит к начальному смещению в следующей строке кэша.

Большинство устройств PCI поддерживают только ограниченный диапазон типичных размеров строк кэша; если размер строки кэша запрограммирован на неожиданное значение, они принудительно осуществляют доступ по одному слову.

PCI также поддерживает пакетный доступ к вводу-выводу и пространству конфигурации, но поддерживается только линейный режим. (Это используется редко и может быть неисправно в некоторых устройствах; они могут не поддерживать его, но и не обеспечивать должным образом однословный доступ.)

Это максимально возможная скорость четырехсловной записи, завершаемая ведущим устройством:

0_ 1_ 2_ 3_ 4_ 5_ 6_ 7_ КЛК _/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \ ___ ___ ___ ___ ___ AD[31:0] ---<___X___X___X___X___>---<___> ___ ___ ___ ___ ___ С/БЭ[3:0]# ---<___X___X___X___X___>---<___> | | | | ___ IRDY# ^^^^^^^^^\______________/ ^^^^^ | | | | ___ TRDY# ^^^^^^^^\______________/ ^^^^^ | | | | ___ ДЕВСЕЛ# ^^^^^^^^^\______________/ ^^^^^ ___ | | | ___ КАДР# \_______________/ | ^^^^\____ _ _ |_ |_ |_ |_ _ _ КЛК _/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \ 0 1 2 3 4 5 6 7

На фронте тактового сигнала 1 инициатор начинает транзакцию, управляя адресом, командой и утверждая FRAME#. Остальные сигналы находятся в состоянии ожидания (обозначены ^^^), подтянутые подтягивающими резисторами материнской платы. Это может быть их циклом поворота. На цикле 2 цель устанавливает и DEVSEL#, и TRDY#. Поскольку инициатор также готов, происходит передача данных. Это повторяется еще три цикла, но перед последним (фронт тактового сигнала 5) мастер снимает подтверждение FRAME#, указывая, что это конец. На фронте тактового сигнала 6 шина AD и FRAME# не управляются (цикл поворота), а другие линии управления управляются на высоком уровне в течение 1 цикла. На фронте тактового сигнала 7 другой инициатор может начать другую транзакцию. Это также цикл поворота для других линий управления.

Эквивалентный пакет чтения занимает на один цикл больше, поскольку цель должна ждать 1 цикл, пока шина AD не развернется, прежде чем она сможет установить TRDY#:

0_ 1_ 2_ 3_ 4_ 5_ 6_ 7_ 8_ КЛК _/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \ ___ ___ ___ ___ ___ AD[31:0] ---<___>---<___X___X___X___>---<___> ___ _______ ___ ___ ___ С/БЭ[3:0]# ---<___X_______X___X___X___>---<___> ___ | | | | ___ IRDY# ^^^^\___________________/ ^^^^^ ___ _____ | | | | ___ TRDY# ^^^^ \______________/ ^^^^^ ___ | | | | ___ ДЕВСЕЛ# ^^^^\___________________/ ^^^^^ ___ | | | ___ КАДР# \___________________/ | ^^^^\____ _ _ _ |_ |_ |_ |_ _ _ КЛК _/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \ 0 1 2 3 4 5 6 7 8

Высокоскоростной импульс, завершенный целью, будет иметь дополнительный цикл в конце:

0_ 1_ 2_ 3_ 4_ 5_ 6_ 7_ 8_ КЛК _/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \ ___ ___ ___ ___ ___ AD[31:0] ---<___>---<___X___X___X___XXXX>---- ___ _______ ___ ___ ___ ___ С/БЭ[3:0]# ---<___X_______X___X___X___X___>---- | | | | ___ IRDY# ^^^^^^^^\_______________________/ _____ | | | | _______ TRDY# ^^^^^^^ \______________/ ________________ | ___ СТОП# ^^^^^^^^ | | | \_______/ | | | | ___ ДЕВСЕЛ# ^^^^^^^^\_______________________/ ___ | | | | ___ КАДР# \_______________________/ ^^^^ _ _ _ |_ |_ |_ |_ _ _ КЛК _/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \_/ \ 0 1 2 3 4 5 6 7 8

На тактовом фронте 6 цель показывает, что она хочет остановиться (с данными), но инициатор уже удерживает IRDY# на низком уровне, поэтому наступает пятая фаза данных (тактовый фронт 7), во время которой данные не передаются.

Шина PCI обнаруживает ошибки четности, но не пытается исправить их повторными попытками операций; это просто указание на сбой. Из-за этого нет необходимости обнаруживать ошибку четности до того, как она произошла, и шина PCI фактически обнаруживает ее через несколько циклов. Во время фазы данных, какое бы устройство ни управляло линиями AD[31:0], оно вычисляет четность по ним и линиям C/BE[3:0]# и отправляет ее по линии PAR на один цикл позже. Все правила доступа и циклы поворота для шины AD применяются к линии PAR, всего на один цикл позже. Устройство, прослушивающее шину AD, проверяет полученную четность и подтверждает линию PERR# (ошибка четности) на один цикл после этого. Это обычно генерирует прерывание процессора, и процессор может искать на шине PCI устройство, которое обнаружило ошибку.

Линия PERR# используется только во время фаз данных, после выбора цели. Если ошибка четности обнаружена во время фазы адреса (или фазы данных специального цикла), устройства, которые ее наблюдают, устанавливают линию SERR# (системная ошибка).

Даже если некоторые байты замаскированы строками C/BE# и не используются, они все равно должны иметь некоторое определенное значение, и это значение должно использоваться для вычисления четности.

Из-за необходимости цикла оборота между различными устройствами, управляющими сигналами шины PCI, в общем случае необходимо иметь цикл ожидания между транзакциями шины PCI. Однако в некоторых обстоятельствах разрешается пропустить этот цикл ожидания, перейдя непосредственно от последнего цикла одной передачи (IRDY# установлен, FRAME# не установлен) к первому циклу следующей (FRAME# установлен, IRDY# не установлен).

Инициатор может выполнять встречные транзакции только в следующих случаях:

Дополнительные временные ограничения могут быть вызваны необходимостью разворота линий управления целью, в частности DEVSEL#. Цель отменяет подтверждение DEVSEL#, переводя его в высокий уровень в цикле, следующем за конечной фазой данных, которая в случае встречных транзакций является первым циклом адресной фазы. Второй цикл адресной фазы затем резервируется для разворота DEVSEL#, поэтому, если цель отличается от предыдущей, она не должна подтверждать DEVSEL# до третьего цикла (средняя скорость DEVSEL).

Один случай, когда эта проблема не может возникнуть, — если инициатор каким-то образом знает (предположительно, потому что адреса разделяют достаточное количество старших битов), что вторая передача адресована той же цели, что и предыдущая. В этом случае он может выполнять встречные транзакции. Все цели PCI должны поддерживать это.

Также возможно, что цель будет отслеживать требования. Если она никогда не делает быстрый DEVSEL, они выполняются тривиально. Если это так, она должна ждать до среднего времени DEVSEL, если только:

Целевые устройства, имеющие такую возможность, указывают на это специальным битом в регистре конфигурации PCI, и если все целевые устройства на шине имеют такую возможность, все инициаторы могут свободно использовать обратную передачу.

Мост шины субтрактивного декодирования должен знать, что следует ожидать эту дополнительную задержку в случае последовательных циклов, чтобы объявить о поддержке последовательных циклов.

Начиная с версии 2.1, [ необходимо уточнение ] спецификация PCI включает опциональную поддержку 64-битной шины. Это обеспечивается через расширенный разъем, который обеспечивает 64-битные расширения шины AD[63:32], C/BE[7:4]# и PAR64, а также ряд дополнительных контактов питания и заземления. 64-битный разъем PCI можно отличить от 32-битного разъема по дополнительному 64-битному сегменту.

Транзакции памяти между 64-битными устройствами могут использовать все 64 бита для удвоения скорости передачи данных. Транзакции, не связанные с памятью (включая доступ к конфигурации и пространству ввода-вывода), не могут использовать 64-битное расширение. Во время 64-битного пакета адресация пакета работает так же, как и при 32-битной передаче, но адрес увеличивается дважды за фазу данных. Начальный адрес должен быть выровнен по 64 битам; т. е. AD2 должен быть равен 0. Данные, соответствующие промежуточным адресам (с AD2 = 1), переносятся по верхней половине шины AD.

Чтобы инициировать 64-битную транзакцию, инициатор вводит начальный адрес на шине AD и одновременно с FRAME# выставляет REQ64#. Если выбранная цель может поддерживать 64-битную передачу для этой транзакции, она отвечает выставкой ACK64# одновременно с DEVSEL#. Цель может решать на основе каждой транзакции, разрешать ли 64-битную передачу.

Если REQ64# утверждается во время фазы адреса, инициатор также управляет старшими 32 битами адреса и копией команды шины на старшей половине шины. Если адрес требует 64 бита, двойной цикл адреса все еще требуется, но старшая половина шины несет старшую половину адреса и окончательный код команды во время обоих циклов фазы адреса; это позволяет 64-битной цели видеть весь адрес и начинать отвечать раньше.

Если инициатор видит DEVSEL#, установленный без ACK64#, он выполняет 32-битные фазы данных. Данные, которые были бы переданы по верхней половине шины во время первой фазы данных, вместо этого передаются во время второй фазы данных. Обычно инициатор управляет всеми 64 битами данных, прежде чем увидит DEVSEL#. Если ACK64# отсутствует, он может прекратить управлять верхней половиной шины данных.

Линии REQ64# и ACK64# поддерживаются в активном состоянии в течение всей транзакции, за исключением последней фазы данных, и снимаются в то же время, что и FRAME# и DEVSEL# соответственно.

Линия PAR64 работает так же, как линия PAR, но обеспечивает четность по AD[63:32] и C/BE[7:4]#. Она действительна только для фаз адреса, если REQ64# подтвержден. PAR64 действительна только для фаз данных, если REQ64# и ACK64# подтверждены.

PCI изначально включала опциональную поддержку обратной записи кэша когерентности . Это требовало поддержки кэшируемых целевых объектов памяти, которые прослушивали бы два контакта из кэша на шине, SDONE (snoop done) и SBO# (snoop backoff). [35]

Поскольку это редко реализовывалось на практике, это было удалено из версии 2.2 спецификации PCI, [16] [36] , а контакты были повторно использованы для доступа к SMBus в версии 2.3. [18]

Кэш будет отслеживать все обращения к памяти, не утверждая DEVSEL#. Если он заметит обращение, которое может быть кэшировано, он понизит уровень SDONE (snoop not done). Цель, поддерживающая когерентность, избежит завершения фазы данных (утверждая TRDY#), пока не увидит высокий уровень SDONE.

В случае записи в данные, которые были чистыми в кэше, кэш должен был бы только сделать свою копию недействительной и подтвердить SDONE, как только это было бы установлено. Однако, если кэш содержал грязные данные, кэш должен был бы записать их обратно, прежде чем доступ мог бы быть продолжен. поэтому он бы подтвердил SBO# при поднятии SDONE. Это дало бы сигнал активной цели утвердить STOP#, а не TRDY#, заставив инициатора отключиться и повторить операцию позже. Тем временем кэш был бы арбитражем для шины и записывал бы свои данные обратно в память.

Целевые устройства, поддерживающие когерентность кэша, также должны завершать пакеты до того, как они пересекут строки кэша.

При разработке и/или устранении неполадок шины PCI проверка аппаратных сигналов может быть очень важна. Логические анализаторы и анализаторы шин — это инструменты, которые собирают, анализируют и декодируют сигналы для пользователей, чтобы просматривать их в полезных способах.

Series — это настоящий 64-битный адаптер, расширяющий сетевой конвейер для достижения более высокой пропускной способности, а также предлагающий обратную совместимость со стандартными 32-битными слотами PCI.

Обратная совместимость с 32-битными слотами PCI 33 МГц

Adaptec SCSI Card 29160 является 64-битной PCI-картой, она также работает в 32-битном слоте PCI. При установке в 32-битный слот PCI карта автоматически работает в более медленном 32-битном режиме.