Программируемая вентильная матрица ( FPGA ) — это тип интегральной схемы , которую можно программировать или перепрограммировать после изготовления. Он состоит из массива программируемых логических блоков и межсоединений, которые можно настроить для выполнения различных цифровых функций. FPGA обычно используются в приложениях, где требуются гибкость, скорость и возможности параллельной обработки, например, в телекоммуникационном, автомобильном, аэрокосмическом и промышленном секторах.

Конфигурация FPGA обычно задается с использованием языка описания аппаратного обеспечения (HDL), аналогичного тому, который используется для интегральной схемы специального назначения (ASIC). Принципиальные схемы ранее использовались для определения конфигурации.

Логические блоки FPGA могут быть сконфигурированы для выполнения сложных комбинационных функций или действовать как простые логические элементы, такие как AND и XOR . В большинстве ПЛИС логические блоки также включают в себя элементы памяти , которые могут быть простыми триггерами или более полными блоками памяти. [1] Многие FPGA можно перепрограммировать для реализации различных логических функций , что позволяет гибко реконфигурировать вычисления , выполняемые в компьютерном программном обеспечении .

FPGA также играют роль в разработке встроенных систем благодаря их способности начинать разработку системного программного обеспечения одновременно с аппаратным обеспечением, позволяют моделировать производительность системы на очень ранней стадии разработки и позволяют проводить различные испытания системы и итерации проектирования перед завершением разработки системной архитектуры. [2]

FPGA также часто используются при разработке ASIC для ускорения процесса моделирования.

Индустрия FPGA выросла из программируемой постоянной памяти (PROM) и программируемых логических устройств (PLD). И PROM, и PLD можно было программировать партиями на заводе или в полевых условиях (программируемое на месте). [3]

Компания Altera была основана в 1983 году и в 1984 году выпустила первое в отрасли перепрограммируемое логическое устройство — EP300 — в корпусе которого было кварцевое окно, позволяющее пользователям освещать кристалл ультрафиолетовой лампой, чтобы стереть ячейки EPROM , в которых хранилась конфигурация устройства. . [4]

В 1985 году компания Xilinx выпустила первую коммерчески жизнеспособную программируемую вентильную матрицу — XC2064. [5] XC2064 имел программируемые ворота и программируемые соединения между воротами, что положило начало новой технологии и рынку. [6] XC2064 имел 64 настраиваемых логических блока (CLB) с двумя справочными таблицами с тремя входами (LUT). [7]

В 1987 году Центр надводных боевых действий ВМФ профинансировал эксперимент, предложенный Стивом Кассельманом, по разработке компьютера, который мог бы реализовать 600 000 перепрограммируемых вентилей. Кассельман добился успеха, и в 1992 году был выдан патент на систему. [3]

Altera и Xilinx продолжали существовать без каких-либо препятствий и быстро росли с 1985 года до середины 1990-х годов, когда появились конкуренты, разрушившие значительную часть их доли рынка. К 1993 году Actel (ныне Microsemi ) обслуживала около 18 процентов рынка. [6]

1990-е годы были периодом быстрого роста FPGA, как по сложности схем, так и по объему производства. В начале 1990-х годов FPGA в основном использовались в телекоммуникациях и сетях . К концу десятилетия FPGA нашли свое применение в потребительских, автомобильных и промышленных приложениях. [8]

К 2013 году Altera (31 процент), Actel (10 процентов) и Xilinx (36 процентов) вместе представляли примерно 77 процентов рынка FPGA. [9]

Такие компании, как Microsoft, начали использовать FPGA для ускорения высокопроизводительных, ресурсоемких систем (например, центров обработки данных , в которых используется их поисковая система Bing ) благодаря преимуществу производительности на ватт , которое обеспечивают FPGA. [10] Microsoft начала использовать FPGA для ускорения Bing в 2014 году, а в 2018 году начала развертывать FPGA в других рабочих нагрузках центров обработки данных для своей платформы облачных вычислений Azure . [11]

Следующие графики показывают прогресс в различных аспектах проектирования FPGA.

Начало проектирования — это новый индивидуальный проект для реализации на FPGA.

Современные FPGA имеют достаточное количество логических вентилей и блоков оперативной памяти для реализации сложных цифровых вычислений. FPGA можно использовать для реализации любой логической функции, которую может выполнять ASIC . Возможность обновления функциональности после поставки, частичная реконфигурация части конструкции [17] и низкие единовременные затраты на проектирование по сравнению с конструкцией ASIC (несмотря на обычно более высокую стоимость единицы продукции) дают преимущества для многих приложений. [1]

Поскольку в конструкциях FPGA используются очень высокие скорости ввода-вывода и двунаправленные шины данных , становится непросто проверить правильность синхронизации действительных данных в течение времени установки и времени удержания. [18] Планирование этажей помогает распределять ресурсы внутри FPGA для удовлетворения этих временных ограничений.

Некоторые FPGA помимо цифровых функций имеют аналоговые функции. Наиболее распространенной аналоговой функцией является программируемая скорость нарастания напряжения на каждом выходном контакте, что позволяет инженеру устанавливать низкие скорости на слабонагруженных контактах, которые в противном случае вызывали бы недопустимый звон или соединение , и устанавливать более высокие скорости на сильно нагруженных высокоскоростных каналах, которые в противном случае работали бы. слишком медленно. [19] [20] Также распространены схемы управления кварцевыми генераторами , встроенные в кристалл резистивно-емкостные генераторы и схемы фазовой автоподстройки частоты со встроенными генераторами, управляемыми напряжением, которые используются для генерации и управления тактовыми импульсами, а также для высокоскоростных сериализаторов. десериализатор (SERDES) передает тактовую частоту и восстанавливает тактовую частоту приемника. Достаточно распространены дифференциальные компараторы на входных контактах, предназначенные для подключения к каналам дифференциальной сигнализации . Некоторые FPGA со смешанными сигналами имеют встроенные периферийные аналого-цифровые преобразователи (АЦП) и цифро-аналоговые преобразователи (ЦАП) с блоками формирования аналогового сигнала, что позволяет им работать как система на кристалле (SoC). [21] Такие устройства стирают грань между FPGA, которая хранит цифровые единицы и нули на своей внутренней программируемой межсоединительной матрице, и программируемой пользователем аналоговой матрицей (FPAA), которая передает аналоговые значения на своей внутренней программируемой межсоединенной структуре.

Наиболее распространенная архитектура FPGA состоит из массива логических блоков , называемых настраиваемыми логическими блоками (CLB) или блоками логических массивов (LAB), в зависимости от производителя, площадок ввода-вывода и каналов маршрутизации. [1] Как правило, все каналы маршрутизации имеют одинаковую ширину (количество сигналов). Несколько площадок ввода-вывода могут соответствовать высоте одной строки или ширине одного столбца массива.

«Прикладная схема должна быть отображена в FPGA с адекватными ресурсами. Хотя количество необходимых логических блоков и входов/выходов легко определяется проектом, количество необходимых каналов маршрутизации может значительно различаться даже среди проектов с одинаковым объемом логики. Например, перекрестный коммутатор требует гораздо больше маршрутизации, чем систолический массив с тем же количеством вентилей.Поскольку неиспользуемые каналы маршрутизации увеличивают стоимость (и снижают производительность) FPGA, не принося никакой пользы, производители FPGA стараются предоставить ровно достаточное количество каналов. так что большинство проектов, которые подходят с точки зрения таблиц поиска (LUT) и входов/выходов, могут быть маршрутизированы . Это определяется оценками, полученными на основе правила Рента , или экспериментами с существующими проектами». [22]

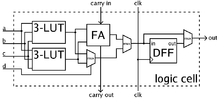

Обычно логический блок состоит из нескольких логических ячеек. Типичная ячейка состоит из 4-входового LUT, полного сумматора (FA) и триггера D-типа . LUT можно разделить на две LUT с 3 входами. В обычном режиме они объединяются в 4-входовой LUT через первый мультиплексор (mux). В арифметическом режиме их выходы подаются на сумматор. Выбор режима запрограммирован во втором мультиплексоре. Выход может быть синхронным или асинхронным , в зависимости от программирования третьего мультиплексора. На практике сумматор целиком или его части сохраняются как функции в LUT для экономии места . [23] [24] [25]

Современные семейства FPGA расширяют вышеуказанные возможности, включая функциональность более высокого уровня, зафиксированную в кремнии. Встраивание этих общих функций в схему уменьшает требуемую площадь и повышает производительность этих функций по сравнению с их построением из логических примитивов. Примеры таких устройств включают умножители , общие блоки DSP , встроенные процессоры , высокоскоростную логику ввода-вывода и встроенную память .

FPGA более высокого класса могут содержать высокоскоростные мультигигабитные приемопередатчики и жесткие IP-ядра, такие как процессорные ядра , блоки управления доступом к среде Ethernet , контроллеры PCI или PCI Express и контроллеры внешней памяти . Эти ядра существуют рядом с программируемой фабрикой, но они построены на транзисторах , а не на LUT, поэтому имеют производительность и энергопотребление на уровне ASIC, не потребляя при этом значительного количества ресурсов фабрики, оставляя большую часть фабрики свободной для логики, специфичной для приложения. Мультигигабитные трансиверы также содержат высокопроизводительные схемы формирования сигнала , а также высокоскоростные сериализаторы и десериализаторы — компоненты, которые невозможно построить на основе LUT. Функциональность физического уровня (PHY) более высокого уровня, такая как линейное кодирование, может быть реализована или не реализована вместе с сериализаторами и десериализаторами в жесткой логике, в зависимости от FPGA.

Альтернативный подход к использованию аппаратных макропроцессоров заключается в использовании IP-ядер программных процессоров , реализованных в логике FPGA. Nios II , MicroBlaze и Mico32 — примеры популярных процессоров с программным обеспечением. Многие современные FPGA программируются во время выполнения , что привело к идее реконфигурируемых вычислений или реконфигурируемых систем — процессоров , которые переконфигурируются в соответствии с поставленной задачей. Кроме того, начинают появляться новые архитектуры, не связанные с FPGA. Программно-конфигурируемые микропроцессоры, такие как Stretch S5000, используют гибридный подход, предоставляя массив процессорных ядер и программируемых ядер, подобных FPGA, на одном кристалле.

В 2012 году крупнозернистый архитектурный подход был сделан еще одним шагом вперед за счет объединения логических блоков и межсоединений традиционных FPGA со встроенными микропроцессорами и соответствующими периферийными устройствами для формирования полноценной системы на программируемом кристалле . Примеры таких гибридных технологий можно найти в полностью программируемой SoC Xilinx Zynq-7000 [26] , которая включает двухъядерный процессор ARM Cortex-A9 MPCore с тактовой частотой 1,0 ГГц , встроенный в логическую структуру FPGA [27] или в Altera Arria V. FPGA, включающая двухъядерный процессор ARM Cortex-A9 MPCore с частотой 800 МГц. Atmel FPSLIC — еще одно подобное устройство, в котором используется процессор AVR в сочетании с архитектурой программируемой логики Atmel. Устройства Microsemi SmartFusion включают в себя ядро жесткого процессора ARM Cortex-M3 (до 512 КБ флэш-памяти и 64 КБ ОЗУ) и аналоговые периферийные устройства , такие как многоканальные аналого-цифровые преобразователи и цифро-аналоговые преобразователи для их структура FPGA на основе флэш-памяти . [ нужна цитата ]

Большая часть логики внутри FPGA представляет собой синхронную схему , требующую тактового сигнала . FPGA содержат выделенные глобальные и региональные сети маршрутизации для тактирования и сброса, обычно реализуемые в виде H-дерева , поэтому их можно доставлять с минимальным перекосом . FPGA могут содержать аналоговые компоненты системы фазовой автоподстройки частоты или системы автоподстройки частоты по задержке для синтеза новых тактовых частот и управления джиттером . В сложных конструкциях можно использовать несколько тактовых импульсов с разными частотными и фазовыми соотношениями, каждый из которых образует отдельные тактовые домены . Эти тактовые сигналы могут генерироваться локально генератором или могут быть восстановлены из потока данных . Необходимо соблюдать осторожность при построении схемы пересечения тактовой области , чтобы избежать метастабильности . Некоторые FPGA содержат двухпортовые блоки ОЗУ, которые способны работать с разными тактовыми частотами, помогая создавать FIFO и двухпортовые буферы, соединяющие домены тактовых импульсов.

Чтобы уменьшить размер и энергопотребление FPGA, такие поставщики, как Tabula и Xilinx, внедрили трехмерную или многоуровневую архитектуру . [28] [29] После выпуска 28-нм FPGA 7-й серии компания Xilinx заявила, что некоторые детали с самой высокой плотностью в этих линейках продуктов FPGA будут изготовлены с использованием нескольких кристаллов в одном корпусе с использованием технологии, разработанной для 3D-конструирования и многоярусные сборки.

В подходе Xilinx несколько (три или четыре) активных кристаллов FPGA размещаются рядом на кремниевом переходнике – едином куске кремния, несущем пассивное межсоединение. [29] [30] Конструкция с несколькими кристаллами также позволяет создавать различные части FPGA с использованием разных технологических процессов, поскольку требования к процессам различаются между самой фабрикой FPGA и очень высокоскоростными последовательными приемопередатчиками 28 Гбит / с. FPGA, построенная таким образом, называется гетерогенной FPGA . [31]

Гетерогенный подход Altera предполагает использование одного монолитного кристалла FPGA и подключение других кристаллов и технологий к FPGA с помощью встроенной технологии Intel Multi-die Interconnection Bridge (EMIB). [32]

Чтобы определить поведение FPGA, пользователь предоставляет проект на языке описания аппаратного обеспечения (HDL) или в виде схематического проекта. Форма HDL больше подходит для работы с большими структурами, поскольку в ней можно указать функциональное поведение высокого уровня, а не рисовать каждую часть вручную. Однако ввод схемы может облегчить визуализацию конструкции и ее составных модулей .

С помощью инструмента автоматизации электронного проектирования создается список соединений с технологической картой . Затем список соединений можно адаптировать к фактической архитектуре FPGA с помощью процесса, называемого местом и маршрутом , который обычно выполняется собственным программным обеспечением компании FPGA для размещения и маршрутизации. Пользователь проверит результаты, используя временной анализ , моделирование и другие методы проверки и проверки . После завершения процесса проектирования и проверки двоичный файл, созданный, как правило, с использованием собственного программного обеспечения поставщика FPGA, используется для (ре)конфигурации FPGA. Этот файл передается в FPGA через последовательный интерфейс ( JTAG ) или на внешнее запоминающее устройство, такое как EEPROM .

Наиболее распространенными HDL являются VHDL и Verilog , а также такие расширения, как SystemVerilog . Однако в попытке снизить сложность проектирования на HDL, который сравнивают с эквивалентом языков ассемблера , предпринимаются шаги [ кем? ] повысить уровень абстракции за счет внедрения альтернативных языков . Язык графического программирования LabVIEW компании National Instruments (иногда называемый G ) имеет дополнительный модуль FPGA, доступный для настройки и программирования оборудования FPGA. Verilog был создан, чтобы упростить процесс, сделав HDL более надежным и гибким. Verilog в настоящее время является самым популярным. Verilog создает уровень абстракции, чтобы скрыть детали своей реализации. Verilog имеет синтаксис, подобный C, в отличие от VHDL. [33]

Чтобы упростить проектирование сложных систем на ПЛИС, существуют библиотеки предопределенных сложных функций и схем, которые были протестированы и оптимизированы для ускорения процесса проектирования. Эти предопределенные схемы обычно называются ядрами интеллектуальной собственности (IP) и доступны у поставщиков FPGA и сторонних поставщиков IP. Они редко бывают бесплатными и обычно выпускаются по проприетарным лицензиям. Другие предопределенные схемы доступны в сообществах разработчиков, таких как OpenCores (обычно выпускаются под бесплатными лицензиями и лицензиями с открытым исходным кодом, такими как GPL , BSD или аналогичные лицензии) и другими источниками. Такие конструкции известны как аппаратное обеспечение с открытым исходным кодом .

В типичном процессе проектирования разработчик приложения FPGA моделирует проект на нескольких этапах процесса проектирования. Первоначально описание RTL в VHDL или Verilog моделируется путем создания тестовых стендов для моделирования системы и наблюдения за результатами. Затем, после того как механизм синтеза сопоставляет проект со списком соединений, список соединений преобразуется в описание уровня вентиля , где моделирование повторяется для подтверждения того, что синтез прошел без ошибок. Наконец, проект закладывается в FPGA, после чего можно добавить задержки распространения и снова запустить моделирование с аннотациями этих значений в списке соединений.

Совсем недавно OpenCL (открытый язык вычислений) стал использоваться программистами, чтобы воспользоваться преимуществами производительности и энергоэффективности, обеспечиваемыми FPGA. OpenCL позволяет программистам разрабатывать код на языке программирования C и использовать функции FPGA в качестве ядер OpenCL, используя конструкции OpenCL. [34] Для получения дополнительной информации см. Синтез высокого уровня и преобразование C в HDL .

Большинство FPGA используют для программирования подход, основанный на SRAM . Эти FPGA программируются и перепрограммируются внутри системы, но требуют внешних загрузочных устройств. Например, флэш-память или устройства EEPROM часто могут загружать содержимое во внутреннюю SRAM, которая управляет маршрутизацией и логикой. Подход SRAM основан на CMOS .

Более редкие альтернативы подходу SRAM включают:

В 2016 году лидерами рынка FPGA были давние конкуренты отрасли Xilinx (теперь часть AMD ) и Altera (теперь дочерняя компания Intel ). [36] В то время они контролировали почти 90 процентов рынка.

И Xilinx (теперь AMD), и Altera (теперь Intel) предоставляют собственное программное обеспечение для автоматизации электронного проектирования для Windows и Linux ( ISE / Vivado и Quartus ), которое позволяет инженерам проектировать , анализировать, моделировать и синтезировать ( компилировать ) свои проекты. [37] [38]

В марте 2010 года Tabula анонсировала свою технологию FPGA, которая использует логику мультиплексирования по времени и межсоединения, что обеспечивает потенциальную экономию средств для приложений с высокой плотностью размещения. [39] 24 марта 2015 г. Tabula официально закрылась. [40]

1 июня 2015 года Intel объявила о приобретении Altera примерно за 16,7 миллиардов долларов и завершила сделку 30 декабря 2015 года .

27 октября 2020 года AMD объявила о приобретении Xilinx [42] и завершила сделку на сумму около 50 миллиардов долларов в феврале 2022 года. [43]

Среди других производителей:

FPGA можно использовать для решения любой вычислимой задачи . Это тривиально доказывается тем фактом, что FPGA можно использовать для реализации программного микропроцессора , такого как Xilinx MicroBlaze или Altera Nios II . Их преимущество заключается в том, что они значительно быстрее для некоторых приложений из-за их параллельного характера и оптимальности с точки зрения количества вентилей, используемых для определенных процессов. [48]

Первоначально FPGA создавались как конкуренты CPLD для реализации связующей логики для печатных плат . По мере увеличения размера, возможностей и скорости FPGA взяли на себя дополнительные функции до такой степени, что некоторые из них теперь продаются как полные системы на кристаллах (SoC). В частности, с появлением специальных умножителей в архитектурах FPGA в конце 1990-х годов приложения, которые традиционно были единственным резервом аппаратного обеспечения цифровых сигнальных процессоров (DSP), вместо этого начали включать FPGA. [49] [50]

Эволюция FPGA стимулировала рост использования этих устройств, архитектура которых позволяет разрабатывать аппаратные решения, оптимизированные для сложных задач, таких как сегментация 3D-изображений МРТ, дискретное 3D-вейвлет-преобразование, реконструкция томографических изображений или системы ПЭТ/МРТ. [51] [52] Разработанные решения могут выполнять интенсивные вычислительные задачи с параллельной обработкой, являются динамически перепрограммируемыми и имеют низкую стоимость, при этом удовлетворяя жестким требованиям реального времени, связанным с медицинской визуализацией.

Другой тенденцией в использовании FPGA является аппаратное ускорение , при котором можно использовать FPGA для ускорения определенных частей алгоритма и разделения части вычислений между FPGA и обычным процессором. Поисковая система Bing известна тем, что в 2014 году она применила ускорение FPGA для своего алгоритма поиска. [53] С 2018 года [обновлять]FPGA все чаще используются в качестве ускорителей искусственного интеллекта , включая так называемый «Проект Катапульта» Microsoft [11] , а также для ускорения искусственных нейронных сетей. для приложений машинного обучения .

Традиционно [ когда? ] FPGA были зарезервированы для конкретных вертикальных приложений , где объем производства невелик. Для этих мелкосерийных приложений надбавка, которую компании платят за единицу оборудования для программируемого чипа, более доступна, чем ресурсы разработки, затраченные на создание ASIC. По состоянию на 2017 год [обновлять]новая динамика затрат и производительности расширила спектр жизнеспособных приложений.

Там, где периферийные устройства для персональных компьютеров существуют на нишевых рынках или изо всех сил пытаются проникнуть на массовый рынок (иногда, несмотря на активную рекламу), может быть более рентабельным использовать FPGA для небольших производственных партий (например, 1000 единиц). Примеры включают экзотические продукты, такие как, например , ArVid , ленточный архиватор VHS (только некоторые версии которого были основаны на FPGA) и бюджетный псевдо- SSD-накопитель i-RAM от Gigabyte Technology , в котором использовалась Xilinx FPGA. [54] Часто чип, изготовленный на заказ, будет дешевле, если производить его в больших количествах, но FPGA могут быть выбраны для быстрого вывода продукта на рынок. Опять же, по мере роста доступности недорогих FPGA их включение даже в более крупные производственные партии может стать оправданным.

Другие варианты использования FPGA включают в себя:

FPGA играют решающую роль в современной военной связи, особенно в таких системах, как Joint Tactical Radio System (JTRS) и в устройствах таких компаний, как Thales и Harris Corporation . Их гибкость и программируемость делают их идеальными для военной связи, предлагая настраиваемую и безопасную обработку сигналов. В JTRS, используемом военными США, FPGA обеспечивают адаптивность и обработку в реальном времени, что имеет решающее значение для соответствия различным стандартам связи и методам шифрования. Компания Thales использует технологию FPGA при разработке устройств связи, отвечающих строгим требованиям военного использования, включая быструю реконфигурацию и надежную безопасность. Точно так же корпорация Harris, которая теперь является частью L3Harris Technologies , включает FPGA в свои оборонные и коммерческие коммуникационные решения, улучшая обработку сигналов и безопасность системы. [59]

FPGA имеют как преимущества, так и недостатки по сравнению с ASIC или защищенными микропроцессорами в отношении аппаратной безопасности . Гибкость FPGA снижает риск злонамеренных модификаций во время производства . [60] Ранее для многих FPGA битовый поток проекта был открыт, когда FPGA загружала его из внешней памяти (обычно при каждом включении питания). Все основные поставщики FPGA теперь предлагают разработчикам целый ряд решений по обеспечению безопасности, таких как шифрование битового потока и аутентификация . Например, Altera и Xilinx предлагают шифрование AES (до 256 бит) для битовых потоков, хранящихся во внешней флэш-памяти. Физические неклонируемые функции (PUF) представляют собой интегральные схемы, которые имеют свои уникальные сигнатуры благодаря обработке и могут также использоваться для защиты FPGA, занимая при этом очень мало аппаратного пространства. [61]

FPGA, которые сохраняют свою конфигурацию внутри энергонезависимой флэш-памяти, такие как программируемые устройства ProAsic 3 от Microsemi или XP2 от Lattice , не раскрывают битовый поток и не нуждаются в шифровании . Кроме того, флэш-память для справочной таблицы обеспечивает защиту от сбоев при единичных событиях для космических приложений. [ необходимы разъяснения ] Клиенты, которым нужна более высокая гарантия защиты от несанкционированного доступа, могут использовать FPGA с однократной записью и защитой от предохранения от таких поставщиков, как Microsemi .

Благодаря своим FPGA и SoC Stratix 10 компания Altera представила диспетчер безопасных устройств и функции физического неклонирования , обеспечивающие высокий уровень защиты от физических атак. [62]

В 2012 году исследователи Сергей Скоробогатов и Кристофер Вудс продемонстрировали, что некоторые FPGA могут быть уязвимы для враждебных намерений. Они обнаружили, что критическая бэкдор- уязвимость была изготовлена в кремнии как часть Actel/Microsemi ProAsic 3, что делает его уязвимым на многих уровнях, таких как перепрограммирование шифрования и ключей доступа , доступ к незашифрованному потоку битов, изменение низкоуровневых функций кремния и извлечение данных конфигурации . [63]

В 2020 году во всех ПЛИС Xilinx 7-й серии была обнаружена критическая уязвимость (названная «Starbleed»), которая делала бесполезным шифрование битового потока. Обходного пути нет. Xilinx не выпускала аппаратную версию. Устройства Ultrascale и более поздние версии, уже представленные на рынке в то время, не были затронуты.

Исторически FPGA были медленнее, менее энергоэффективными и, как правило, обеспечивали меньшую функциональность, чем их фиксированные аналоги ASIC . Исследование 2006 года показало, что проекты, реализованные на FPGA, требуют в среднем в 40 раз больше площади, потребляют в 12 раз больше динамической мощности и работают на треть быстрее, чем соответствующие реализации ASIC. [64]

Преимущества FPGA включают в себя возможность перепрограммирования уже после развертывания (т. е. «в полевых условиях») для исправления ошибок , а также часто включают более короткое время выхода на рынок и более низкие единовременные затраты на проектирование. Поставщики также могут пойти промежуточным путем через прототипирование FPGA : разработать прототип оборудования на FPGA, но произвести окончательную версию в виде ASIC, чтобы ее больше нельзя было модифицировать после завершения проектирования. То же самое часто происходит и с новыми конструкциями процессоров. [65] Некоторые FPGA имеют возможность частичной реконфигурации , что позволяет перепрограммировать одну часть устройства, в то время как другие части продолжают работать. [66] [67]

Основные различия между сложными программируемыми логическими устройствами (CPLD) и FPGA заключаются в архитектуре . CPLD имеет сравнительно ограниченную структуру, состоящую из одного или нескольких программируемых логических массивов суммы произведений , питающих относительно небольшое количество тактируемых регистров . В результате CPLD менее гибки, но имеют преимущество более предсказуемых временных задержек и более высокого соотношения логики и межсоединения. [ нужна цитация ] В архитектурах FPGA, с другой стороны, преобладают межсоединения . Это делает их гораздо более гибкими (с точки зрения диапазона конструкций, которые практичны для реализации на них), но также гораздо более сложными для проектирования или, по крайней мере, требуют более сложного программного обеспечения для автоматизации электронного проектирования (EDA). На практике различие между FPGA и CPLD часто заключается в размере, поскольку FPGA обычно намного больше с точки зрения ресурсов, чем CPLD. Обычно только FPGA содержат более сложные встроенные функции , такие как сумматоры , умножители , память и сериализаторы/десериализаторы . Еще одним распространенным отличием является то, что CPLD содержат встроенную флэш-память для хранения своей конфигурации, тогда как FPGA обычно требуют внешней энергонезависимой памяти (но не всегда). Когда конструкция требует простого мгновенного включения (логика уже настроена при включении питания), обычно предпочтительными являются CPLD. Для большинства других приложений обычно предпочтительнее использовать FPGA. Иногда в одной системе используются и CPLD, и FPGA. В этих конструкциях CPLD обычно выполняют функции связующей логики и отвечают за « загрузку » FPGA, а также за управление последовательностью сброса и загрузки всей печатной платы. Поэтому, в зависимости от приложения, может быть разумно использовать в одной конструкции и FPGA, и CPLD. [68]