Сумматор с пропуском переноса [nb 1] (также известный как сумматор с обходом переноса ) — это реализация сумматора , которая с небольшими усилиями улучшает задержку сумматора с пульсирующим переносом по сравнению с другими сумматорами. Улучшение задержки в наихудшем случае достигается за счет использования нескольких сумматоров с пропуском переноса для формирования сумматора с пропуском переноса по блоку.

В отличие от других быстрых сумматоров, производительность сумматора с пропуском переноса увеличивается только при использовании некоторых комбинаций входных битов. Это означает, что улучшение скорости является лишь вероятностным .

Худший случай для простого одноуровневого сумматора с пульсирующим переносом возникает, когда условие распространения [1] истинно для каждой пары цифр . Затем перенос проходит через -битный сумматор и появляется как перенос после .

Для каждой пары входных битов операнда условия распространения определяются с помощью XOR-вентиля. Когда все условия распространения истинны , бит переноса определяет бит переноса.

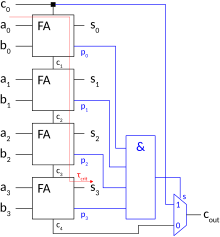

Сумматор с n -битным переносом и пропуском состоит из n -битной цепи переноса пульсаций, n- входного И-вентиля и одного мультиплексора. Каждый бит распространения , предоставляемый цепочкой переноса, подключен к n -входному И-вентилю. Результирующий бит используется в качестве бита выбора мультиплексора, который переключает либо последний бит переноса , либо входной перенос на сигнал переноса .

Это значительно уменьшает задержку сумматора на его критическом пути, поскольку бит переноса для каждого блока теперь может «пропускать» блоки с сигналом группового распространения, установленным на логику 1 (в отличие от длинной цепочки пульсирующего переноса, которая потребовала бы перенос для пульсации каждого бита сумматора). Количество входов И-вентиля равно ширине сумматора. При большой ширине это становится непрактичным и приводит к дополнительным задержкам, поскольку И-вентиль приходится строить в виде дерева. Хорошая ширина достигается, когда логика суммы имеет ту же глубину, что и n -входной логический элемент И и мультиплексор.

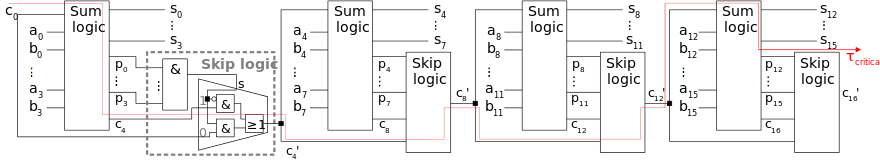

Критический путь сумматора переноса-пропуска начинается с первого полного сумматора, проходит через все сумматоры и заканчивается битом суммы . Сумматоры переноса-пропуска объединены в цепочку (см. «Суммары-переносы-блоки»), чтобы уменьшить общий критический путь, поскольку однобитовый сумматор переноса-пропуска не имеет реального преимущества в скорости по сравнению с -битным сумматором пульсирующего переноса.

Логика пропуска состоит из входного И-вентиля и одного мультиплексора.

Поскольку сигналы распространения вычисляются параллельно и доступны заранее, критический путь для логики пропуска в сумматоре с пропуском переноса состоит только из задержки, налагаемой мультиплексором (условный пропуск).

Сумматоры с пропуском переноса по блоку состоят из нескольких сумматоров с пропуском переноса. Существует два типа сумматоров с переносом и пропуском блоков. Два операнда и разбиваются на блоки битов.

Сумматоры фиксированного размера с переносом и пропуском блоков разбивают биты входных битов на блоки по битам каждый, в результате чего образуются блоки. Критический путь состоит из волнистого пути и элемента пропуска первого блока, путей пропуска, заключенных между первым и последним блоком, и, наконец, пульсирующего пути последнего блока.

Оптимальный размер блока для заданной ширины сумматора n определяется равенством 0

Реализуемы только положительные размеры блоков.

Производительность можно улучшить, т. е. все переносы распространяются быстрее, изменяя размеры блоков. Соответственно, начальные блоки сумматора делаются меньшими, чтобы быстро обнаружить генераторы переноса, которые должны распространяться дальше, средние блоки делаются больше, поскольку они не являются проблемным случаем, а затем наиболее важные блоки снова уменьшаются, так что опоздавшие входные данные переноса могут быть быстро обработаны.

При использовании дополнительных блоков пропуска на дополнительном уровне сигналы распространения блоков дополнительно суммируются и используются для выполнения более крупных пропусков:

Таким образом, сумматор становится еще быстрее.

Проблема определения размеров блоков и количества уровней, необходимых для создания физически самого быстрого сумматора с пропуском переноса, известна как «задача оптимизации сумматора с пропуском переноса». Эта проблема усложняется тем фактом, что сумматоры с пропуском переноса реализованы на физических устройствах, размер и другие параметры которых также влияют на время сложения.

Задача оптимизации переноса-пропуска для блоков переменного размера и нескольких уровней для узла процесса произвольного устройства была решена Томасом В. Линчем. [2] В этой ссылке также показано, что добавление переноса-пропуска аналогично параллельному добавлению префиксов и, таким образом, связано, а для некоторых конфигураций, идентичных Хану-Карлсону, [3] [4] Бренту -Кунгу , [5] сумматор Когге -Стоуна [6] и ряд других типов сумматоров.

Если разбить это на более конкретные термины, то для создания 4-битного сумматора с обходом переноса потребуется 6 полных сумматоров . Входные шины будут 4-битными A и 4-битными B с сигналом переноса ( CIN ). Выходом будет 4-битная шина X и сигнал выполнения ( COUT ).

Первые два полных сумматора складывают первые два бита. Сигнал выполнения от второго полного сумматора ( ) будет управлять сигналом выбора для трех мультиплексоров 2:1. Второй набор из двух полных сумматоров будет добавлять последние два бита, предполагая, что это логический 0. И последний набор полных сумматоров будет предполагать, что это логическая 1.

Затем мультиплексоры контролируют, какой выходной сигнал используется для COUT и .