Emotion Engine — это центральный процессор , разработанный и изготовленный Sony Computer Entertainment и Toshiba для использования в игровой консоли PlayStation 2 . Он также использовался в ранних моделях PlayStation 3 , продаваемых в Японии и Северной Америке (номера моделей CECHAxx и CECHBxx), для обеспечения поддержки игр для PlayStation 2. Массовое производство Emotion Engine началось в 1999 году и закончилось в конце 2012 года с прекращением выпуска PlayStation 2. [1]

Двигатель эмоций состоит из восьми отдельных «блоков», каждый из которых выполняет определенную задачу, интегрированных в один кристалл . Этими блоками являются: ядро ЦП, два блока векторной обработки (VPU), 10-канальный блок DMA , контроллер памяти и блок обработки изображений (IPU). Существует три интерфейса: интерфейс ввода-вывода для процессора ввода-вывода, графический интерфейс (GIF) для графического синтезатора и интерфейс памяти для системной памяти. [2]

Ядро ЦП тесно связано с первым VPU, VPU 0 . Вместе они отвечают за выполнение игрового кода и высокоуровневые вычисления моделирования. Второй VPU, VPU 1 , предназначен для преобразования геометрии и освещения и работает независимо, параллельно ядру ЦП, под управлением микрокода . VPU 0 , если он не используется, также может использоваться для геометрических преобразований. Списки отображения , созданные CPU/VPU0 и VPU1, отправляются в GIF, который определяет их приоритет перед отправкой в графический синтезатор для рендеринга.

Ядро ЦП представляет собой RISC- процессор двустороннего суперскалярного порядка . [3] Основанный на MIPS R5900, он реализует архитектуру набора команд MIPS-III (ISA) и большую часть MIPS-IV, в дополнение к специальному набору инструкций, разработанному Sony, который работал с 128-битными группами из 32-битных команд. битовые, 16-битные или 8-битные целые числа в режиме одной инструкции и нескольких данных (SIMD) (т. е. четыре 32-битных целых числа можно добавить к четырем другим с помощью одной инструкции). Определенные инструкции включают в себя: сложение, вычитание, умножение, деление, мин/макс, сдвиг, логический подсчет, подсчет начальных нулей, 128-битную загрузку/сохранение и сдвиг воронки с 256 на 128 бит в дополнение к некоторым, не описанным Sony для конкурентные причины. Вопреки некоторым заблуждениям, эти возможности SIMD не сводились к тому, что процессор был «128-битным», поскольку ни адреса памяти, ни сами целые числа не были 128-битными, а только общие SIMD/целочисленные регистры. Для сравнения, 128-битные регистры и SIMD-инструкции присутствовали в 32-битной архитектуре x86 с 1999 года, с появлением SSE . Однако внутренние пути данных имели ширину 128 бит, а процессоры могли работать с количествами размером 4x32 бита параллельно в отдельных регистрах.

Он имеет 6-этапный целочисленный конвейер и 15-этапный конвейер с плавающей запятой (FP). Ассортимент регистров состоит из 32 128-битных регистров VLIW SIMD (именование/переименование), одного 64-битного аккумулятора и двух 64-битных регистров общих данных, 8 16-битных регистров фиксированных функций, 16 8-битных регистров контроллера. Процессор также имеет два 64-битных целочисленных арифметико-логических блока (ALU), 128-битный блок загрузки-сохранения (LSU), блок выполнения ветвей (BXU) и 32-битный сопроцессор VU1 с плавающей запятой (FPU). (который действовал как контроллер синхронизации для VPU0/VPU1), содержащий ядро базового процессора MIPS с 32 64-битными регистрами FP и 15 32-битными целочисленными регистрами. ALU являются 64-битными с 32-битным FPU, не совместимым со стандартом IEEE 754. Пользовательский набор команд 107 MMI (Multimedia Extensions) был реализован путем группировки двух 64-битных целочисленных ALU. И целочисленный конвейер, и конвейер с плавающей запятой состоят из шести этапов.

Для подачи инструкций и данных исполнительным блокам имеется двусторонний набор ассоциативных кэшей инструкций емкостью 16 КБ [4] , двусторонний набор ассоциативных неблокирующих кэшей данных объемом 8 КБ [4] и оперативное ОЗУ объемом 16 КБ . Кэш инструкций и данных виртуально индексируются и физически помечаются тегами, в то время как блокнотная оперативная память находится в отдельном пространстве памяти. Для трансляции виртуальных адресов предусмотрен объединенный резервный буфер преобразования 48 инструкций и данных с двойной записью . Прогнозирование ветвей достигается с помощью кэша целевых адресов ветвей с 64 записями и таблицы истории ветвей, интегрированной в кеш инструкций. Штраф за неправильное предсказание ветвления составляет три цикла из-за короткого шестиэтапного конвейера.

Большая часть производительности Emotion Engine с плавающей запятой обеспечивается двумя блоками векторной обработки (VPU), обозначенными VPU0 и VPU1. По сути, это были DSP, адаптированные для 3D-математики, и предшественники аппаратных конвейеров вершинных шейдеров . Каждый VPU имеет 32 128-битных векторных SIMD- регистра (содержащих 4D-векторные данные), 16 16-битных регистров с фиксированной запятой, четыре блока умножения-накопления с плавающей запятой (FMAC), блок деления с плавающей запятой (FDIV) и локальную память данных. . Память данных для VPU0 имеет размер 4 КБ, а VPU1 имеет память данных 16 КБ.

Для достижения высокой пропускной способности память данных VPU подключается напрямую к GIF, и обе памяти данных могут считываться напрямую блоком DMA . Одна векторная инструкция состоит из четырех 32-битных значений с плавающей запятой одинарной точности , которые распределяются по четырем (32-битным) модулям FMAC одинарной точности для обработки. Эта схема аналогична расширениям SSEx от Intel.

Устройствам FMAC требуется четыре цикла для выполнения одной инструкции, но, поскольку устройства имеют шестиступенчатый конвейер , их пропускная способность составляет одну инструкцию за цикл. Устройство FDIV имеет девятиступенчатый конвейер и может выполнять одну инструкцию каждые семь тактов.

IPU позволял декодировать сжатые изображения MPEG-2 , что позволяло воспроизводить DVD-диски и игровые FMV . Это также позволило выполнить векторное квантование данных 2D-графики. [5]

Блок управления памятью, контроллер RDRAM и контроллер DMA обеспечивают доступ к памяти внутри системы. [5]

Связь между ядром MIPS, двумя VPU, GIF, контроллером памяти и другими устройствами осуществляется по 128-битной внутренней шине данных, работающей на половине тактовой частоты Emotion Engine, но для обеспечения большей пропускной способности имеется также 128-битная внутренняя шина данных. -битный выделенный путь между ЦП и VPU0 и 128-битный выделенный путь между VPU1 и GIF. При частоте 150 МГц внутренняя шина данных обеспечивает максимальную теоретическую пропускную способность 2,4 ГБ/с.

Связь между Emotion Engine и оперативной памятью происходит через два канала DRDRAM (Direct Rambus Dynamic Random Access Memory) и контроллер памяти , который взаимодействует с внутренней шиной данных. Каждый канал имеет ширину 16 бит и работает на частоте 400 МГц DDR (двойная скорость передачи данных). В совокупности два канала DRDRAM имеют максимальную теоретическую пропускную способность 25,6 Гбит/с (3,2 ГБ/с), что примерно на 33% больше пропускной способности, чем внутренняя шина данных. По этой причине контроллер памяти буферизует данные, отправляемые из каналов DRDRAM, чтобы ЦП мог использовать дополнительную полосу пропускания.

Emotion Engine напрямую взаимодействует с графическим синтезатором через GIF с помощью выделенной 64-битной шины 150 МГц с максимальной теоретической пропускной способностью 1,2 ГБ/с. [6]

Чтобы обеспечить связь между Emotion Engine и процессором ввода-вывода (IOP), интерфейс ввода-вывода соединяет 32-битную входную-выходную шину шириной 37,5 МГц с максимальной теоретической пропускной способностью 150 МБ/с к внутренней шине данных. Интерфейс обеспечивает достаточную пропускную способность для разъема расширения PCMCIA, который использовался для сетевого адаптера со встроенным интерфейсом P-ATA для более быстрого доступа к данным и онлайн-функциональности. Преимущество высокой пропускной способности заключалось в том, что ее можно было легко использовать для внедрения аппаратных расширений, таких как сетевой адаптер со встроенной поддержкой жестких дисков IDE, или других расширений для расширения функциональности и жизненного цикла продукта, что можно рассматривать как конкурентное преимущество. Однако в более новых вариантах (например, в тонкой версии) интерфейс будет обеспечивать гораздо большую пропускную способность, чем требуется устройствам ввода-вывода PlayStation, поскольку поддержка жестких дисков была удалена, а от конструкции разъема PCMCIA отказались в пользу более тонкой конструкции.

Emotion Engine содержал 13,5 миллионов металлооксидно-полупроводниковых (МОП) транзисторов [7] на кристалле интегральной схемы (ИС) площадью 240 мм 2 . [8] Он был изготовлен Sony и Toshiba по технологии комплементарного металл-оксид-полупроводник ( КМОП ) толщиной 0,25 мкм ( эффективная LG 0,18 мкм ) с четырьмя уровнями межсоединений.

Emotion Engine был упакован в решетку из пластиковых шариков с 540 контактами (PBGA).

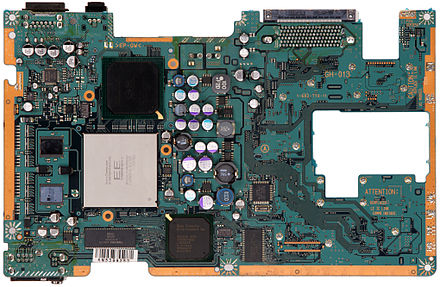

В основном Emotion Engine использовался в качестве процессора PlayStation 2 . Первые модели PlayStation 3 также имели на материнской плате Emotion Engine для обеспечения обратной совместимости с играми для PlayStation 2. Однако во второй версии PlayStation 3 отсутствовал физический Emotion Engine, чтобы снизить затраты, и все свои функции выполнялись с использованием программной эмуляции, выполняемой процессором широкополосной связи в сочетании с аппаратным графическим синтезатором, который все еще присутствует для достижения обратной совместимости с PlayStation 2. Во всех последующих версиях графический синтезатор был удален; однако программный эмулятор PlayStation 2 доступен в более поздних версиях системного программного обеспечения для использования с играми Sony PS2 Classics, доступными для покупки в Sony Entertainment Network.

Emotion Engine также использовался в цифровом видеомагнитофоне PSX , а также в моделях телевизоров Sony WEGA HVX (номера моделей KDE-xxxHVX/KDL-xxxHVX) и Sony BRAVIA KDL22PX300 HDTV, все из которых использовали оборудование PlayStation 2.