В электронике триггеры и защелки представляют собой схемы , имеющие два устойчивых состояния, которые могут хранить информацию о состоянии – бистабильный мультивибратор . Схема может быть изменена с помощью сигналов, подаваемых на один или несколько управляющих входов, и будет выводить свое состояние (часто вместе с его логическим дополнением ). Это основной элемент хранения в последовательной логике . Триггеры и защелки являются основными строительными блоками цифровых электронных систем, используемых в компьютерах, коммуникациях и многих других типах систем.

Триггеры и защелки используются в качестве элементов хранения данных для хранения одного бита (двоичной цифры) данных; одно из двух его состояний представляет «единицу», а другое представляет «ноль». Такое хранилище данных может использоваться для хранения состояния , и такая схема описывается как последовательная логика в электронике. При использовании в конечном автомате выход и следующее состояние зависят не только от его текущего входа, но и от его текущего состояния (и, следовательно, предыдущих входов). Его также можно использовать для подсчета импульсов и для синхронизации переменно-синхронизированных входных сигналов с некоторым опорным сигналом синхронизации.

Термин «триггер» исторически относился как к схемам, запускаемым по уровню (асинхронным, прозрачным или непрозрачным), так и к схемам, запускаемым по фронту ( синхронным или тактируемым ), которые хранят один бит данных с помощью вентилей . [1] Современные авторы резервируют термин «триггер» исключительно для запоминающих элементов, запускаемых по фронту, а защелки — для элементов, запускаемых по уровню. [2] [3] Термины «запускаемый по фронту» и «запускаемый по уровню» могут использоваться для избежания двусмысленности. [4]

Когда защелка, запускаемая по уровню, включена, она становится прозрачной, но выход триггера, запускаемого по фронту, изменяется только по фронту тактового сигнала (либо положительному, либо отрицательному).

Различные типы триггеров и защелок доступны в виде интегральных схем , обычно с несколькими элементами на чип. Например, 74HC75 — это четверная прозрачная защелка в серии 7400 .

Первая электронная защелка была изобретена в 1918 году британскими физиками Уильямом Эклзом и Ф. У. Джорданом . [5] [6] Первоначально она называлась триггерной схемой Эклза–Джордана и состояла из двух активных элементов ( вакуумных ламп ). [7] Эта конструкция использовалась в британском компьютере для взлома кодов Colossus 1943 года. [8] Такие схемы и их транзисторные версии были распространены в компьютерах даже после появления интегральных схем , хотя защелки и триггеры, сделанные из логических вентилей, также распространены сейчас. [9] [10] Ранние защелки были известны по-разному: триггерные схемы или мультивибраторы .

По словам инженера Лаборатории реактивного движения США П. Л. Линдли , типы триггеров, описанные ниже (SR, D, T, JK), впервые обсуждались в курсе по компьютерному проектированию в Калифорнийском университете в Лос-Анджелесе в 1954 году Монтгомери Фистером, а затем появились в его книге « Логическое проектирование цифровых компьютеров». [11] [12] В то время Линдли работал в Hughes Aircraft под руководством Элдреда Нельсона, который придумал термин JK для триггера, который менял состояние, когда оба входа были включены (логическая «единица»). Другие названия были придуманы Фистером. Они немного отличаются от некоторых определений, приведенных ниже. Линдли объясняет, что он услышал историю о триггере JK от Элдреда Нельсона, который придумал этот термин, работая в Hughes Aircraft. Все триггеры, использовавшиеся в Hughes в то время, были того типа, который стал известен как JK. При проектировании логической системы Нельсон присвоил буквы входам триггера следующим образом: № 1: A и B, № 2: C и D, № 3: E и F, № 4: G и H, № 5: J и K. Нельсон использовал обозначения « j -вход» и « k -вход» в патентной заявке, поданной в 1953 году. [13]

Прозрачные или асинхронные защелки могут быть построены вокруг одной пары перекрестно связанных инвертирующих элементов: электронные лампы , биполярные транзисторы , полевые транзисторы , инверторы и инвертирующие логические вентили — все они используются в практических схемах.

Синхронизированные триггеры специально разработаны для синхронных систем; такие устройства игнорируют свои входы, за исключением перехода выделенного тактового сигнала (известного как тактирование, пульсация или стробирование). Тактирование заставляет триггер либо изменять, либо сохранять свой выходной сигнал на основе значений входных сигналов при переходе. Некоторые триггеры изменяют выход на переднем фронте тактового сигнала, другие на заднем фронте.

Поскольку элементарные каскады усиления являются инвертирующими, два каскада могут быть соединены последовательно (как каскад) для формирования необходимого неинвертирующего усилителя. В этой конфигурации каждый усилитель может рассматриваться как активная инвертирующая сеть обратной связи для другого инвертирующего усилителя. Таким образом, два каскада соединены в неинвертирующую петлю, хотя схема цепи обычно рисуется как симметричная перекрестно связанная пара (оба чертежа первоначально представлены в патенте Эклза–Джордана).

Триггеры и защелки можно разделить на общие типы: SR («set-reset»), D («data»), T («toggle») и JK (см. раздел «История» выше). Поведение конкретного типа можно описать характеристическим уравнением, которое выводит «следующий» выход ( Q next ) в терминах входного сигнала(ов) и/или текущего выхода, .

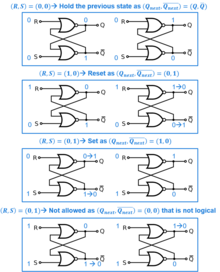

При использовании статических вентилей в качестве строительных блоков наиболее фундаментальной защелкой является асинхронная защелка Set-Reset (SR) .

Его два входа S и R могут устанавливать внутреннее состояние в 1, используя комбинацию S=1 и R=0, и могут сбрасывать внутреннее состояние в 0, используя комбинацию S=0 и R=1. [примечание 1]

Защелка SR может быть сконструирована из пары перекрестно связанных логических вентилей NOR или NAND . Сохраненный бит присутствует на выходе, обозначенном Q.

Удобно думать о NAND, NOR, AND и OR как об управляемых операциях, где один вход выбирается как набор управляющих входов, а другой бит как обрабатываемый вход в зависимости от состояния управления. Затем все эти вентили имеют одно управляющее значение, которое игнорирует вход (x) и выводит постоянное значение, в то время как другое управляющее значение пропускает вход (возможно, дополненный):

По сути, все они могут использоваться как переключатели, которые либо устанавливают определенное значение, либо пропускают входное значение.

Защелка SR NOR состоит из двух параллельных вентилей NOR, где выход каждого NOR также разветвляется на один вход другого NOR, как показано на рисунке. Мы называем входами обратной связи или просто обратными связями эти соединения выход-вход. Оставшиеся входы мы будем использовать в качестве управляющих входов, как объяснено выше. Обратите внимание, что на этом этапе, поскольку все симметрично, неважно, к каким входам подключены выходы. Теперь мы нарушаем симметрию, выбирая, какой из оставшихся управляющих входов будет нашей установкой и сбросом, и мы можем назвать «set NOR» вентилем NOR с управлением установкой и «reset NOR» вентилем NOR с управлением сбросом; на рисунках set NOR является нижним, а reset NOR — верхним. Выходом reset NOR будет наш сохраненный бит Q, в то время как мы увидим, что выход set NOR хранит его дополнение Q.

Чтобы вывести поведение защелки SR NOR, рассмотрим S и R как управляющие входы и вспомним, что из приведенных выше уравнений установка и сброс NOR с управлением 1 зафиксируют их выходы на 0, в то время как установка и сброс NOR с управлением 0 будут действовать как вентиль НЕ. Благодаря этому теперь можно вывести поведение защелки SR как простые условия (вместо того, чтобы, например, назначать значения каждой строке, чтобы увидеть, как они распространяются):

Примечание: X означает «безразлично », то есть допустимым значением является 0 или 1.

Комбинация R = S = 1 называется ограниченной комбинацией или запрещенным состоянием , поскольку, поскольку оба вентиля NOR затем выводят нули, это нарушает логическое уравнение Q = не Q. Эта комбинация также не подходит для схем, где оба входа могут одновременно перейти в состояние низкого уровня (т. е. переход от ограниченного к удержанию ). Выход может оставаться в метастабильном состоянии и в конечном итоге может заблокироваться либо на 1, либо на 0 в зависимости от временных соотношений распространения между вентилями ( состояние гонки ).

Чтобы преодолеть ограниченную комбинацию, можно добавить вентили к входам, которые будут преобразовываться (S, R) = (1, 1)в одну из неограниченных комбинаций. Это может быть:

Это реализовано практически в каждом программируемом логическом контроллере .

В качестве альтернативы ограниченная комбинация может быть сделана для переключения выхода. Результатом является защелка JK.

Характеристическое уравнение для SR-защелки имеет вид:

где A + B означает (A или B), AB означает (A и B)

Другое выражение:

Схема, показанная ниже, представляет собой базовую защелку NAND. Входы также обычно обозначаются как S и R для Set и Reset соответственно. Поскольку входы NAND обычно должны быть логической 1, чтобы не влиять на действие защелки, входы считаются инвертированными в этой схеме (или активным низким).

Схема использует ту же обратную связь, что и SR NOR, просто заменяя вентили NOR на вентили NAND, чтобы «запоминать» и сохранять свое логическое состояние даже после изменения управляющих входных сигналов. Опять же, напомним, что NAND-контролируемый 1 всегда выводит 0, в то время как NAND-контролируемый 0 действует как вентиль NOT. Когда входы S и R оба высокие, обратная связь сохраняет выходы Q в предыдущем состоянии. Когда один из них равен нулю, они фиксируют свои выходные биты на 0, в то время как другой адаптируется к дополнению. S=R=0 создает недопустимое состояние.

С точки зрения обучения, защелки SR, нарисованные как пара перекрестно связанных компонентов (транзисторы, затворы, трубки и т. д.), часто сложны для понимания новичками. Дидактически более простым объяснением будет нарисовать защелку как один контур обратной связи вместо перекрестной связи. Ниже представлена защелка SR, построенная с вентилем И с одним инвертированным входом и вентилем ИЛИ . Обратите внимание, что инвертор не нужен для функциональности защелки, а скорее для того, чтобы сделать оба входа высокоактивными.

Обратите внимание, что защелка SR AND-OR имеет то преимущество, что S = 1, R = 1 четко определены. В приведенной выше версии защелки SR AND-OR она отдает приоритет сигналу R над сигналом S. Если необходим приоритет S над R, этого можно добиться, подключив выход Q к выходу вентиля OR вместо выхода вентиля AND.

Защелку SR AND-OR легче понять, потому что оба вентиля можно объяснить изолированно, снова с помощью управляющего представления AND и OR сверху. Когда ни S, ни R не установлены, то и вентиль OR, и вентиль AND находятся в «режиме удержания», т. е. они пропускают вход, их выход является входом из петли обратной связи. Когда вход S = 1, то вентиль OR выводит 1, независимо от другого входа из петли обратной связи («режим установки»). Когда вход R = 1, то вентиль AND выводит 0, независимо от другого входа из петли обратной связи («режим сброса»). И поскольку вентиль AND принимает выход вентиля OR в качестве входа, R имеет приоритет над S. Защелки, нарисованные как перекрестно связанные вентили, могут выглядеть менее интуитивно понятными, так как поведение одного вентиля, по-видимому, переплетено с другим вентилем. Стандартные защелки NOR или NAND также можно перерисовать с помощью петли обратной связи, но в их случае петля обратной связи не показывает одинаковое значение сигнала на протяжении всей петли обратной связи. Однако у защелки SR AND-OR есть тот недостаток, что для нее потребуется дополнительный инвертор, если требуется инвертированный выход Q.

Обратите внимание, что защелку SR AND-OR можно преобразовать в защелку SR NOR с помощью логических преобразований: инвертирования выхода вентиля OR, а также второго входа вентиля AND и подключения инвертированного выхода Q между этими двумя добавленными инверторами; при этом вентиль AND с обоими инвертированными входами эквивалентен вентилю NOR согласно законам Де Моргана .

JK-защелка используется гораздо реже, чем JK-триггер. JK-защелка следует следующей таблице состояний:

Таким образом, защелка JK представляет собой защелку SR, которая переключает свой выход (колеблется между 0 и 1) при передаче входной комбинации 11. [16] В отличие от триггера JK, входная комбинация 11 для защелки JK не очень полезна, поскольку нет тактового сигнала, который бы управлял переключением. [17]

Защелки спроектированы так, чтобы быть прозрачными. То есть изменения входного сигнала вызывают немедленные изменения на выходе. К прозрачной защелке можно добавить дополнительную логику, чтобы сделать ее непрозрачной или непрозрачной , когда другой вход (вход «разрешения») не утвержден. Когда несколько прозрачных защелок следуют друг за другом, если они все прозрачны одновременно, сигналы будут распространяться через них все. Однако, если за прозрачной защелкой с высоким уровнем следует прозрачная защелка с низким уровнем (или наоборот), состояние и выход будут изменяться только на фронтах тактовых импульсов, образуя то, что называется триггером «ведущий-ведомый» .

Запираемая SR-защелка может быть создана путем добавления второго уровня вентилей NAND к инвертированной SR-защелке . Дополнительные вентили NAND дополнительно инвертируют входы, так что SR- защелка становится запираемой SR-защелкой ( SR-защелка трансформируется в запираемую SR -защелку с инвертированным разрешением).

В качестве альтернативы можно создать управляемую SR-защелку (с неинвертирующим включением), добавив к SR-защелке второй уровень вентилей И.

При высоком уровне E ( включено true) сигналы могут проходить через входные вентили к инкапсулированной защелке; все комбинации сигналов, за исключением (0, 0) = удержание , затем немедленно воспроизводятся на выходе (Q, Q ), т. е. защелка прозрачна .

При низком уровне E ( включить false) защелка закрыта (непрозрачна) и остается в том состоянии, в котором она находилась в последний раз, когда уровень E был высоким.

Периодический входной сигнал разрешения можно назвать стробом записи . Когда вход разрешения является тактовым сигналом , защелка считается чувствительной к уровню (к уровню тактового сигнала), в отличие от чувствительной к фронту, как триггеры ниже.

Эта защелка использует тот факт, что в двух активных входных комбинациях (01 и 10) запираемой SR-защелки R является дополнением S. Входной каскад NAND преобразует два входных состояния D (0 и 1) в эти две входные комбинации для следующей SR- защелки путем инвертирования входного сигнала данных. Низкое состояние разрешающего сигнала создает неактивную комбинацию «11». Таким образом, запираемая D-защелка может рассматриваться как одновходовая синхронная SR-защелка . Такая конфигурация предотвращает применение ограниченной входной комбинации. Она также известна как прозрачная защелка , защелка данных или просто запираемая защелка . Она имеет вход данных и разрешающий сигнал (иногда называемый тактовым или управляющим ). Слово прозрачный происходит от того факта, что когда разрешающий вход включен, сигнал распространяется напрямую через схему от входа D к выходу Q. Запираемые D-защелки также чувствительны к уровню относительно уровня тактового или разрешающего сигнала.

Прозрачные защелки обычно используются в качестве портов ввода-вывода или в асинхронных системах, или в синхронных двухфазных системах ( синхронных системах , использующих двухфазный тактовый сигнал ), где две защелки, работающие на разных фазах тактового сигнала, предотвращают прозрачность данных, как в триггере «ведущий-ведомый».

Таблица истинности ниже показывает, что когда вход блокировки enable / c равен 0, вход D не оказывает влияния на выход. Когда E/C высокий, выход равен D.

Классические конструкции задвижек с затворами имеют некоторые нежелательные характеристики. [18] Они требуют двухканальной логики или инвертора. Распространение от входа к выходу может занять до трех задержек затвора. Распространение от входа к выходу не является постоянным — некоторые выходы занимают две задержки затвора, а другие — три.

Проектировщики искали альтернативы. [19] Успешной альтернативой является защелка Эрла. Она требует только одного ввода данных, а ее выход занимает постоянную задержку в два вентиля. Кроме того, два уровня вентилей защелки Эрла в некоторых случаях могут быть объединены с двумя последними уровнями вентилей схем, управляющих защелкой, поскольку многие общие вычислительные схемы имеют слой OR, за которым следует слой AND в качестве последних двух уровней. Объединение функции защелки может реализовать защелку без дополнительных задержек вентилей. [18] Объединение обычно используется при проектировании конвейерных компьютеров и, по сути, изначально было разработано Джоном Г. Эрлом для использования в IBM System/360 Model 91 для этой цели. [20]

Защелка Эрла не представляет опасности. [21] Если средний вентиль NAND опущен, то получается защелка удержания полярности , которая обычно используется, поскольку требует меньше логики. [21] [22] Однако она подвержена логической опасности. Намеренное искажение тактового сигнала может избежать опасности. [22]

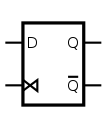

D-триггер широко используется и известен как «информационный» триггер. D-триггер захватывает значение D-входа в определенной части тактового цикла (например, нарастающий фронт тактового сигнала). Это захваченное значение становится выходом Q. В других случаях выход Q не изменяется. [23] [24] D-триггер можно рассматривать как ячейку памяти, удержание нулевого порядка или линию задержки . [25]

Таблица истинности:

( X обозначает состояние «безразлично» , то есть сигнал не имеет значения)

Большинство триггеров D-типа в ИС имеют возможность принудительного перевода в состояние установки или сброса (которое игнорирует входы D и тактового сигнала), во многом подобно триггеру SR. Обычно недопустимое условие S = R = 1 разрешается в триггерах D-типа. Установка S = R = 0 заставляет триггер вести себя так, как описано выше. Вот таблица истинности для других возможных конфигураций S и R:

Эти триггеры очень полезны, так как они составляют основу сдвиговых регистров , которые являются неотъемлемой частью многих электронных устройств. Преимущество D-триггера над "прозрачной защелкой" D-типа заключается в том, что сигнал на входном контакте D захватывается в момент тактирования триггера, и последующие изменения на входе D будут игнорироваться до следующего тактового события. Исключением является то, что некоторые триггеры имеют вход сигнала "сброса", который сбрасывает Q (в ноль), и могут быть как асинхронными, так и синхронными с тактовыми сигналами.

Вышеуказанная схема сдвигает содержимое регистра вправо на одну позицию бита при каждом активном переходе часов. Вход X сдвигается в самую левую позицию бита.

Эта схема [26] состоит из двух стадий, реализованных защелками SR NAND. Входной каскад (две защелки слева) обрабатывает сигналы синхронизации и данных, чтобы обеспечить правильные входные сигналы для выходного каскада (единственная защелка справа). Если тактовый сигнал низкий, оба выходных сигнала входного каскада высокие независимо от входных данных; выходная защелка не затронута и сохраняет предыдущее состояние. Когда тактовый сигнал изменяется с низкого на высокий, только одно из выходных напряжений (в зависимости от сигнала данных) становится низким и устанавливает/сбрасывает выходную защелку: если D = 0, нижний выход становится низким; если D = 1, верхний выход становится низким. Если тактовый сигнал продолжает оставаться высоким, выходы сохраняют свои состояния независимо от входных данных и заставляют выходную защелку оставаться в соответствующем состоянии, поскольку входной логический ноль (выходного каскада) остается активным, пока тактовый сигнал высокий. Следовательно, роль выходной защелки заключается в сохранении данных только пока тактовый сигнал низкий.

Схема тесно связана с управляемой D-защелкой, поскольку обе схемы преобразуют два состояния входа D (0 и 1) в две входные комбинации (01 и 10) для выходной SR- защелки путем инвертирования входного сигнала данных (обе схемы разделяют один сигнал D на два дополнительных сигнала S и R ). Разница в том, что в управляемой D-защелке используются логические вентили NAND, в то время как в D-триггере с положительным фронтом используются защелки SR NAND. Роль этих защелок заключается в «запирании» активного выхода, производящего низкое напряжение (логический ноль); таким образом, управляемый положительным фронтом D-триггер можно также рассматривать как управляемую D-защелку с защелкивающимися входными вентилями.

D-триггер типа «ведущий-ведомый» создается путем последовательного соединения двух запираемых D-защелок и инвертирования разрешающего входа на одну из них. Он называется «ведущий-ведомый», поскольку ведущая защелка управляет выходным значением ведомой защелки Q и заставляет ведомую защелку удерживать свое значение всякий раз, когда ведомая защелка включена, поскольку ведомая защелка всегда копирует свое новое значение из ведущей защелки и изменяет свое значение только в ответ на изменение значения ведущей защелки и тактового сигнала.

Для D-триггера master-slave, запускаемого положительным фронтом, когда тактовый сигнал низкий (логический 0), «разрешение», видимое первой или «главной» D-защелкой (инвертированный тактовый сигнал), высокое (логическая 1). Это позволяет «главной» защелке сохранять входное значение, когда тактовый сигнал переходит с низкого на высокий. Когда тактовый сигнал становится высоким (от 0 до 1), инвертированное «разрешение» первой защелки становится низким (от 1 до 0), а значение, видимое на входе в ведущую защелку, «заблокировано». Почти одновременно дважды инвертированное «разрешение» второй или «ведомой» D-защелки переходит с низкого на высокий (от 0 до 1) вместе с тактовым сигналом. Это позволяет сигналу, захваченному на переднем фронте тактового сигнала теперь «заблокированной» главной защелкой, проходить через «ведомую» защелку. Когда тактовый сигнал возвращается к низкому уровню (от 1 до 0), выход «ведомой» защелки «блокируется», и значение, видимое на последнем нарастающем фронте тактового сигнала, удерживается, в то время как «ведущая» защелка начинает принимать новые значения, готовясь к следующему нарастающему фронту тактового сигнала.

Удаление самого левого инвертора в схеме создает триггер D-типа, который стробируется на заднем фронте тактового сигнала. Это имеет такую таблицу истинности:

Триггеры, которые считывают новое значение по восходящему и нисходящему фронтам тактового сигнала, называются триггерами с двойным срабатыванием по фронту. Такой триггер может быть построен с использованием двух триггеров D-типа с срабатыванием по фронту и мультиплексора или с использованием двух триггеров D-типа с срабатыванием по фронту и трех вентилей XOR.

Эффективную функциональную альтернативу D-триггеру можно создать с помощью динамических схем (где информация хранится в емкости), если она достаточно часто синхронизируется; хотя это и не настоящий триггер, его все равно называют триггером из-за его функциональной роли. В то время как ведущий-ведомый элемент D запускается по фронту тактового сигнала, каждый из его компонентов запускается по уровням тактового сигнала. «D-триггер, запускаемый фронтом», как его называют, хотя он и не является настоящим триггером, не обладает свойствами ведущего-ведомого.

D-триггеры с фронтом часто реализуются в интегрированных высокоскоростных операциях с использованием динамической логики . Это означает, что цифровой выход сохраняется на паразитной емкости устройства, пока устройство не переходит. Эта конструкция позволяет выполнить сброс, просто разрядив один или несколько внутренних узлов. Распространенной разновидностью динамических триггеров является тип истинного однофазного тактового генератора (TSPC), который выполняет операцию триггера с небольшой мощностью и на высоких скоростях. Однако динамические триггеры обычно не работают на статических или низких тактовых частотах: при наличии достаточного времени пути утечки могут разрядить паразитную емкость достаточно, чтобы триггер перешел в недопустимые состояния.

Если вход T высокий, триггер T меняет состояние («переключается») всякий раз, когда стробируется вход синхронизации. Если вход T низкий, триггер сохраняет предыдущее значение. Такое поведение описывается характеристическим уравнением :

и может быть описана в таблице истинности :

Когда T удерживается на высоком уровне, триггер делит тактовую частоту на два; то есть, если тактовая частота составляет 4 МГц, выходная частота, полученная от триггера, будет равна 2 МГц. Эта функция «деления на» применяется в различных типах цифровых счетчиков . AT-триггер также может быть построен с использованием JK-триггера (контакты J и K соединены вместе и действуют как T) или D-триггера (вход T XOR Q, предыдущий управляет входом D).

Триггер JK дополняет поведение триггера SR (J: Set, K: Reset), интерпретируя условие J = K = 1 как команду «переключения» или переключения. В частности, комбинация J = 1, K = 0 является командой для установки триггера; комбинация J = 0, K = 1 является командой для сброса триггера; а комбинация J = K = 1 является командой для переключения триггера, т. е. изменения его выхода на логическое дополнение его текущего значения. Установка J = K = 0 сохраняет текущее состояние. Чтобы синтезировать триггер D, просто установите K равным дополнению J (вход J будет действовать как вход D). Аналогично, чтобы синтезировать триггер T, установите K равным J. Таким образом, триггер JK является универсальным триггером, поскольку его можно настроить для работы в качестве триггера SR, триггера D или триггера T.

Характеристическое уравнение JK-триггера имеет вид:

и соответствующая таблица истинности:

Входной сигнал должен быть постоянным в период около восходящего фронта часов, известного как апертура. Представьте себе, что вы фотографируете лягушку на листе кувшинки. [28] Предположим, что лягушка затем прыгает в воду. Если вы сфотографируете лягушку, когда она прыгает в воду, вы получите размытое изображение лягушки, прыгающей в воду — неясно, в каком состоянии была лягушка. Но если вы сделаете снимок, когда лягушка устойчиво сидит на листе (или устойчиво находится в воде), вы получите четкое изображение. Точно так же входной сигнал на триггер должен быть постоянным в течение апертуры триггера .

Время настройки — это минимальное время, в течение которого входные данные должны оставаться стабильными до наступления события часов, чтобы часы могли надежно считывать данные.

Время удержания — это минимальное время, в течение которого входные данные должны оставаться стабильными после события часов, чтобы часы могли надежно считывать данные.

Диафрагма — это сумма времени настройки и удержания. Ввод данных должен быть постоянным в течение всего этого периода времени. [28]

Время восстановления — это минимальное количество времени, в течение которого асинхронный вход установки или сброса должен быть неактивным до события часов, чтобы данные надежно отбирались часами. Время восстановления для асинхронного входа установки или сброса, таким образом, аналогично времени настройки для входа данных.

Время удаления — это минимальное количество времени, в течение которого асинхронный вход установки или сброса должен быть неактивным после события часов, чтобы данные надежно отбирались часами. Время удаления для асинхронного входа установки или сброса, таким образом, аналогично времени удержания для входа данных.

Короткие импульсы, подаваемые на асинхронные входы (установка, сброс), не должны подаваться полностью в течение периода восстановления-удаления, иначе становится совершенно неопределенным, перейдет ли триггер в соответствующее состояние. В другом случае, когда асинхронный сигнал просто делает один переход, который случайно попадает между временем восстановления/удаления, в конечном итоге триггер перейдет в соответствующее состояние, но на выходе может появиться или не появиться очень короткий сбой, в зависимости от синхронного входного сигнала. Эта вторая ситуация может иметь или не иметь значение для конструкции схемы.

Сигналы установки и сброса (и другие) могут быть как синхронными, так и асинхронными и, следовательно, могут характеризоваться либо временем установки/удержания, либо временем восстановления/снятия, а синхронность во многом зависит от конструкции триггера.

Дифференциация между временем установки/удержания и временем восстановления/удаления часто необходима при проверке синхронизации больших схем, поскольку асинхронные сигналы могут оказаться менее критичными, чем синхронные сигналы. Дифференциация дает разработчикам схем возможность независимо определять условия проверки для этих типов сигналов.

Триггеры подвержены проблеме, называемой метастабильностью , которая может возникнуть, когда два входа, такие как данные и часы или часы и сброс, изменяются примерно в одно и то же время. Когда порядок не ясен, в пределах соответствующих временных ограничений, результатом является то, что выход может вести себя непредсказуемо, занимая во много раз больше времени, чем обычно, чтобы установиться в одно или другое состояние, или даже колеблясь несколько раз перед установкой. Теоретически время установки не ограничено. В компьютерной системе эта метастабильность может привести к повреждению данных или сбою программы, если состояние нестабильно до того, как другая схема использует его значение; в частности, если два разных логических пути используют выход триггера, один путь может интерпретировать его как 0, а другой как 1, когда он не перешел в стабильное состояние, переводя машину в несогласованное состояние. [29]

Метастабильность в триггерах можно избежать, гарантируя, что данные и управляющие входы будут оставаться действительными и постоянными в течение определенных периодов до и после тактового импульса, называемых временем настройки (t su ) и временем удержания (t h ) соответственно. Эти времена указаны в техническом описании устройства и обычно составляют от нескольких наносекунд до нескольких сотен пикосекунд для современных устройств. В зависимости от внутренней организации триггера можно построить устройство с нулевым (или даже отрицательным) требованием времени настройки или удержания, но не обоими одновременно.

К сожалению, не всегда возможно соблюсти критерии настройки и удержания, поскольку триггер может быть подключен к сигналу реального времени, который может измениться в любой момент вне контроля разработчика. В этом случае лучшее, что может сделать разработчик, — это снизить вероятность ошибки до определенного уровня в зависимости от требуемой надежности схемы. Один из методов подавления метастабильности — соединить два или более триггера в цепочку, так что выход каждого из них подает данные на вход следующего, и все устройства используют общие часы. С помощью этого метода вероятность метастабильного события может быть снижена до пренебрежимо малого значения, но никогда до нуля. Вероятность метастабильности становится все ближе и ближе к нулю по мере увеличения числа последовательно соединенных триггеров. Число каскадируемых триггеров называется «ранжированием»; «двухранговые» триггеры (два триггера последовательно) являются обычной ситуацией.

Доступны так называемые метастабильно-устойчивые триггеры, которые работают, максимально сокращая время установки и удержания, но даже они не могут полностью устранить проблему. Это связано с тем, что метастабильность — это больше, чем просто вопрос схемотехнической разработки. Когда переходы в часах и данных близки по времени, триггер вынужден решать, какое событие произошло первым. Как бы быстро ни было сделано устройство, всегда есть вероятность, что входные события будут настолько близки друг к другу, что оно не сможет определить, какое из них произошло первым. Поэтому логически невозможно построить идеально метастабильный триггер. Триггеры иногда характеризуются максимальным временем установления (максимальным временем, в течение которого они будут оставаться метастабильными при определенных условиях). В этом случае двухранговые триггеры, тактируемые медленнее, чем максимально допустимое время метастабильности, обеспечат надлежащую подготовку для асинхронных (например, внешних) сигналов.

Другим важным значением времени для триггера является задержка от тактового сигнала до выхода (общий символ в технических описаниях: t CO ) или задержка распространения (t P ), которая представляет собой время, необходимое триггеру для изменения своего выхода после фронта тактового сигнала. Время перехода с высокого уровня на низкий (t PHL ) иногда отличается от времени перехода с низкого уровня на высокий (t PLH ).

При каскадном соединении триггеров, которые совместно используют одни и те же часы (как в сдвиговом регистре ), важно гарантировать, что t CO предыдущего триггера больше, чем время удержания (t h ) следующего триггера, поэтому данные, присутствующие на входе последующего триггера, правильно «сдвинуты» после активного фронта часов. Такое соотношение между t CO и t h обычно гарантируется, если триггеры физически идентичны. Кроме того, для правильной работы легко проверить, что период часов должен быть больше суммы t su + t h .

Триггеры можно обобщить по крайней мере двумя способами: сделав их 1-из-N вместо 1-из-2, и адаптировав их к логике с более чем двумя состояниями. В особых случаях кодирования 1-из-3 или многозначной троичной логики такой элемент можно назвать триггером -флэпом . [30]

В обычном триггере ровно один из двух дополнительных выходов имеет высокий уровень. Это можно обобщить до элемента памяти с N выходами, ровно один из которых имеет высокий уровень (или ровно один из N имеет низкий уровень). Таким образом, выход всегда является представлением «один горячий» (соответственно, «один холодный »). Конструкция похожа на обычный перекрестно-связанный триггер; каждый выход, когда имеет высокий уровень, подавляет все остальные выходы. [31] В качестве альтернативы можно использовать более или менее обычные триггеры, по одному на выход, с дополнительной схемой, чтобы гарантировать, что только один за раз может быть истинным. [32]

Другим обобщением обычного триггера является элемент памяти для многозначной логики . В этом случае элемент памяти сохраняет ровно одно из логических состояний до тех пор, пока управляющие входы не вызовут изменение. [33] Кроме того, также могут использоваться многозначные часы, что приводит к новым возможным переходам часов. [34]

{{cite book}}: |journal=проигнорировано ( помощь )