Производство полупроводниковых устройств — это процесс, используемый для производства полупроводниковых устройств , обычно интегральных схем (ИС), таких как компьютерные процессоры , микроконтроллеры и микросхемы памяти (такие как флэш-память NAND и DRAM ), которые присутствуют в повседневных электронных устройствах. Это многоэтапный фотолитографический и физико-химический процесс (с такими этапами, как термическое окисление , осаждение тонких пленок, ионная имплантация, травление), в ходе которого электронные схемы постепенно создаются на пластине , обычно изготовленной из чистого монокристаллического полупроводника. материал. Почти всегда используется кремний , но для специализированных применений используются различные соединения полупроводников .

Процесс изготовления осуществляется на узкоспециализированных заводах по производству полупроводников , также называемых литейными заводами или «фабриками» [1] , центральной частью которых является « чистая комната ». В более совершенных полупроводниковых устройствах, таких как современные узлы 14/10/7 нм , изготовление может занять до 15 недель, при этом в среднем по отрасли 11–13 недель . [2] Производство на передовых производственных мощностях полностью автоматизировано, а автоматизированные системы обработки материалов обеспечивают транспортировку пластин от машины к машине. [3]

Пластина часто имеет несколько интегральных схем, которые называются кристаллами, поскольку представляют собой кусочки, вырезанные из одной пластины. Отдельные штампы отделяются от готовой пластины в процессе, называемом разделением штампов , также называемом нарезкой пластин. Затем штампы могут подвергаться дальнейшей сборке и упаковке. [4]

На производственных предприятиях пластины транспортируются в специальных герметичных пластиковых коробках, называемых FOUP . [3] FOUP во многих фабриках содержат внутреннюю азотную атмосферу [5] [6] , которая помогает предотвратить окисление меди на пластинах. Медь используется в современных полупроводниках для проводки. [7] Внутренности технологического оборудования и ФОУП остаются чище, чем окружающий воздух в чистом помещении. Эта внутренняя атмосфера известна как мини-среда и помогает повысить производительность, то есть количество работающих устройств на пластине. Эта мини-среда находится внутри EFEM (модуля внешнего интерфейса оборудования) [8], который позволяет машине получать FOUP и вводить пластины из FOUP в машину. Кроме того, многие машины также обрабатывают пластины в среде чистого азота или вакуума, чтобы уменьшить загрязнение и улучшить контроль процесса. [3] Производственным предприятиям необходимо большое количество жидкого азота для поддержания атмосферы внутри производственного оборудования и FOUP, которые постоянно продуваются азотом. [5] [6] Также между FOUP и EFEM может быть установлена воздушная завеса или сетка [9] , которая помогает уменьшить количество влаги, попадающей в FOUP, и повысить урожайность. [10] [11]

Компании, производящие машины, используемые в процессе промышленного изготовления полупроводников, включают ASML , Applied Materials , Tokyo Electron и Lam Research .

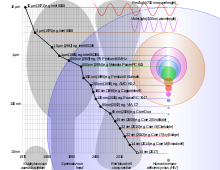

Размер элемента определяется шириной наименьших линий, которые можно нанести в процессе производства полупроводников. Это измерение известно как ширина линии. [12] [13] Нанесение рисунка часто относится к фотолитографии, которая позволяет определить дизайн или рисунок устройства на устройстве во время изготовления. [14] F 2 используется для измерения площади различных частей полупроводникового устройства в зависимости от размера элемента процесса производства полупроводников. Многие полупроводниковые устройства состоят из секций, называемых ячейками, и каждая ячейка представляет собой небольшую часть устройства, например ячейку памяти для хранения данных. Таким образом, F 2 используется для измерения площади, занимаемой этими ячейками или секциями. [15]

Конкретный полупроводниковый процесс имеет определенные правила относительно минимального размера (ширины или CD/критического размера) и пространства для элементов на каждом слое чипа. [16] Обычно новый полупроводниковый процесс имеет меньшие минимальные размеры и меньшее расстояние. В некоторых случаях это позволяет просто уменьшить размеры кристалла существующей конструкции микросхемы, чтобы снизить затраты, улучшить производительность [16] и увеличить плотность транзисторов (количество транзисторов на единицу площади) без затрат на новую конструкцию.

Ранние полупроводниковые процессы имели произвольные названия поколений (а именно, HMOS I/II/III/IV и CHMOS III/III-E/IV/V). Позже каждый процесс нового поколения стал известен как технологический узел [17] или технологический узел [18] [19] , обозначаемый минимальным размером элемента процесса в нанометрах (или исторически микрометрах ) длины транзисторного затвора процесса , например « Процесс 90 нм ». Однако с 1994 года этого не произошло [20] , а количество нанометров, используемых для обозначения технологических узлов (см. « Международную технологическую дорожную карту для полупроводников »), стало скорее маркетинговым термином, не имеющим стандартизированной связи с размерами функциональных элементов или с транзисторной плотностью (количество транзисторов на единицу площади). [21]

Первоначально длина затвора транзистора была меньше, чем предполагалось в названии технологического узла (например, узел 350 нм); однако в 2009 году эта тенденция изменилась. [20] Размеры элементов не могут иметь никакой связи с нанометрами (нм), используемыми в маркетинге. Например, прежний 10-нм техпроцесс Intel на самом деле имеет особенности (кончики ребер FinFET ) шириной 7 нм, поэтому 10-нм техпроцесс Intel аналогичен по плотности транзисторов 7-нм техпроцессу TSMC . Другой пример: 12- и 14-нм техпроцессы GlobalFoundries имеют схожие размеры элементов. [22] [23] [21]

Усовершенствованный тип технологии MOSFET , CMOS , был разработан Чи-Танг Са и Фрэнком Ванлассом из Fairchild Semiconductor в 1963 году. [24] [25] CMOS была коммерциализирована компанией RCA в конце 1960-х годов. [24] RCA коммерчески использовала КМОП для своих интегральных схем серии 4000 в 1968 году, начиная с техпроцесса 20 мкм, а затем постепенно масштабируясь до техпроцесса 10 мкм в течение следующих нескольких лет. [26] Многие первые производители полупроводниковых устройств разработали и построили собственное оборудование, такое как ионные имплантаторы. [27]

В 1963 году Гарольд М. Манасевит был первым, кто задокументировал эпитаксиальный рост кремния на сапфире , работая в подразделении Autonetics компании North American Aviation (ныне Boeing ). В 1964 году он опубликовал свои выводы вместе с коллегой Уильямом Симпсоном в Журнале прикладной физики . [28] В 1965 году К.В. Мюллер и П.Х. Робинсон изготовили MOSFET (полевой транзистор металл-оксид-полупроводник) с использованием процесса кремний-сапфир в лабораториях RCA . [29]

Производство полупроводниковых устройств с тех пор распространилось из Техаса и Калифорнии в 1960-х годах на остальной мир, включая Азию , Европу и Ближний Восток .

Размер пластин со временем увеличился с 25 мм в 1960 году до 50 мм в 1969 году, 100 мм в 1976 году, 125 мм в 1981 году, 150 мм в 1983 году и 200 мм в 1992 году. [30] [31]

В эпоху 2-дюймовых пластин их обрабатывали вручную с помощью пинцета и удерживали вручную в течение времени, необходимого для данного процесса. Пинцеты были заменены вакуумными палочками, поскольку они генерируют меньше частиц [32] , которые могут загрязнять пластины. Носители или кассеты для вафель, которые могут вмещать несколько пластин одновременно, были разработаны для перевозки нескольких пластин между этапами процесса, но пластины приходилось снимать с носителя по отдельности, обрабатывать и возвращать на носитель, поэтому для устранения необходимости были разработаны кислотостойкие носители. Это трудоемкий процесс, поэтому всю кассету с пластинами погружали в ванны для влажного травления и влажной очистки. Когда размеры пластин увеличивались до 100 мм, вся кассета часто не погружалась в воду, поскольку однородность и качество результатов по всей пластине становилось трудно контролировать. К тому времени, когда появились пластины диаметром 150 мм, кассеты уже не погружались в воду и использовались только в качестве носителей и держателей для хранения пластин, а для обработки пластин стала преобладать робототехника. При использовании пластин диаметром 200 мм ручная обработка кассет пластин становится рискованной, поскольку они тяжелее. [33]

В 1970-х годах несколько компаний перевели свою технологию производства полупроводников с биполярной на КМОП-технологию. [34] Оборудование для производства полупроводников считается дорогостоящим с 1978 года. [35]

В 1984 году KLA разработала первый автоматический прибор для проверки прицельной марки и фотомаски. [36] В 1985 году KLA разработала автоматический инструмент для контроля кремниевых пластин, который заменил ручной контроль с помощью микроскопа. [37]

В 1985 году компания STmicroelectronics изобрела BCD, также называемый BCDMOS, процесс производства полупроводников с использованием биполярных , CMOS и LDMOS устройств. [38] Его также можно сделать с помощью биполярных, CMOS и DMOS устройств. [39] Компания Applied Materials разработала первый практичный многокамерный или кластерный инструмент для обработки пластин — Precision 5000. [40]

До 1980-х годов физическое осаждение из паровой фазы было основным методом нанесения материалов на пластины, вплоть до появления химического осаждения из паровой фазы. [41] Оборудование с диффузионными насосами было заменено на оборудование с турбомолекулярными насосами, поскольку в последних не используется масло, которое часто загрязняет пластины при обработке в вакууме. [42]

Пластины диаметром 200 мм впервые были использованы для изготовления чипсов в 1990 году. Они стали стандартом до появления пластин диаметром 300 мм в 2000 году. [43] [44] Перемычки использовались при переходе от пластин диаметром 150 мм к пластинам 200 мм [45] и при переходе от пластин диаметром 200 мм к пластинам 300 мм. . [46] [47] Полупроводниковая промышленность приняла пластины большего размера, чтобы удовлетворить возросший спрос на чипы, поскольку пластины большего размера обеспечивают большую площадь поверхности на пластину. [48] Со временем индустрия перешла на пластины диаметром 300 мм, что привело к принятию FOUP, [49] но многие продукты, которые не являются передовыми, по-прежнему производятся на пластинах диаметром 200 мм, такие как аналоговые микросхемы, радиочастотные микросхемы, силовые микросхемы, BCDMOS. и МЭМС-устройства. [50] Некоторые процессы, такие как очистка, [51] ионная имплантация, [52] [53] травление, [54] отжиг [55] и окисление [56], начали использовать обработку отдельных пластин вместо пакетной обработки пластин в целях улучшения воспроизводимость результатов. [57] [58] Аналогичная тенденция существовала и в производстве МЭМС. [59] В 1998 году компания Applied Materials представила Producer, кластерный инструмент, который имел камеры, сгруппированные попарно для обработки пластин, которые имели общий вакуум и линии подачи, но в остальном были изолированы, что было революционно для того времени, поскольку предлагало более высокую производительность, чем другие инструменты. кластерные инструменты без ущерба для качества благодаря изолированной конструкции камеры. [60] [45]

Полупроводниковая промышленность сегодня является глобальным бизнесом. Ведущие производители полупроводников обычно имеют предприятия по всему миру. Samsung Electronics , крупнейший в мире производитель полупроводников, имеет предприятия в Южной Корее и США. Intel , второй по величине производитель, имеет предприятия в Европе и Азии, а также в США. TSMC , крупнейшая в мире литейная компания , имеет предприятия на Тайване, в Китае, Сингапуре и США. Qualcomm и Broadcom входят в число крупнейших компаний по производству полупроводников, не имеющих собственных производственных мощностей , и передают свое производство таким компаниям, как TSMC. [61] У них также есть объекты, разбросанные по разным странам. Поскольку среднее использование полупроводниковых устройств увеличилось, долговечность стала проблемой, и производители начали проектировать свои устройства так, чтобы они прослужили достаточно долго, и это зависит от рынка, для которого предназначено устройство. Особенно это стало проблемой на узле 10 нм. [62] [63]

Технология «кремний на изоляторе » (SOI) используется в одно-, двух-, четырех-, шести- и восьмиядерных процессорах AMD по техпроцессу 130, 90, 65, 45 и 32 нм, выпускаемых с 2001 года . В 2001 году использовалось множество мостовых инструментов, способных обрабатывать пластины диаметром от 200 до 300 мм, которые могли обрабатывать пластины диаметром 200 и 300 мм. [65] В то время 18 компаний могли производить чипы по передовому 130-нм техпроцессу. [66]

Ожидалось, что в 2006 году пластины диаметром 450 мм будут приняты на вооружение в 2012 году, а пластины диаметром 675 мм - к 2021 году. [67]

С 2009 года «узел» стал коммерческим названием в маркетинговых целях, обозначающим новые поколения технологических процессов, без какой-либо привязки к длине литника, шагу металла или шагу литника. [68] [69] [70] Например, 7-нм процесс GlobalFoundries был похож на 10-нм процесс Intel , поэтому традиционное понятие технологического узла стало размытым. [71] Кроме того, 10-нм техпроцессы TSMC и Samsung лишь немного плотнее 14-нм техпроцесса Intel по плотности транзисторов. На самом деле они гораздо ближе к 14-нм техпроцессу Intel, чем к 10-нм техпроцессу Intel (например, шаг ребер 10-нм техпроцесса Samsung точно такой же, как и у 14-нм техпроцесса Intel: 42 нм). [72] [73] Intel изменила название своего 10-нм процесса, чтобы позиционировать его как 7-нм процесс. [74] По мере того, как транзисторы становятся меньше, новые эффекты начинают влиять на проектные решения, такие как самонагрев транзисторов, а другие эффекты, такие как электромиграция, стали более очевидными после перехода на 16-нм узел. [75] [76]

В 2011 году Intel продемонстрировала полевые транзисторы Fin (FinFET), в которых затвор окружает канал с трех сторон, что позволяет повысить энергоэффективность и снизить задержку затвора — и, следовательно, повысить производительность — по сравнению с планарными транзисторами на узле 22 нм, поскольку планарные транзисторы которые имеют только одну поверхность, действующую как канал, начали страдать от эффектов коротких каналов. [77] [78] [79] [80] [81] Стартап под названием SuVolta создал технологию под названием Deeply Depleted Channel (DDC), чтобы конкурировать с транзисторами FinFET, в которых используются планарные транзисторы на узле 65 нм, которые очень слабо легированы. [82]

К 2018 году для возможной замены FinFET был предложен ряд транзисторных архитектур , большинство из которых были основаны на концепции GAAFET : [83] горизонтальные и вертикальные нанопровода, горизонтальные нанолистовые транзисторы [84] [85] (Samsung MBCFET, Intel Nanoribbon), вертикальный полевой транзистор (VFET) и другие вертикальные транзисторы, [86] [87] комплементарный полевой транзистор (CFET), многослойный полевой транзистор, вертикальные полевые транзисторы, FinFET с полупроводниковыми материалами III-V (III-V FinFET), [88] [ 89] несколько типов транзисторов с горизонтальным затвором, таких как нанокольцевые, шестиугольные, квадратные и круглые транзисторы с круглым затвором [90] и полевые транзисторы с отрицательной емкостью (NC-FET), в которых используются совершенно разные материалы. [91] FD-SOI рассматривался как потенциальная недорогая альтернатива FinFET. [92]

По состоянию на 2019 год 14-нм и 10-нм чипы находятся в массовом производстве Intel, UMC , TSMC, Samsung, Micron , SK Hynix , Toshiba Memory и GlobalFoundries, а 7-нм техпроцессы находятся в массовом производстве TSMC и Samsung, хотя их 7-нм техпроцесс определение узла аналогично 10-нанометровому процессу Intel. 5 -нанометровый процесс начал производиться компанией Samsung в 2018 году. [93] По состоянию на 2019 год узлом с самой высокой плотностью транзисторов является 5- нанометровый узел N5 от TSMC , [94] с плотностью 171,3 миллиона транзисторов на квадратный миллиметр. [95] В 2019 году Samsung и TSMC объявили о планах по производству 3-нанометровых узлов. GlobalFoundries решила остановить разработку новых узлов за пределами 12 нанометров в целях экономии ресурсов, поскольку она определила, что создание нового завода для обработки заказов менее 12 нм выйдет за рамки финансовых возможностей компании. [96]

С 2020 по 2022 год наблюдался глобальный дефицит чипов . Во время дефицита, вызванного пандемией COVID-19, многие производители полупроводников запретили сотрудникам покидать территорию компании. [97] Многие страны предоставляют субсидии полупроводниковым компаниям на строительство новых заводов или фабрик. Многие компании пострадали от поддельных чипов. [98] Полупроводники стали жизненно важными для мировой экономики и национальной безопасности некоторых стран. [99] [100] [101] США попросили TSMC не производить полупроводники для китайской компании Huawei. [102] Были исследованы CFET-транзисторы, в которых NMOS- и PMOS-транзисторы располагаются друг над другом. Были оценены два подхода к созданию этих транзисторов: монолитный подход, при котором оба типа транзисторов создавались за один процесс, и последовательный подход, при котором два типа транзисторов создавались отдельно, а затем складывались друг в друга. [103]

Это список методов обработки, которые многократно используются при создании современного электронного устройства; этот список не обязательно подразумевает конкретный заказ или то, что все методы используются во время производства, поскольку на практике порядок и применяемые методы часто зависят от технологических предложений литейных заводов или от производителя интегрированных устройств (IDM) для их собственные продукты, и для полупроводникового устройства могут не потребоваться все методы. Оборудование для проведения этих процессов производится несколькими компаниями . Перед запуском завода по производству полупроводников все оборудование должно быть протестировано. [104] Эти процессы выполняются после проектирования интегральной схемы . Фабрика по производству полупроводников работает круглосуточно и без выходных [105] , и многие фабрики используют большое количество воды, в первую очередь для промывки чипов. [106]

Дополнительно могут быть выполнены такие этапы, как травление по Райту .

Когда ширина элементов была намного больше, чем примерно 10 микрометров , чистота полупроводников не была такой большой проблемой, как сегодня при производстве устройств. В 1960-е годы рабочие могли работать над полупроводниковыми приборами в уличной одежде. [126] Поскольку устройства становятся все более интегрированными, чистые помещения должны стать еще чище. Сегодня на производственных предприятиях используется фильтрованный воздух под давлением , чтобы удалить даже мельчайшие частицы, которые могут оседать на пластинах и способствовать возникновению дефектов. Потолки чистых помещений для производства полупроводников оборудованы вентиляторными фильтрами (FFU), которые регулярно заменяют и фильтруют воздух в чистом помещении; Полупроводниковое основное оборудование также может иметь свои собственные FFU для очистки воздуха в EFEM оборудования, что позволяет оборудованию принимать пластины в FOUP. FFU в сочетании с фальшполом с решетками помогают обеспечить ламинарный поток воздуха, гарантируя, что частицы немедленно опускаются на пол и не остаются во взвешенном состоянии в воздухе из-за турбулентности. Рабочие предприятий по производству полупроводников обязаны носить костюмы для чистых помещений , чтобы защитить устройства от загрязнения людьми. [127] Для увеличения производительности FOUP и полупроводниковое основное оборудование могут иметь мини-среду с уровнем пыли класса 1 по ISO, а FOUP могут иметь еще более чистую микросреду. [11] [8] Блоки FOUP и SMIF изолируют пластины от воздуха в чистом помещении, увеличивая производительность, поскольку уменьшают количество дефектов, вызванных частицами пыли. Кроме того, на предприятиях в чистых помещениях должно находиться как можно меньше людей, чтобы облегчить поддержание чистоты помещений, поскольку люди, даже когда они носят костюмы для чистых помещений, выделяют большое количество частиц, особенно при ходьбе. [128] [127] [129]

Типичная пластина изготавливается из чрезвычайно чистого кремния , который выращивается в монокристаллические цилиндрические слитки ( були ) диаметром до 300 мм (чуть менее 12 дюймов) с использованием процесса Чохральского . Эти слитки затем нарезают на пластины толщиной около 0,75 мм и полируют до получения очень ровной и плоской поверхности. В процессе производства пластины часто группируются в партии, которые представлены ФОУП, СМИФ или вафельной кассетой, которые являются вафленосителями. FOUP и SMIF можно транспортировать на производстве между машинами и оборудованием с помощью автоматизированной системы OHT (верхнего подъемного транспорта) AMHS (автоматизированной системы погрузочно-разгрузочных работ). [49] Помимо SMIF и FOUP, кассеты с пластинами могут быть помещены в коробку для пластин или коробку для переноски пластин. [130]

При изготовлении полупроводниковых устройств различные этапы обработки делятся на четыре основные категории: нанесение, удаление, формирование рисунка и модификация электрических свойств.

Модификация электрических свойств теперь также распространяется на снижение диэлектрической проницаемости материала в изоляторах с низким κ за счет воздействия ультрафиолетового света при УФ-обработке (UVP). Модификация часто достигается путем окисления , которое может быть осуществлено для создания переходов полупроводник-изолятор, например, при локальном окислении кремния ( LOCOS ) для изготовления металлооксидных полевых транзисторов . Современные чипы имеют до одиннадцати или более уровней металла, получаемых за более чем 300 или более последовательных этапов обработки.

Рецепт в производстве полупроводников — это список условий, при которых пластина будет обрабатываться на определенном станке на этапе обработки во время производства. [146] Вариативность процесса является проблемой при обработке полупроводников, при которой пластины обрабатываются неравномерно или качество или эффективность процессов, выполняемых на пластине, неравномерны по всей поверхности пластины. [147]

Обработка FEOL подразумевает формирование транзисторов непосредственно в кремнии . Необработанная пластина создается путем выращивания сверхчистого, практически бездефектного слоя кремния посредством эпитаксии . [148] [149] В наиболее совершенных логических устройствах перед этапом эпитаксии кремния выполняются трюки, позволяющие улучшить характеристики создаваемых транзисторов. Один метод включает в себя этап деформации , на котором осаждается вариант кремния, такой как кремний-германий (SiGe). После осаждения эпитаксиального кремния кристаллическая решетка несколько растягивается, что приводит к улучшению электронной подвижности. Другой метод, называемый технологией «кремний на изоляторе», предполагает введение изолирующего слоя между необработанной кремниевой пластиной и тонким слоем последующей эпитаксии кремния. Этот метод приводит к созданию транзисторов с уменьшенными паразитными эффектами . Полупроводниковое оборудование может иметь несколько камер, в которых пластины обрабатываются такими процессами, как осаждение и травление. Многие виды оборудования обрабатывают пластины между этими камерами во внутренней среде азота или вакуума для улучшения управления процессом. [3] Влажные стенды с резервуарами, содержащими химические растворы, исторически использовались для очистки и травления пластин. [150]

В узле 90 нм были введены транзисторные каналы, изготовленные с помощью технологии тензоинжиниринга, для улучшения тока возбуждения в PMOS-транзисторах за счет введения в транзистор областей с кремний-германием. То же самое было сделано в NMOS-транзисторах на узле 20 нм [114]

В 2007 году транзисторы HKMG (high-k/металлический затвор) были представлены Intel на узле 45 нм, которые заменили поликремниевые затворы, которые, в свою очередь, заменили технологию металлических затворов (алюминиевых затворов) [151] в 1970-х годах. [152] Диэлектрик с высоким коэффициентом k, такой как оксид гафния (HFO 2 ), заменил оксинитрид кремния (SiON), чтобы предотвратить большие токи утечки в транзисторе, одновременно позволяя продолжать масштабирование или сжатие транзисторов. Однако HFO 2 несовместим с поликремниевыми затворами, поэтому требуется использование металлического затвора. В производстве использовались два подхода: «gate-first» и «gate-last». «Сначала затвор» состоит из нанесения диэлектрика с высоким коэффициентом k, а затем металла затвора, такого как нитрид тантала, рабочая функция которого зависит от того, является ли транзистор NMOS или PMOS, осаждения поликремния, формирования рисунка линии затвора, имплантации ионов истока и стока, отжига легирующей примеси и силицидирования. поликремния, истока и стока. [153] [154] В памяти DRAM эта технология была впервые применена в 2015 году. [155]

Последний этап заключался в нанесении диэлектрика с высоким κ , создании фиктивных затворов, изготовлении источников и стоков путем ионного осаждения и отжига с примесью, нанесении «межуровневого диэлектрика (ILD)», а затем полировке и удалении фиктивных затворов для замены их на металл, рабочая функция которого зависела от того, был ли транзистор NMOS или PMOS, создавая таким образом металлический затвор. Третий процесс, полное силицидирование (FUSI) [156], не был реализован из-за производственных проблем. [157] Принцип Gate-first стал доминировать на узле 22/20 нм. [158] [159] HKMG был расширен с планарных транзисторов для использования в FinFET и нанолистовых транзисторах. [160] Вместо оксида гафния также можно использовать оксинитрид кремния-гафния. [161] [162] [3] [163] [164]

Начиная с узла 16/14 нм, для травления все чаще используется атомно-слоевое травление (ALE), поскольку оно обеспечивает более высокую точность, чем другие методы травления. В производстве обычно используется плазменный АПЭ, который удаляет материалы однонаправленно, создавая конструкции с вертикальными стенками. Термический ALE также можно использовать для изотропного удаления материалов во всех направлениях одновременно, но без возможности создания вертикальных стенок. Плазменный ALE изначально был принят для травления контактов в транзисторах, а начиная с 7-нм узла он также используется для создания транзисторных структур путем их травления. [113]

За предварительной разработкой поверхности следует выращивание диэлектрика затвора (традиционно диоксида кремния ), формирование рисунка затвора, формирование рисунка областей истока и стока и последующая имплантация или диффузия легирующих примесей для получения желаемых дополнительных электрических свойств. В устройствах динамической памяти с произвольным доступом (DRAM) в это время также изготавливаются накопительные конденсаторы , обычно расположенные над транзистором доступа (ныне несуществующий производитель DRAM Qimonda реализовал эти конденсаторы с выемками, выгравированными глубоко на поверхности кремния).

После создания различных полупроводниковых устройств их необходимо соединить между собой для формирования желаемых электрических цепей. Это происходит в серии этапов обработки пластин, которые вместе называются BEOL (не путать с завершающим этапом изготовления чипов, который относится к этапам упаковки и тестирования). Обработка BEOL предполагает создание металлических соединительных проводов, изолированных диэлектрическими слоями. Изоляционный материал традиционно представлял собой SiO 2 или силикатное стекло , но в последнее время используются новые материалы с низкой диэлектрической проницаемостью , также называемые диэлектриками с низким κ (например, оксикарбид кремния), обычно обеспечивающие диэлектрическую проницаемость около 2,7 (по сравнению с 3,82 для SiO 2 ), хотя производителям микросхем предлагаются материалы с константами всего 2,2.

BEoL применяется с 1995 года на узлах 350 и 250 нм (узлы 0,35 и 0,25 микрона), тогда же стали применять химико-механическую полировку. В то время 2 металлических слоя для межсоединений, также называемые металлизацией [165], были новейшим достижением. [166]

Начиная с 22-нм узла, некоторые производители добавили новый процесс, называемый средней линией (MOL), который соединяет транзисторы с остальной частью межсоединения, выполненной в процессе BEoL. MOL часто основан на вольфраме и имеет верхний и нижний слои: нижний слой соединяет переходы транзисторов, а верхний слой представляет собой вольфрамовую заглушку, соединяющую транзисторы с межкомпонентным соединением. Intel в 10-нм узле представила технологию «контакт поверх активного затвора» (COAG), которая вместо размещения контакта для подключения транзистора рядом с затвором транзистора размещает его непосредственно над затвором транзистора для повышения плотности транзисторов. [167]

Исторически металлические проволоки состояли из алюминия . При таком подходе к проводке (часто называемом субтрактивным алюминием ) сначала наносятся поверхностные пленки алюминия, формируются рисунки, а затем травятся, оставляя изолированные провода. Затем на оголенные провода наносится диэлектрический материал. Различные металлические слои соединяются между собой путем травления отверстий (называемых « переходными отверстиями») в изолирующем материале, а затем нанесения в них вольфрама методом CVD с использованием гексафторида вольфрама ; этот подход все еще может использоваться (и часто используется) при изготовлении многих микросхем памяти, таких как динамическая память с произвольным доступом (DRAM), поскольку количество уровней межсоединений может быть небольшим (не более четырех). Алюминий иногда легировали медью для предотвращения рекристаллизации. Золото также использовалось в межсоединениях ранних чипов. [168]

Совсем недавно, когда количество уровней межсоединений для логики существенно увеличилось из-за большого количества транзисторов, которые теперь соединены между собой в современном микропроцессоре , временная задержка в проводке стала настолько значительной, что потребовала изменения материала проводки (от слой межсоединения из алюминия в медь ) [169] наряду с изменением диэлектрического материала в межсоединении (от диоксида кремния к новым изоляторам с низким κ ). [170] [171] Это повышение производительности также достигается за счет снижения затрат за счет обработки дамаска , которая исключает этапы обработки. По мере увеличения количества уровней межсоединений требуется планаризация предыдущих слоев, чтобы обеспечить плоскую поверхность перед последующей литографией. Без этого уровни становились бы все более искривленными, выходя за пределы глубины фокуса доступной литографии и, таким образом, мешая возможности создания узоров. CMP ( химико-механическая планаризация ) является основным методом обработки для достижения такой планаризации, хотя сухое обратное травление все еще иногда используется, когда количество уровней межсоединений не превышает трех. В медных межсоединениях используется электропроводящий барьерный слой, который предотвращает диффузию меди («отравление») в окружающую среду, часто состоящую из нитрида тантала. [172] [167] В 1997 году IBM первой внедрила медные межсоединения. [173]

В 2014 году компания Applied Materials предложила использовать кобальт в межсоединениях на узле 22 нм, который используется для герметизации медных межсоединений в кобальте для предотвращения электромиграции, заменяя нитрид тантала, поскольку в этом применении он должен быть толще, чем кобальт. [167] [174]

Высокосерийный характер обработки пластин увеличил спрос на метрологию между различными этапами обработки. Например, метрология тонких пленок, основанная на эллипсометрии или рефлектометрии , используется для точного контроля толщины затворного оксида, а также толщины, показателя преломления и коэффициента гашения фоторезиста и других покрытий. [175] Метрологическое оборудование для испытаний пластин используется для проверки того, что пластины не были повреждены в результате предыдущих этапов обработки вплоть до испытания; если слишком много штампов на одной пластине вышли из строя, вся пластина утилизируется, чтобы избежать затрат на дальнейшую обработку. Виртуальная метрология использовалась для прогнозирования свойств пластин на основе статистических методов без проведения самих физических измерений. [1]

После завершения процесса обработки полупроводниковые устройства или микросхемы подвергаются различным электрическим испытаниям, чтобы определить, правильно ли они функционируют. Процент устройств на пластине, которые работают правильно, называется доходом . Производители, как правило, скрывают свой выход [176] , но он может достигать 30 %, а это означает, что только 30 % чипов на пластине работают должным образом. Изменение процесса является одной из многих причин низкой производительности. Тестирование проводится для предотвращения сборки неисправных микросхем в относительно дорогие корпуса.

Выход часто, но не обязательно, зависит от размера устройства (кристалла или чипа). Например, в декабре 2019 года TSMC объявила о среднем выходе ~80% при пиковом выходе на пластину >90% для своих 5-нм тестовых чипов с размером кристалла 17,92 мм2 . Выход снизился до 32,0% при увеличении размера матрицы до 100 мм 2 . [177] Количество дефектов-убийц на пластине, независимо от размера кристалла, можно обозначить как плотность дефектов (или D 0 ) пластины на единицу площади, обычно см 2 .

Фабрика проверяет чипы на пластине с помощью электронного тестера, который прижимает крошечные зонды к чипу. Машина помечает каждый плохой чип каплей красителя. В настоящее время электронная маркировка красителем возможна, если данные испытаний пластин (результаты) заносятся в центральную компьютерную базу данных, а чипы «группируются» (т. е. сортируются в виртуальные корзины) в соответствии с заранее определенными пределами испытаний, такими как максимальные рабочие частоты/тактовые частоты, количество рабочих (полностью функциональных) ядер на чип и т. д. Полученные данные группирования можно отобразить в виде графика или записать в журнал на карте пластины, чтобы отслеживать производственные дефекты и отмечать дефектные чипы. Эту карту также можно использовать при сборке и упаковке пластин. Биннинг позволяет повторно использовать чипы, которые в противном случае были бы отклонены, в продуктах более низкого уровня, как в случае с графическими процессорами и центральными процессорами, увеличивая производительность устройства, особенно потому, что очень немногие чипы полностью функциональны (например, все ядра работают правильно). eFUSE можно использовать для отключения частей чипов, таких как ядра, либо потому, что они не работали должным образом во время объединения, либо в рамках сегментации рынка (использование одного и того же чипа для низкого, среднего и высокого уровня). Чипы могут иметь запасные части, позволяющие чипу полностью пройти тестирование, даже если у него есть несколько нерабочих частей.

Чипы также проверяются еще раз после упаковки, поскольку соединительные провода могут отсутствовать или аналоговые характеристики могут быть изменены из-за упаковки. Это называется «окончательным испытанием». Чипы также можно визуализировать с помощью рентгеновских лучей.

Обычно фабрика взимает плату за время тестирования, причем цены составляют порядка центов за секунду. Время тестирования варьируется от нескольких миллисекунд до нескольких секунд, а программное обеспечение для тестирования оптимизировано для сокращения времени тестирования. Тестирование на нескольких чипах (на нескольких площадках) также возможно, поскольку многие тестировщики имеют ресурсы для выполнения большинства или всех тестов параллельно и на нескольких чипах одновременно.

Чипы часто проектируются с «функциями тестируемости», такими как цепочки сканирования или « встроенная функция самотестирования », для ускорения тестирования и снижения затрат на тестирование. В некоторых конструкциях, в которых используются специализированные аналоговые производственные процессы, пластины также подвергаются лазерной обрезке во время испытаний, чтобы достичь плотно распределенных значений сопротивления, как указано в конструкции.

В хороших проектах стараются тестировать и статистически управлять углами (экстремальные характеристики кремния, вызванные высокой рабочей температурой в сочетании с экстремальными этапами обработки). Большинство конструкций рассчитаны как минимум на 64 угла.

Выход устройства или выход кристалла — это количество рабочих чипов или кристаллов на пластине, выраженное в процентах, поскольку количество чипов на пластине (Die на пластину, DPW) может варьироваться в зависимости от размера чипов и диаметра пластины. Снижение выхода — это снижение выхода, которое исторически было вызвано в основном частицами пыли, однако с 1990-х годов снижение выхода в основном вызвано вариациями процесса, самого процесса и инструментов, используемых при производстве чипов, хотя пыль по-прежнему остается проблемой в производстве чипов. много старых фабрик. Частицы пыли оказывают все большее влияние на производительность, поскольку размеры элементов уменьшаются в результате внедрения новых процессов. Автоматизация и использование мини-сред внутри производственного оборудования, FOUP и SMIF, позволили снизить количество дефектов, вызванных частицами пыли. Выход устройства должен поддерживаться на высоком уровне, чтобы снизить цену продажи рабочих чипов, поскольку работающим чипам приходится платить за те чипы, которые вышли из строя, а также снизить стоимость обработки пластин. На урожайность также могут влиять конструкция и эксплуатация фабрики.

Для увеличения урожайности необходим строгий контроль над загрязнителями и производственным процессом. Загрязнения могут представлять собой химические загрязнители или частицы пыли. «Смертельные дефекты» — это дефекты, вызванные частицами пыли, которые вызывают полный выход из строя устройства (например, транзистора). Есть и безобидные дефекты. Частица должна быть 1/5 размера элемента, чтобы вызвать серьезный дефект. Таким образом, если диаметр элемента составляет 100 нм, частице достаточно иметь диаметр всего 20 нм, чтобы вызвать серьезный дефект. Электростатическое электричество также может отрицательно повлиять на урожайность. Химические загрязнители или примеси включают тяжелые металлы, такие как железо, медь, никель, цинк, хром, золото, ртуть и серебро, щелочные металлы, такие как натрий, калий и литий, а также такие элементы, как алюминий, магний, кальций, хлор, сера, углерод. и фтор. Важно, чтобы эти элементы не оставались в контакте с кремнием, поскольку они могут снизить выход продукции. Для удаления этих элементов из кремния можно использовать химические смеси; разные смеси эффективны против разных элементов.

Для оценки урожайности используется несколько моделей. Это модель Мерфи, модель Пуассона, биномиальная модель, модель Мура и модель Сидса. Не существует универсальной модели; модель необходимо выбирать исходя из фактического распределения выхода (расположения дефектных чипов). Например, модель Мерфи предполагает, что потеря выхода в большей степени происходит по краям пластины (нерабочие чипы сосредоточены на краях пластины), Модель Пуассона предполагает, что дефектные кристаллы распределены по пластине относительно равномерно, а модель Сидса предполагает, что дефектные кристаллы сгруппированы вместе. [178]

Производство штампов меньшего размера обходится дешевле (поскольку больше умещается на пластине, а пластины обрабатываются и оцениваются как единое целое) и может способствовать достижению более высоких выходов, поскольку у кристаллов меньшего размера меньше шансов иметь дефекты из-за меньшей площади поверхности на пластине. вафля. Однако меньшие по размеру матрицы требуют меньших характеристик для достижения тех же функций, что и более крупные матрицы, или превосходят их, а меньшие по размеру характеристики требуют уменьшения вариаций процесса и повышенной чистоты (уменьшения загрязнения) для поддержания высоких выходов. Метрологические инструменты используются для проверки пластин во время производственного процесса и прогнозирования выхода продукции, поэтому пластины, по прогнозам, имеющие слишком много дефектов, могут быть утилизированы, чтобы сэкономить на затратах на обработку. [176]

После испытания пластину обычно уменьшают по толщине в процессе, также известном как «обратная обработка», [179] «обратная обработка», «обратная шлифовка пластины» или «утончение пластины» [180] перед тем, как пластина надрезается и затем разбивается на отдельные штампы. , процесс, известный как нарезка пластин . Упаковываются только хорошие чипсы без маркировки.

Пластиковая или керамическая упаковка предполагает установку матрицы, соединение подушечек матрицы со штифтами на упаковке и герметизацию матрицы. Крошечные соединительные провода используются для соединения площадок с контактами. В «старые времена» (1970-е годы) провода прикреплялись вручную, но теперь эту задачу выполняют специализированные машины. Традиционно эти провода состоят из золота, ведущего к свинцовой рамке (произносится как «лид-рамка») из паяной меди; свинец ядовит, поэтому теперь RoHS требует использования «свинцовых рамок», не содержащих свинец .

Пакет Chip Scale (CSP) — еще одна технология упаковки. Пластиковый двухрядный корпус , как и большинство корпусов, во много раз больше, чем реальный кристалл, спрятанный внутри, тогда как чипы CSP имеют размер почти такого же кристалла; CSP может быть построен для каждого кристалла до того, как пластина будет нарезана кубиками.

Упакованные микросхемы проверяются повторно, чтобы убедиться, что они не были повреждены во время упаковки и что операция соединения кристалла с выводом была выполнена правильно. Затем лазер гравирует название и номера чипа на упаковке.

В процессе изготовления используются многие токсичные материалы. [181] К ним относятся:

Крайне важно, чтобы работники не подвергались непосредственному воздействию этих опасных веществ. Высокая степень автоматизации, распространенная в отрасли производства микросхем, помогает снизить риски воздействия. На большинстве производственных предприятий используются системы управления выхлопными газами, такие как мокрые скрубберы, камеры сгорания, нагреваемые поглотительные картриджи и т. д., чтобы контролировать риск для работников и окружающей среды.

Следующей крупной транзисторной инновацией стало появление транзисторов FinFET (трехзатворных) по 22-нм технологии Intel в 2011 году.

{{cite book}}: CS1 maint: bot: original URL status unknown (link)