Изготовление полупроводниковых приборов — это процесс, используемый для производства полупроводниковых приборов , как правило, интегральных схем (ИС), таких как компьютерные процессоры , микроконтроллеры и чипы памяти (такие как ОЗУ и флэш-память ). Это многоэтапный фотолитографический и физико-химический процесс (с такими этапами, как термическое окисление , осаждение тонких пленок, ионная имплантация, травление), в ходе которого электронные схемы постепенно создаются на пластине , обычно изготовленной из чистого монокристаллического полупроводникового материала. Почти всегда используется кремний , но для специализированных применений используются различные составные полупроводники .

Процесс изготовления выполняется на высокоспециализированных заводах по производству полупроводников , также называемых литейными цехами или « фабриками», [1] при этом центральной частью является « чистая комната ». В более продвинутых полупроводниковых устройствах, таких как современные узлы 14/10/7 нм , изготовление может занять до 15 недель, при этом средний показатель по отрасли составляет 11–13 недель. [2] Производство на передовых производственных предприятиях полностью автоматизировано, а автоматизированные системы обработки материалов обеспечивают транспортировку пластин от машины к машине. [3]

Пластина часто имеет несколько интегральных схем, которые называются кристаллами , поскольку они являются частями, нарезанными на кубики из одной пластины. Отдельные кристаллы отделяются от готовой пластины в процессе, называемом разделением кристаллов , также называемом разделением пластин. Затем кристаллы могут подвергаться дальнейшей сборке и упаковке. [4]

На заводах-изготовителях пластины транспортируются внутри специальных герметичных пластиковых коробок, называемых FOUP . [3] FOUP на многих заводах содержат внутреннюю азотную атмосферу [5] [6] , которая помогает предотвратить окисление меди на пластинах. Медь используется в современных полупроводниках для проводки. [7] Внутренности технологического оборудования и FOUP поддерживаются чище, чем окружающий воздух в чистом помещении. Эта внутренняя атмосфера известна как мини-среда и помогает повысить выход, который представляет собой количество рабочих устройств на пластине. Эта мини-среда находится внутри EFEM (модуль переднего конца оборудования) [8] , который позволяет машине получать FOUP и вводить пластины из FOUP в машину. Кроме того, многие машины также обрабатывают пластины в чистой азотной или вакуумной среде для снижения загрязнения и улучшения управления процессом. [3] Заводам-изготовителям требуются большие объемы жидкого азота для поддержания атмосферы внутри производственного оборудования и FOUP, которые постоянно продуваются азотом. [5] [6] Между FOUP и EFEM также может быть установлена воздушная завеса или сетка [9], что помогает уменьшить количество влаги, попадающей в FOUP, и повышает урожайность. [10] [11]

Компании, производящие машины, используемые в процессе промышленного изготовления полупроводников, включают ASML , Applied Materials , Tokyo Electron и Lam Research .

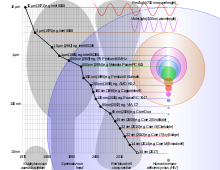

Размер элемента определяется шириной наименьших линий, которые могут быть сформированы в процессе изготовления полупроводника, это измерение известно как ширина линии. [12] [13] Формирование шаблона часто относится к фотолитографии, которая позволяет определить дизайн устройства или шаблон на устройстве во время изготовления. [14] F 2 используется как измерение площади для различных частей полупроводникового устройства, основанное на размере элемента процесса производства полупроводника. Многие полупроводниковые устройства проектируются в секциях, называемых ячейками, и каждая ячейка представляет собой небольшую часть устройства, такую как ячейка памяти для хранения данных. Таким образом, F 2 используется для измерения площади, занимаемой этими ячейками или секциями. [15]

Конкретный полупроводниковый процесс имеет определенные правила по минимальному размеру (ширина или CD/критический размер) и расстоянию для элементов на каждом слое чипа. [16] Обычно новый полупроводниковый процесс имеет меньшие минимальные размеры и более плотное расстояни. В некоторых случаях это позволяет просто уменьшить размер кристалла в текущем дизайне чипа, чтобы снизить затраты, улучшить производительность, [16] и увеличить плотность транзисторов (количество транзисторов на единицу площади) без затрат на новый дизайн.

Ранние полупроводниковые процессы имели произвольные названия для поколений (а именно, HMOS I/II/III/IV и CHMOS III/III-E/IV/V). Позже каждый новый процесс поколения стал известен как технологический узел [17] или узел процесса , [18] [19] обозначенный минимальным размером элемента процесса в нанометрах (или исторически микрометрах ) длины затвора транзистора процесса , например, « 90 нм процесс ». Однако с 1994 года это не имело места, [20] и количество нанометров, используемых для обозначения узлов процесса (см. Международную технологическую дорожную карту для полупроводников ), стало скорее маркетинговым термином, который не имеет стандартизированной связи с функциональными размерами элементов или с плотностью транзисторов (количество транзисторов на единицу площади). [21]

Первоначально длина затвора транзистора была меньше, чем предполагалось в названии узла процесса (например, узел 350 нм); однако эта тенденция изменилась в 2009 году. [20] Размеры элементов могут не иметь никакой связи с нанометрами (нм), используемыми в маркетинге. Например, бывший 10-нм процесс Intel на самом деле имеет элементы (кончики ребер FinFET ) шириной 7 нм, поэтому 10-нм процесс Intel аналогичен по плотности транзисторов 7-нм процессу TSMC . В качестве другого примера, 12-нм и 14-нм процессы GlobalFoundries имеют схожие размеры элементов. [22] [23] [21]

В 1955 году Карл Фрош и Линкольн Дерик, работая в Bell Telephone Laboratories , случайно вырастили слой диоксида кремния поверх кремниевой пластины, для которого они наблюдали эффекты пассивации поверхности. [25] [26] К 1957 году Фрош и Дерик, используя маскирование и предварительное осаждение, смогли изготовить транзисторы из диоксида кремния; первые планарные полевые транзисторы, в которых сток и исток были смежными на одной поверхности. [27] В Bell Labs важность их открытий была немедленно осознана. Записки, описывающие результаты их работы, циркулировали по Bell Labs, прежде чем были официально опубликованы в 1957 году. В Shockley Semiconductor Шокли распространил препринт своей статьи в декабре 1956 года среди всех своих старших сотрудников, включая Жана Эрни , [28] [29] [30] [31] который позже изобрел планарный процесс в 1959 году, работая в Fairchild Semiconductor . [32] [33]

В 1948 году Бардин запатентовал транзистор с изолированным затвором (IGFET) с инверсионным слоем, концепция Бардина, которая сегодня составляет основу технологии КМОП. [34] Улучшенный тип технологии МОП-транзисторов , КМОП , был разработан Чи-Тан Са и Фрэнком Ванлассом в Fairchild Semiconductor в 1963 году. [35] [36] КМОП была коммерциализирована RCA в конце 1960-х годов. [35] RCA коммерчески использовала КМОП для своих интегральных схем серии 4000 в 1968 году, начав с 20 -мкм процесса, прежде чем постепенно масштабироваться до 10-мкм процесса в течение следующих нескольких лет. [37] Многие ранние производители полупроводниковых приборов разработали и создали свое собственное оборудование, такое как ионные имплантеры. [38]

В 1963 году Гарольд М. Манасевит был первым, кто задокументировал эпитаксиальный рост кремния на сапфире, работая в подразделении Autonetics компании North American Aviation (теперь Boeing ). В 1964 году он опубликовал свои выводы с коллегой Уильямом Симпсоном в журнале Journal of Applied Physics . [39] В 1965 году CW Mueller и PH Robinson изготовили MOSFET (полевой транзистор металл-оксид-полупроводник), используя процесс кремния на сапфире в RCA Laboratories . [40]

С тех пор производство полупроводниковых приборов распространилось из Техаса и Калифорнии в 1960-х годах на остальной мир, включая Азию , Европу и Ближний Восток .

Размер пластины со временем увеличился с 25 мм в 1960 году до 50 мм в 1969 году, 100 мм в 1976 году, 125 мм в 1981 году, 150 мм в 1983 году и 200 мм в 1992 году. [41] [42]

В эпоху 2-дюймовых пластин их обрабатывали вручную с помощью пинцета и удерживали вручную в течение времени, необходимого для данного процесса. Пинцеты были заменены вакуумными зондами, поскольку они генерируют меньше частиц [43] , которые могут загрязнять пластины. Носители или кассеты для пластин, которые могут удерживать несколько пластин одновременно, были разработаны для переноса нескольких пластин между этапами процесса, но пластины приходилось по отдельности извлекать из носителя, обрабатывать и возвращать в носитель, поэтому были разработаны кислотостойкие носители, чтобы исключить этот трудоемкий процесс, поэтому вся кассета с пластинами погружалась в ванны для влажного травления и влажной очистки. Когда размеры пластин увеличились до 100 мм, вся кассета часто не погружалась так равномерно, и качество результатов по всей пластине становилось трудно контролировать. К моменту появления 150-мм пластин кассеты не были погружены в раствор и использовались только в качестве носителей и держателей пластин для хранения пластин, а робототехника стала преобладать в обращении с пластинами. С появлением 200-мм пластин ручная обработка кассет с пластинами становится рискованной, поскольку они тяжелее. [44]

В 1970-х годах несколько компаний перевели технологию производства полупроводников с биполярной на КМОП-технологию. [45] Оборудование для производства полупроводников считается дорогим с 1978 года. [46]

В 1984 году KLA разработала первый автоматический инструмент для проверки сетки и фотошаблонов. [47] В 1985 году KLA разработала автоматический инструмент для проверки кремниевых пластин, который заменил ручной микроскопический контроль. [48]

В 1985 году компания SGS (теперь STmicroelectronics ) изобрела BCD, также называемый BCDMOS , процесс производства полупроводников с использованием биполярных , КМОП и ДМОП -устройств. [49] Компания Applied Materials разработала первый практический многокамерный или кластерный инструмент для обработки пластин Precision 5000. [50]

До 1980-х годов физическое осаждение из паровой фазы было основным методом, используемым для нанесения материалов на пластины, пока не появился химический метод осаждения из паровой фазы. [51] Оборудование с диффузионными насосами было заменено на оборудование, использующее турбомолекулярные насосы, поскольку последние не используют масло, которое часто загрязняло пластины во время обработки в вакууме. [52]

Пластины диаметром 200 мм впервые были использованы в 1990 году для изготовления чипов. Они стали стандартом до введения пластин диаметром 300 мм в 2000 году. [53] [54] Мостовые инструменты использовались при переходе от 150-мм пластин к 200-мм пластинам [55] и при переходе от 200-мм к 300-мм пластинам. [56] [57] Полупроводниковая промышленность приняла более крупные пластины, чтобы справиться с возросшим спросом на чипы, поскольку более крупные пластины обеспечивают большую площадь поверхности на пластину. [58] Со временем отрасль перешла на 300-мм пластины, что повлекло за собой принятие FOUP, [59] но многие продукты, которые не являются передовыми, по-прежнему производятся на 200-мм пластинах, такие как аналоговые ИС, радиочастотные чипы, силовые ИС, BCDMOS и устройства MEMS . [60] Некоторые процессы, такие как очистка, [61] ионная имплантация, [62] [63] травление, [64] отжиг [65] и окисление [66], начали применять обработку отдельных пластин вместо пакетной обработки пластин с целью улучшения воспроизводимости результатов. [67] [68] Похожая тенденция существовала в производстве МЭМС. [69] В 1998 году компания Applied Materials представила Producer, кластерный инструмент, в котором камеры были сгруппированы попарно для обработки пластин, которые имели общие вакуумные и подводящие линии, но в остальном были изолированы, что было революционным в то время, поскольку обеспечивало более высокую производительность, чем другие кластерные инструменты, без ущерба для качества благодаря изолированной конструкции камеры. [70] [55]

Полупроводниковая промышленность сегодня является глобальным бизнесом. Ведущие производители полупроводников обычно имеют предприятия по всему миру. Samsung Electronics , крупнейший в мире производитель полупроводников, имеет предприятия в Южной Корее и США. Intel , второй по величине производитель, имеет предприятия в Европе и Азии, а также в США. TSMC , крупнейший в мире литейный завод , имеет предприятия на Тайване, в Китае, Сингапуре и США. Qualcomm и Broadcom являются одними из крупнейших полупроводниковых компаний без собственных производственных мощностей , передающих свое производство на аутсорсинг таким компаниям, как TSMC. [71] У них также есть предприятия, разбросанные по разным странам. Поскольку среднее использование полупроводниковых устройств увеличилось, долговечность стала проблемой, и производители начали проектировать свои устройства так, чтобы они работали достаточно долго, и это зависит от рынка, для которого предназначено устройство. Это стало особенно проблемой на узле 10 нм. [72] [73]

Технология «кремний на изоляторе » (SOI) использовалась в одно-, двух-, четырех-, шести- и восьмиядерных процессорах AMD 130 нм, 90 нм, 65 нм, 45 нм и 32 нм, выпущенных с 2001 года. [ 74] Во время перехода с пластин диаметром 200 мм на 300 мм в 2001 году использовалось множество мостовых инструментов, которые могли обрабатывать как пластины диаметром 200 мм, так и 300 мм. [75] В то время 18 компаний могли производить чипы по передовому 130-нм процессу. [76]

В 2006 году ожидалось, что пластины диаметром 450 мм будут приняты в 2012 году, а пластины диаметром 675 мм — к 2021 году. [77]

С 2009 года «узел» стал коммерческим названием в маркетинговых целях, которое указывает на новые поколения технологических процессов, без какой-либо связи с длиной затвора, шагом металла или шагом затвора. [78] [79] [80] Например, 7-нм процесс GlobalFoundries был похож на 10-нм процесс Intel , поэтому традиционное понятие узла процесса стало размытым. [81] Кроме того, 10-нм процессы TSMC и Samsung лишь немного плотнее, чем 14-нм процесс Intel по плотности транзисторов. На самом деле они гораздо ближе к 14-нм процессу Intel, чем к 10-нм процессу Intel (например, шаг ребер 10-нм процесса Samsung точно такой же, как и у 14-нм процесса Intel: 42 нм). [82] [83] Intel изменила название своего 10-нм процесса, чтобы позиционировать его как 7-нм процесс. [84] По мере того, как транзисторы становятся меньше, на проектные решения начинают влиять новые эффекты, такие как самонагрев транзисторов, а другие эффекты, такие как электромиграция, стали более очевидными с появлением 16-нм узла. [85] [86]

В 2011 году Intel продемонстрировала полевые транзисторы Fin (FinFET), в которых затвор окружает канал с трех сторон, что позволяет повысить энергоэффективность и снизить задержку затвора, а значит, и производительность по сравнению с планарными транзисторами на 22-нм узле, поскольку планарные транзисторы, у которых только одна поверхность действует как канал, начали страдать от эффекта короткого канала. [87] [88] [89] [90] [91] Стартап под названием SuVolta создал технологию под названием Deeply Depleted Channel (DDC) для конкуренции с FinFET-транзисторами, в которой планарные транзисторы на 65-нм узле имеют очень слабо легированные примеси. [92]

К 2018 году для возможной замены FinFET был предложен ряд транзисторных архитектур , большинство из которых были основаны на концепции GAAFET : [93] горизонтальные и вертикальные нанопровода, горизонтальные нанолистовые транзисторы [94] [95] (Samsung MBCFET, Intel Nanoribbon), вертикальные полевые транзисторы (VFET) и другие вертикальные транзисторы, [96] [97] комплементарные полевые транзисторы (CFET), многослойные полевые транзисторы, вертикальные TFET, FinFET с полупроводниковыми материалами III-V (III-V FinFET), [98] [99] несколько видов горизонтальных затворных транзисторов со сквозным затвором, таких как нанокольцевые, шестиугольные проволочные, квадратные проволочные и круглые проволочные затворные транзисторы [100] и полевые транзисторы с отрицательной емкостью (NC-FET), которые используют кардинально разные материалы. [101] FD-SOI рассматривался как потенциальная недорогая альтернатива FinFET. [102]

По состоянию на 2019 год 14-нанометровые и 10-нанометровые чипы находятся в массовом производстве Intel, UMC , TSMC, Samsung, Micron , SK Hynix , Toshiba Memory и GlobalFoundries, а 7-нанометровые чипы находятся в массовом производстве TSMC и Samsung, хотя их 7-нанометровый узел аналогичен 10-нанометровому процессу Intel. 5-нанометровый процесс начал производиться Samsung в 2018 году. [103] По состоянию на 2019 год узлом с самой высокой плотностью транзисторов является 5- нанометровый узел N5 компании TSMC [104] с плотностью 171,3 миллиона транзисторов на квадратный миллиметр. [105] В 2019 году Samsung и TSMC объявили о планах по производству 3-нанометровых узлов. Компания GlobalFoundries решила прекратить разработку новых узлов свыше 12 нм в целях экономии ресурсов, поскольку она пришла к выводу, что создание нового завода для обработки заказов с параметрами ниже 12 нм будет превышать финансовые возможности компании. [106]

С 2020 по 2022 год наблюдался глобальный дефицит чипов . Во время этого дефицита, вызванного пандемией COVID-19, многие производители полупроводников запретили сотрудникам покидать территорию компании. [107] Многие страны предоставили субсидии полупроводниковым компаниям на строительство новых производственных предприятий или фабрик. Многие компании пострадали от поддельных чипов. [108] Полупроводники стали жизненно важными для мировой экономики и национальной безопасности некоторых стран. [109] [110] [111] США попросили TSMC не производить полупроводники для китайской компании Huawei. [112] Были исследованы транзисторы CFET, которые объединяют транзисторы NMOS и PMOS друг с другом. Были оценены два подхода к созданию этих транзисторов: монолитный подход, при котором оба типа транзисторов изготавливаются в одном процессе, и последовательный подход, при котором два типа транзисторов изготавливаются отдельно, а затем объединяются. [113]

Это список методов обработки, которые используются много раз в ходе создания современного электронного устройства; этот список не обязательно подразумевает определенный порядок или то, что все методы используются во время производства, поскольку на практике порядок и применяемые методы часто являются специфическими для технологических предложений литейных заводов или специфическими для производителя интегрированных устройств (IDM) для их собственной продукции, а для полупроводникового устройства могут не потребоваться все методы. Оборудование для выполнения этих процессов производится несколькими компаниями . Все оборудование должно быть протестировано до запуска завода по производству полупроводников. [114] Эти процессы выполняются после проектирования интегральных схем . Фабрика полупроводников работает круглосуточно и без выходных [115], и многие фабрики используют большое количество воды, в основном для промывки чипов. [116]

Дополнительно могут быть выполнены такие этапы, как травление по методу Райта .

Когда ширина элементов была намного больше, чем около 10 микрометров , чистота полупроводников не была такой большой проблемой, как сегодня при производстве устройств. В 1960-х годах рабочие могли работать с полупроводниковыми устройствами в уличной одежде. [137] По мере того, как устройства становятся более интегрированными, чистые помещения должны становиться еще чище. Сегодня на производственных предприятиях создается давление с помощью отфильтрованного воздуха для удаления даже самых мелких частиц, которые могут оседать на пластинах и способствовать возникновению дефектов. Потолки чистых помещений для полупроводников оснащены вентиляторными фильтрами (FFU) с регулярными интервалами для постоянной замены и фильтрации воздуха в чистом помещении; основное полупроводниковое оборудование также может иметь свои собственные FFU для очистки воздуха в EFEM оборудования, что позволяет оборудованию принимать пластины в FOUP. FFU в сочетании с фальшполами с решетками помогают обеспечить ламинарный поток воздуха, чтобы гарантировать, что частицы немедленно опускаются на пол и не остаются подвешенными в воздухе из-за турбулентности. Работники на предприятии по производству полупроводников обязаны носить костюмы для чистых помещений , чтобы защитить устройства от загрязнения людьми. [138] Для повышения производительности FOUP и основное полупроводниковое оборудование могут иметь мини-среду с уровнем пыли класса 1 ISO, а FOUP могут иметь еще более чистую микросреду. [11] [8] FOUP и SMIF- поды изолируют пластины от воздуха в чистом помещении, увеличивая производительность, поскольку они уменьшают количество дефектов, вызванных частицами пыли. Кроме того, на фабриках в чистом помещении находится как можно меньше людей, чтобы облегчить поддержание чистоты помещения, поскольку люди, даже будучи в костюмах для чистых помещений, выделяют большое количество частиц, особенно при ходьбе. [139] [138] [140]

Типичная пластина изготавливается из чрезвычайно чистого кремния , который выращивается в монокристаллические цилиндрические слитки ( були ) диаметром до 300 мм (чуть меньше 12 дюймов) с использованием процесса Чохральского . Затем эти слитки нарезаются на пластины толщиной около 0,75 мм и полируются для получения очень ровной и плоской поверхности. В процессе производства пластины часто группируются в партии, которые представлены FOUP, SMIF или кассетой для пластин, которые являются носителями пластин. FOUP и SMIF могут транспортироваться на фабрике между машинами и оборудованием с помощью автоматизированной системы OHT (транспортировка с помощью подвесного подъемника) AMHS (автоматизированная система обработки материалов). [59] Помимо SMIF и FOUP, кассеты для пластин могут быть помещены в коробку для пластин или коробку для переноски пластин. [141]

При изготовлении полупроводниковых приборов различные этапы обработки делятся на четыре основные категории: осаждение, удаление, формирование рисунка и изменение электрических свойств.

Модификация электрических свойств теперь также распространяется на снижение диэлектрической проницаемости материала в низко-κ изоляторах посредством воздействия ультрафиолетового света при УФ-обработке (UVP). Модификация часто достигается окислением , которое может быть выполнено для создания переходов полупроводник-изолятор, например, при локальном окислении кремния ( LOCOS ) для изготовления металлооксидных полевых транзисторов . Современные чипы имеют до одиннадцати или более уровней металла, произведенных за более чем 300 или более последовательных этапов обработки.

Рецепт в производстве полупроводников представляет собой список условий, при которых пластина будет обрабатываться определенной машиной на этапе обработки в процессе производства. [157] Изменчивость процесса является проблемой в обработке полупроводников, при которой пластины обрабатываются неравномерно или качество или эффективность процессов, выполняемых на пластине, неравномерны по всей поверхности пластины. [158]

Обработка пластины разделена на этапы FEOL и BEOL. Обработка FEOL относится к формированию транзисторов непосредственно в кремнии . Необработанная пластина создается путем выращивания сверхчистого, практически бездефектного слоя кремния посредством эпитаксии . [159] [160] В самых современных логических устройствах перед этапом эпитаксии кремния применяются приемы для улучшения производительности создаваемых транзисторов. Один из методов заключается в введении этапа деформации , на котором осаждается вариант кремния, такой как кремний-германий (SiGe). После осаждения эпитаксиального кремния кристаллическая решетка несколько растягивается, что приводит к улучшению электронной подвижности. Другой метод, называемый технологией кремния на изоляторе, заключается в вставке изолирующего слоя между необработанной кремниевой пластиной и тонким слоем последующей эпитаксии кремния. Этот метод приводит к созданию транзисторов с уменьшенными паразитными эффектами . Полупроводниковое оборудование может иметь несколько камер, которые обрабатывают пластины в таких процессах, как осаждение и травление. Многие единицы оборудования обрабатывают пластины между этими камерами во внутренней среде азота или вакуума для улучшения контроля процесса. [3] Мокрые столы с резервуарами, содержащими химические растворы, исторически использовались для очистки и травления пластин. [161]

В узле 90 нм были введены каналы транзисторов, созданные с помощью деформационной инженерии, для улучшения тока управления в транзисторах PMOS путем введения областей с кремнием-германием в транзисторе. То же самое было сделано в транзисторах NMOS в узле 20 нм. [125]

В 2007 году Intel представила транзисторы HKMG (high-k/metal gate) на 45-нм узле, которые заменили поликремниевые затворы, которые, в свою очередь, заменили технологию металлических затворов (алюминиевых затворов) [162] в 1970-х годах. [163] Диэлектрик high-k, такой как оксид гафния (HfO 2 ), заменил оксинитрид кремния (SiON), чтобы предотвратить большие токи утечки в транзисторе, при этом позволяя продолжать масштабирование или сжатие транзисторов. Однако HfO 2 несовместим с поликремниевыми затворами, которые требуют использования металлического затвора. В производстве использовались два подхода: gate-first и gate-last. Gate-first состоит из осаждения диэлектрика с высоким значением k, а затем металла затвора, такого как нитрид тантала, чья рабочая функция зависит от того, является ли транзистор NMOS или PMOS, осаждения поликремния, формирования затворной линии, имплантации ионов истока и стока, отжига легирующей примеси и силицидирования поликремния, а также истока и стока. [164] [165] В памяти DRAM эта технология была впервые применена в 2015 году. [166]

Gate-last состоял из первого осаждения диэлектрика High-κ , создания фиктивных затворов, изготовления источников и стоков путем ионного осаждения и отжига легирующей примеси, осаждения «межуровневого диэлектрика (ILD)», а затем полировки и удаления фиктивных затворов для замены их металлом, рабочая функция которого зависела от того, был ли транзистор NMOS или PMOS, таким образом создавая металлический затвор. Третий процесс, полное силицидирование (FUSI) [167], не был реализован из-за производственных проблем. [168] Gate-first стал доминирующим в узле 22 нм/20 нм. [169] [170] HKMG был расширен от планарных транзисторов для использования в FinFET и нанолистовых транзисторах. [171] Гафний-кремниевый оксинитрид также может использоваться вместо оксида гафния. [172] [173] [3] [174] [175]

Начиная с узла 16 нм/14 нм, атомно-слоевое травление (ALE) все чаще используется для травления, поскольку оно обеспечивает более высокую точность, чем другие методы травления. В производстве обычно используется плазменное ALE, которое удаляет материалы однонаправленно, создавая структуры с вертикальными стенками. Термическое ALE также может использоваться для удаления материалов изотропно, во всех направлениях одновременно, но без возможности создания вертикальных стенок. Плазменное ALE изначально было принято для травления контактов в транзисторах, а начиная с узла 7 нм оно также используется для создания транзисторных структур путем их травления. [124]

За фронтальной поверхностной инженерией следует рост диэлектрика затвора (традиционно диоксида кремния ), формирование рисунка затвора, формирование рисунка областей источника и стока и последующая имплантация или диффузия легирующих примесей для получения желаемых дополнительных электрических свойств. В устройствах динамической памяти с произвольным доступом (DRAM) в это же время изготавливаются и накопительные конденсаторы , обычно размещаемые над транзистором доступа (ныне несуществующий производитель DRAM Qimonda реализовал эти конденсаторы с канавками, вытравленными глубоко в поверхности кремния).

После создания различных полупроводниковых устройств их необходимо соединить между собой, чтобы сформировать желаемые электрические цепи. Это происходит в серии этапов обработки пластин, которые в совокупности называются BEOL (не путать с конечным этапом изготовления чипов, который относится к этапам упаковки и тестирования). Обработка BEOL включает создание металлических соединительных проводов, которые изолированы диэлектрическими слоями. Изолирующим материалом традиционно является форма SiO 2 или силикатного стекла , но в последнее время используются новые материалы с низкой диэлектрической проницаемостью , также называемые диэлектриками с низким κ (например, оксикарбид кремния), обычно обеспечивающие диэлектрическую проницаемость около 2,7 (по сравнению с 3,82 для SiO 2 ), хотя производителям чипов предлагаются материалы с такой низкой проницаемостью, как 2,2.

BEoL используется с 1995 года на узлах 350 нм и 250 нм (узлы 0,35 и 0,25 микрон), в то же время начала применяться химико-механическая полировка. В то время 2 металлических слоя для межсоединений, также называемых металлизацией [176], были последним словом техники. [177]

Начиная с 22-нм узла некоторые производители добавили новый процесс, называемый middle-of-line (MOL), который соединяет транзисторы с остальной частью межсоединения, выполненного в процессе BEoL. MOL часто основан на вольфраме и имеет верхние и нижние слои: нижний слой соединяет соединения транзисторов, а верхний слой, представляющий собой вольфрамовую вилку, соединяет транзисторы с межсоединением. Intel на 10-нм узле представила контакт над активным затвором (COAG), который вместо размещения контакта для соединения транзистора близко к затвору транзистора, размещает его непосредственно над затвором транзистора для улучшения плотности транзисторов. [178]

Исторически металлические провода состояли из алюминия . В этом подходе к проводке (часто называемом субтрактивным алюминием ) сначала наносятся пленки алюминия, формируется рисунок, а затем травятся, оставляя изолированные провода. Затем на открытые провода наносится диэлектрический материал. Различные металлические слои соединяются между собой путем травления отверстий (называемых « сквозными отверстиями») в изоляционном материале, а затем в них наносится вольфрам с помощью метода химического осаждения из газовой фазы с использованием гексафторида вольфрама ; этот подход все еще может (и часто используется) использоваться при изготовлении многих микросхем памяти, таких как динамическая память с произвольным доступом (DRAM), поскольку количество уровней межсоединений может быть небольшим (не более четырех). Алюминий иногда сплавляли с медью для предотвращения рекристаллизации. Золото также использовалось в межсоединениях в ранних микросхемах. [179]

Совсем недавно, поскольку число уровней межсоединений для логики существенно возросло из-за большого числа транзисторов, которые теперь соединены между собой в современном микропроцессоре , временная задержка в проводке стала настолько значительной, что потребовалась смена материала проводки (с алюминиевого на медный межсоединительный слой) [180] наряду с изменением диэлектрического материала в межсоединении (с диоксидов кремния на более новые изоляторы с низким κ ). [181] [182] Это повышение производительности также достигается за счет снижения затрат за счет обработки дамаскина , которая устраняет этапы обработки. По мере увеличения числа уровней межсоединений требуется планаризация предыдущих слоев для обеспечения плоской поверхности перед последующей литографией. Без нее уровни становились бы все более кривыми, выходя за пределы глубины фокуса доступной литографии и, таким образом, мешая возможности шаблонизации. CMP ( химико-механическая планаризация ) является основным методом обработки для достижения такой планаризации, хотя сухое травление все еще иногда применяется, когда число уровней межсоединений не превышает трех. Медные межсоединения используют электропроводящий барьерный слой, чтобы предотвратить диффузию меди в окружающую среду («отравление»), часто из нитрида тантала. [183] [178] В 1997 году IBM была первой, кто принял медные межсоединения. [184]

В 2014 году компания Applied Materials предложила использовать кобальт в межсоединениях на 22-нм узле, применяемом для инкапсуляции медных межсоединений в кобальт для предотвращения электромиграции, заменив нитрид тантала, поскольку в этом применении он должен быть толще кобальта. [178] [185]

Высокосерийный характер обработки пластин увеличил спрос на метрологию между различными этапами обработки. Например, метрология тонких пленок, основанная на эллипсометрии или рефлектометрии, используется для строгого контроля толщины оксида затвора, а также толщины, показателя преломления и коэффициента экстинкции фоторезиста и других покрытий. [186] Оборудование/инструменты для метрологии пластин или инструменты для проверки пластин используются для проверки того, что пластины не были повреждены предыдущими этапами обработки вплоть до тестирования; если слишком много кристаллов на одной пластине вышли из строя, вся пластина отбраковывается, чтобы избежать затрат на дальнейшую обработку. Виртуальная метрология использовалась для прогнозирования свойств пластин на основе статистических методов без проведения самих физических измерений. [1]

После завершения процесса предварительной обработки полупроводниковые приборы или чипы подвергаются различным электрическим испытаниям, чтобы определить, функционируют ли они должным образом. Процент приборов на пластине, которые, как было установлено, работают должным образом, называется выходом . Производители обычно скрывают свой выход, [187] но он может быть всего лишь 30%, что означает, что только 30% чипов на пластине работают так, как задумано. Изменение процесса является одной из многих причин низкого выхода. Тестирование проводится для предотвращения сборки неисправных чипов в относительно дорогие корпуса.

Выход годных часто, но не обязательно, связан с размером устройства (кристалла или микросхемы). Например, в декабре 2019 года TSMC объявила о среднем выходе годных ~80%, с пиковым выходом годных на пластину >90% для своих 5-нм тестовых чипов с размером кристалла 17,92 мм 2 . Выход годных снизился до 32,0% при увеличении размера кристалла до 100 мм 2 . [188] Количество дефектов-убийц на пластине, независимо от размера кристалла, можно отметить как плотность дефектов (или D 0 ) пластины на единицу площади, обычно см 2 .

Фабрика тестирует чипы на пластине с помощью электронного тестера, который прижимает крошечные зонды к чипу. Машина маркирует каждый плохой чип каплей красителя. В настоящее время электронная маркировка красителем возможна, если данные (результаты) тестирования пластины регистрируются в центральной компьютерной базе данных, а чипы «бинируются» (т. е. сортируются по виртуальным ячейкам) в соответствии с заранее определенными тестовыми пределами, такими как максимальные рабочие частоты/такты, количество рабочих (полностью функциональных) ядер на чип и т. д. Полученные данные бинирования могут быть графически отображены или зарегистрированы на карте пластины для отслеживания производственных дефектов и маркировки плохих чипов. Эту карту также можно использовать во время сборки и упаковки пластины. Бинирование позволяет повторно использовать чипы, которые в противном случае были бы отклонены, в продуктах более низкого уровня, как в случае с графическими процессорами и центральными процессорами, что увеличивает выход годных устройств, особенно с учетом того, что очень немногие чипы полностью функциональны (например, имеют все ядра, функционирующие правильно). eFUSE могут использоваться для отключения частей чипов, таких как ядра, либо потому, что они не работали так, как предполагалось во время биннинга, либо в рамках сегментации рынка (использование одного и того же чипа для низкого, среднего и высокого уровней). Чипы могут иметь запасные части, чтобы чип мог полностью пройти тестирование, даже если у него есть несколько неработающих частей.

Чипы также проверяются снова после упаковки, так как соединительные провода могут отсутствовать, или аналоговые характеристики могут быть изменены упаковкой. Это называется «окончательным тестом». Чипы также могут быть визуализированы с помощью рентгеновских лучей.

Обычно фабрика взимает плату за время тестирования, цены составляют порядка центов за секунду. Время тестирования варьируется от нескольких миллисекунд до пары секунд, а тестовое программное обеспечение оптимизировано для сокращения времени тестирования. Также возможно многочиповое (многосайтовое) тестирование, поскольку у многих тестировщиков есть ресурсы для выполнения большинства или всех тестов параллельно и на нескольких чипах одновременно.

Чипы часто проектируются с "функциями тестируемости", такими как цепи сканирования или " встроенная самопроверка ", чтобы ускорить тестирование и сократить расходы на тестирование. В некоторых конструкциях, использующих специализированные аналоговые процессы FAB, пластины также подвергаются лазерной обрезке во время тестирования, чтобы достичь плотно распределенных значений сопротивления, как указано в конструкции.

Хорошие проекты пытаются протестировать и статистически управлять углами (экстремальные характеристики поведения кремния, вызванные высокой рабочей температурой в сочетании с экстремальными характеристиками этапов обработки на заводе). Большинство проектов справляются как минимум с 64 углами.

Выход годных устройств или выход кристаллов — это количество рабочих чипов или кристаллов на пластине, указанное в процентах, поскольку количество чипов на пластине (Die per wafer, DPW) может варьироваться в зависимости от размера чипов и диаметра пластины. Ухудшение выхода годных — это снижение выхода годных, которое исторически в основном вызывалось частицами пыли, однако с 1990-х годов ухудшение выхода годных в основном вызывается изменением процесса, самим процессом и инструментами, используемыми при производстве чипов, хотя пыль по-прежнему остается проблемой во многих старых фабриках. Частицы пыли оказывают все большее влияние на выход годных, поскольку размеры элементов уменьшаются с помощью новых процессов. Автоматизация и использование мини-сред внутри производственного оборудования, FOUP и SMIF позволили сократить дефекты, вызванные частицами пыли. Выход годных устройств должен поддерживаться высоким, чтобы снизить отпускную цену рабочих чипов, поскольку рабочие чипы должны оплачивать те чипы, которые вышли из строя, и снизить стоимость обработки пластин. Выход годных также может зависеть от конструкции и эксплуатации фабрики.

Для повышения выхода продукции необходим строгий контроль за загрязняющими веществами и производственным процессом. Загрязняющие вещества могут быть химическими загрязняющими веществами или частицами пыли. «Смертельные дефекты» — это те, которые вызваны частицами пыли, которые вызывают полный отказ устройства (например, транзистора). Существуют также безвредные дефекты. Частица должна быть размером 1/5 от размера элемента, чтобы вызвать смертельный дефект. Таким образом, если элемент имеет поперечник 100 нм, частице достаточно быть поперечником всего 20 нм, чтобы вызвать смертельный дефект. Электростатическое электричество также может отрицательно влиять на выход продукции. Химические загрязняющие вещества или примеси включают тяжелые металлы, такие как железо, медь, никель, цинк, хром, золото, ртуть и серебро, щелочные металлы, такие как натрий, калий и литий, и такие элементы, как алюминий, магний, кальций, хлор, сера, углерод и фтор. Важно, чтобы эти элементы не оставались в контакте с кремнием, так как они могут снизить выход продукции. Для удаления этих элементов из кремния можно использовать химические смеси; различные смеси эффективны против различных элементов.

Для оценки выхода годных используются несколько моделей. Это модель Мерфи, модель Пуассона, биномиальная модель, модель Мура и модель Сидса. Универсальной модели не существует; модель должна быть выбрана на основе фактического распределения выхода годных (расположения дефектных чипов). Например, модель Мерфи предполагает, что потеря выхода годных происходит больше на краях пластины (нерабочие чипы концентрируются на краях пластины), модель Пуассона предполагает, что дефектные кристаллы распределены относительно равномерно по всей пластине, а модель Сидса предполагает, что дефектные кристаллы сгруппированы вместе. [189]

Более мелкие матрицы обходятся дешевле в производстве (поскольку больше подходят для пластины, а пластины обрабатываются и оцениваются как единое целое), и могут помочь достичь более высоких показателей выхода, поскольку более мелкие матрицы имеют меньшую вероятность наличия дефекта из-за их меньшей площади поверхности на пластине. Однако более мелкие матрицы требуют меньших характеристик для достижения тех же функций более крупных матриц или их превзойти, а более мелкие характеристики требуют меньшего изменения процесса и большей чистоты (уменьшения загрязнения) для поддержания высокого выхода. Метрологические инструменты используются для проверки пластин во время производственного процесса и прогнозирования выхода, поэтому пластины, которые, по прогнозам, имеют слишком много дефектов, могут быть отбракованы для экономии затрат на обработку. [187]

После тестирования пластина обычно уменьшается в толщине в процессе, также известном как "backlap", [190] "backfinish", "wafer backgrind" или "wafer thinning" [191], прежде чем пластина надрезается и затем разбивается на отдельные матрицы, процесс, известный как wafer dicing . Упаковываются только хорошие, немаркированные чипы.

После проверки работоспособности и сортировки кристаллов их упаковывают. Пластиковая или керамическая упаковка включает монтаж кристалла, соединение кристалла/контактных площадок со штифтами на упаковке и герметизацию кристалла. Для соединения площадок со штифтами используются крошечные соединительные провода . В «старые времена» (1970-е годы) провода прикреплялись вручную, но теперь эту задачу выполняют специализированные машины. Традиционно эти провода были сделаны из золота, ведущего к рамке выводов (произносится как «лид-рамка») из припаянной меди; свинец ядовит, поэтому теперь RoHS предписывает использовать «свинцовые рамки» без свинца . Традиционно контактные площадки располагаются по краям кристалла, однако упаковка Flip-chip может использоваться для размещения контактных площадок по всей поверхности кристалла.

Упаковка масштаба чипа (CSP) — это еще одна технология упаковки. Пластиковый двухрядный корпус , как и большинство корпусов, во много раз больше, чем фактический кристалл, скрытый внутри, тогда как чипы CSP почти такого же размера, как кристалл; CSP может быть создан для каждого кристалла до того, как пластина будет нарезана.

Упакованные чипы повторно тестируются, чтобы убедиться, что они не были повреждены во время упаковки и что операция соединения кристалла с выводом была выполнена правильно. Затем лазер гравирует название и номера чипа на упаковке. Этапы, включающие тестирование и упаковку кристаллов, за которыми следует окончательное тестирование готовых упакованных чипов, называются back end, [192] post-fab, [193] ATMP (сборка, тестирование, маркировка и упаковка) [194] или ATP (сборка, тестирование и упаковка) производства полупроводников и могут выполняться компаниями OSAT (аутсорсинговая сборка и тестирование), которые отделены от литейных заводов полупроводников. Литейный завод — это компания или фабрика, выполняющие производственные процессы, такие как фотолитография и травление, которые являются частью front end производства полупроводников. [195] [196]

В процессе изготовления используется много токсичных материалов. [197] К ним относятся:

Крайне важно, чтобы рабочие не подвергались непосредственному воздействию этих опасных веществ. Высокая степень автоматизации, распространенная в отрасли производства ИС, помогает снизить риски воздействия. Большинство производственных предприятий используют системы управления выхлопными газами, такие как мокрые скрубберы, камеры сгорания, нагреваемые картриджи абсорбера и т. д., чтобы контролировать риск для рабочих и окружающей среды.

Следующим крупным новшеством в области транзисторов стало внедрение транзисторов FinFET (tri-gate) на 22-нм технологии Intel в 2011 году.

{{cite book}}: CS1 maint: бот: исходный статус URL неизвестен ( ссылка )