Система на кристалле или система-на-кристалле ( SoC / ˌ ˈ ɛ s oʊ s iː / ; мн. ч. SoCs / ˌ ˈ ɛ s oʊ s iː z / ) — это интегральная схема , которая объединяет большинство или все компоненты компьютера или другой электронной системы . Эти компоненты почти всегда включают в себя центральный процессор (ЦП) на кристалле , интерфейсы памяти , устройства и интерфейсы ввода/вывода , а также интерфейсы вторичного хранения , часто вместе с другими компонентами, такими как радиомодемы и графический процессор (ГП) — все на одной подложке или микрочипе. [1] SoC могут содержать цифровые , а также аналоговые , смешанные и часто радиочастотные функции обработки сигналов (в противном случае их можно рассматривать как дискретный прикладной процессор).

Более производительные SoC часто сочетаются с выделенными и физически отдельными чипами памяти и вторичного хранилища (такими как LPDDR и eUFS или eMMC соответственно), которые могут быть размещены поверх SoC в конфигурации, известной как пакет на пакете (PoP), или размещаться близко к SoC. Кроме того, SoC могут использовать отдельные беспроводные модемы (особенно модемы WWAN ). [2]

SoC объединяет микроконтроллер , микропроцессор или, возможно, несколько процессорных ядер с периферийными устройствами, такими как графический процессор , Wi-Fi и сотовые сетевые радиомодемы или один или несколько сопроцессоров . Подобно тому, как микроконтроллер объединяет микропроцессор с периферийными схемами и памятью, SoC можно рассматривать как интеграцию микроконтроллера с еще более продвинутыми периферийными устройствами .

По сравнению с многочиповой архитектурой SoC с эквивалентной функциональностью будет иметь сниженное энергопотребление , а также меньшую площадь кристалла полупроводника . Это достигается за счет снижения заменяемости компонентов. По определению, конструкции SoC полностью или почти полностью интегрированы в различных компонентных модулях . По этим причинам наблюдается общая тенденция к более тесной интеграции компонентов в индустрии компьютерного оборудования , отчасти из-за влияния SoC и уроков, извлеченных из рынков мобильных и встраиваемых вычислений.

SoC очень распространены на рынках мобильных вычислений (например, в интеллектуальных устройствах, таких как смартфоны и планшетные компьютеры ) и периферийных вычислений . [3] [4]

В целом, существует три различных типа SoC:

SoC могут применяться для любой вычислительной задачи. Однако обычно они используются в мобильных вычислениях, таких как планшеты, смартфоны, умные часы и нетбуки, а также во встраиваемых системах и в приложениях, где ранее использовались микроконтроллеры .

Там, где раньше можно было использовать только микроконтроллеры, SoC становятся все более заметными на рынке встраиваемых систем. Более тесная системная интеграция обеспечивает лучшую надежность и среднее время между отказами , а SoC предлагают более продвинутую функциональность и вычислительную мощность, чем микроконтроллеры. [5] Приложения включают ускорение ИИ , встроенное машинное зрение , [6] сбор данных , телеметрию , векторную обработку и окружающий интеллект . Часто встраиваемые SoC нацелены на рынки Интернета вещей , мультимедиа, сетей, телекоммуникаций и периферийных вычислений . Вот некоторые примеры SoC для встраиваемых приложений:

SoC на базе мобильных вычислений всегда объединяют процессоры, память, кэши на чипе , возможности беспроводной сети и часто аппаратное обеспечение и прошивку цифровой камеры . С увеличением размеров памяти, высокопроизводительные SoC часто не будут иметь памяти и флэш-накопителей, а вместо этого память и флэш-память будут располагаться прямо рядом с SoC или над ним ( package on package ). [7] Вот некоторые примеры SoC для мобильных вычислений:

В 1992 году компания Acorn Computers выпустила линейки персональных компьютеров A3010, A3020 и A4000 с SoC ARM250. Он объединил оригинальный процессор Acorn ARM2 с контроллером памяти (MEMC), видеоконтроллером (VIDC) и контроллером ввода-вывода (IOC). В предыдущих компьютерах Acorn на базе ARM это были четыре дискретных чипа. Чип ARM7500 был их SoC второго поколения, основанным на контроллерах ARM700, VIDC20 и IOMD, и широко лицензировался во встраиваемых устройствах, таких как телевизионные приставки, а также в более поздних персональных компьютерах Acorn.

Производители планшетов и ноутбуков извлекли уроки из опыта рынков встраиваемых систем и смартфонов, касающиеся снижения энергопотребления, повышения производительности и надежности за счет более тесной интеграции аппаратных и микропрограммных модулей , а также LTE и других беспроводных сетевых коммуникаций, интегрированных в чип (интегрированные контроллеры сетевого интерфейса ). [10]

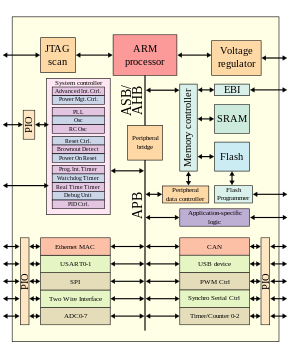

SoC состоит из аппаратных функциональных блоков , включая микропроцессоры , на которых выполняется программный код , а также подсистемы связи для соединения, управления, направления и взаимодействия между этими функциональными модулями.

SoC должен иметь по крайней мере одно ядро процессора , но обычно SoC имеет более одного ядра. Ядра процессора могут быть микроконтроллером , микропроцессором (μP), [11] цифровым сигнальным процессором (DSP) или ядром процессора набора инструкций специального приложения (ASIP). [12] ASIP имеют наборы инструкций , которые настраиваются для домена приложения и разработаны так, чтобы быть более эффективными, чем инструкции общего назначения для определенного типа рабочей нагрузки. Многопроцессорные SoC имеют более одного ядра процессора по определению. Архитектура ARM является распространенным выбором для ядер процессора SoC, поскольку некоторые ядра архитектуры ARM являются программными процессорами, указанными как ядра IP . [11]

SoC должны иметь блоки полупроводниковой памяти для выполнения своих вычислений, как и микроконтроллеры и другие встроенные системы . В зависимости от приложения память SoC может образовывать иерархию памяти и иерархию кэша . На рынке мобильных вычислений это распространено, но во многих маломощных встроенных микроконтроллерах это не обязательно. Технологии памяти для SoC включают постоянное запоминающее устройство (ROM), оперативное запоминающее устройство (RAM), электрически стираемое программируемое ПЗУ ( EEPROM ) и флэш-память . [11] Как и в других компьютерных системах, RAM можно подразделить на относительно более быструю, но более дорогую статическую RAM (SRAM) и более медленную, но дешевую динамическую RAM (DRAM). Когда SoC имеет иерархию кэша , SRAM обычно будет использоваться для реализации регистров процессора и встроенных кэшей ядер , тогда как DRAM будет использоваться для основной памяти . «Основная память» может быть специфична для одного процессора (который может быть многоядерным ), когда SoC имеет несколько процессоров ; в этом случае это распределенная память , и для доступа к ней другого процессора она должна быть отправлена через § Межмодульное взаимодействие на кристалле. [12] Для дальнейшего обсуждения проблем многопроцессорной памяти см. разделы когерентность кэша и задержка памяти .

SoC включают внешние интерфейсы , как правило, для протоколов связи . Они часто основаны на промышленных стандартах, таких как USB , Ethernet , USART , SPI , HDMI , I²C , CSI и т. д. Эти интерфейсы будут различаться в зависимости от предполагаемого применения. Также могут поддерживаться беспроводные сетевые протоколы, такие как Wi-Fi , Bluetooth , 6LoWPAN и ближняя беспроводная связь .

При необходимости SoC включают аналоговые интерфейсы, включая аналого-цифровые и цифро-аналоговые преобразователи , часто для обработки сигналов . Они могут взаимодействовать с различными типами датчиков или исполнительных механизмов , включая интеллектуальные преобразователи . Они могут взаимодействовать с модулями или щитами, предназначенными для конкретных приложений. [nb 1] Или они могут быть внутренними по отношению к SoC, например, если аналоговый датчик встроен в SoC и его показания должны быть преобразованы в цифровые сигналы для математической обработки.

Ядра цифрового сигнального процессора (DSP) часто включаются в SoC. Они выполняют операции обработки сигналов в SoC для датчиков , исполнительных механизмов , сбора данных , анализа данных и обработки мультимедиа. Ядра DSP обычно имеют архитектуры набора инструкций с очень длинным командным словом (VLIW) и одной командой, несколькими данными (SIMD) , и поэтому в высшей степени поддаются использованию параллелизма на уровне инструкций посредством параллельной обработки и суперскалярного выполнения . [12] : 4 Ядра SP чаще всего имеют инструкции, специфичные для приложения, и как таковые, как правило, являются процессорами набора инструкций, специфичных для приложения (ASIP). Такие инструкции, специфичные для приложения, соответствуют выделенным аппаратным функциональным блокам , которые вычисляют эти инструкции.

Типичные инструкции ЦОС включают в себя умножение с накоплением , быстрое преобразование Фурье , объединенное умножение с сложением и свертки .

Как и в случае с другими компьютерными системами, SoC требуют источников синхронизации для генерации тактовых сигналов , управления выполнением функций SoC и предоставления временного контекста для приложений обработки сигналов SoC, если это необходимо. Популярными источниками времени являются кварцевые генераторы и контуры фазовой автоподстройки частоты .

SoC- периферия, включая счетчики -таймеры, таймеры реального времени и генераторы сброса при включении питания . SoC также включают регуляторы напряжения и схемы управления питанием .

SoC включают в себя множество исполнительных блоков . Эти блоки должны часто отправлять данные и инструкции туда и обратно. Из-за этого все, кроме самых тривиальных SoC, требуют коммуникационных подсистем . Первоначально, как и в других микрокомпьютерных технологиях, использовались архитектуры шин данных , но в последнее время конструкции, основанные на разреженных сетях взаимодействия, известных как сети на кристалле (NoC), стали популярными и, как ожидается, в ближайшем будущем обгонят архитектуры шин для проектирования SoC. [13]

Исторически общая глобальная компьютерная шина обычно соединяла различные компоненты, также называемые «блоками» SoC. [13] Очень распространенной шиной для коммуникаций SoC является стандарт ARM, не требующий лицензионных отчислений, Advanced Microcontroller Bus Architecture ( AMBA ).

Контроллеры прямого доступа к памяти направляют данные напрямую между внешними интерфейсами и памятью SoC, минуя ЦП или блок управления , тем самым увеличивая пропускную способность данных SoC. Это похоже на некоторые драйверы периферийных устройств на многокристальных модульных архитектурах ПК на основе компонентов.

Задержка проводов не масштабируется из-за продолжающейся миниатюризации , производительность системы не масштабируется с количеством присоединенных ядер, рабочая частота SoC должна уменьшаться с каждым дополнительным присоединенным ядром, чтобы питание было устойчивым, а длинные провода потребляют большое количество электроэнергии. Эти проблемы не позволяют поддерживать многоядерные системы на чипе. [13] : xiii

В конце 2010-х годов появилась тенденция внедрения SoC- системами коммуникационных подсистем в терминах сетевой топологии вместо протоколов на основе шины . Тенденция к увеличению числа процессорных ядер в SoC-системах привела к тому, что эффективность связи на кристалле стала одним из ключевых факторов, определяющих общую производительность и стоимость системы. [13] : xiii Это привело к появлению сетей взаимосвязей с коммутацией пакетов на основе маршрутизатора, известных как « сети на кристалле » (NoC), для преодоления узких мест сетей на основе шины. [13] : xiii

Сети на кристалле имеют такие преимущества, как маршрутизация , зависящая от назначения и приложения , более высокая энергоэффективность и сниженная вероятность конфликта шин . Архитектуры сетей на кристалле черпают вдохновение из протоколов связи , таких как TCP и набор протоколов Интернета для связи на кристалле, [13] хотя они, как правило, имеют меньше сетевых уровней . Оптимальные архитектуры сетей на кристалле являются постоянной областью большого исследовательского интереса. Архитектуры NoC варьируются от традиционных топологий распределенных вычислительных сетей, таких как тор , гиперкуб , сетки и древовидные сети, до планирования генетических алгоритмов и рандомизированных алгоритмов, таких как случайные блуждания с ветвлением и рандомизированным временем жизни (TTL).

Многие исследователи SoC считают, что архитектуры NoC являются будущим проектирования SoC, поскольку они, как было показано, эффективно удовлетворяют потребности в мощности и пропускной способности конструкций SoC. Текущие архитектуры NoC являются двумерными. Проектирование 2D IC имеет ограниченные возможности планировки этажей , поскольку количество ядер в SoC увеличивается, поэтому с появлением трехмерных интегральных схем (3DIC) проектировщики SoC стремятся создавать трехмерные сети на кристалле, известные как 3DNoC. [13]

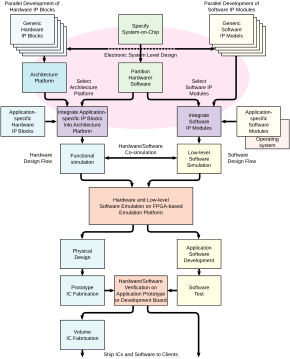

Система на кристалле состоит из аппаратного обеспечения , описанного в § Структура, и программного обеспечения, управляющего микроконтроллером, микропроцессором или ядрами цифрового сигнального процессора, периферийными устройствами и интерфейсами. Поток проектирования для SoC направлен на одновременную разработку этого аппаратного и программного обеспечения, также известного как архитектурное совместное проектирование. Поток проектирования также должен учитывать оптимизации (§ Цели оптимизации) и ограничения.

Большинство SoC разрабатываются на основе предварительно квалифицированных спецификаций IP-ядер аппаратных компонентов для аппаратных элементов и исполнительных устройств , в совокупности «блоков», описанных выше, вместе с программными драйверами устройств , которые могут управлять их работой. Особое значение имеют стеки протоколов , которые управляют стандартными интерфейсами, такими как USB . Аппаратные блоки собираются с использованием средств автоматизированного проектирования , в частности, средств автоматизации электронного проектирования ; программные модули интегрируются с использованием интегрированной среды разработки программного обеспечения .

Компоненты SoC также часто проектируются на языках программирования высокого уровня, таких как C++ , MATLAB или SystemC, и преобразуются в проекты RTL с помощью инструментов синтеза высокого уровня (HLS), таких как C в HDL или поток в HDL . [14] Продукты HLS, называемые «алгоритмическим синтезом», позволяют разработчикам использовать C++ для моделирования и синтеза систем, схем, программного обеспечения и уровней проверки на одном языке высокого уровня, обычно известном компьютерным инженерам, способом, независимым от временных масштабов, которые обычно указаны в HDL. [15] Другие компоненты могут оставаться программными и компилироваться и встраиваться в программные процессоры, включенные в SoC в качестве модулей в HDL как IP-ядра .

После определения архитектуры SoC любые новые элементы оборудования записываются на абстрактном языке описания оборудования , называемом уровнем передачи регистров (RTL), который определяет поведение схемы, или синтезируются в RTL из языка высокого уровня посредством синтеза высокого уровня. Эти элементы соединяются вместе на языке описания оборудования для создания полной конструкции SoC. Логика, указанная для соединения этих компонентов и преобразования между, возможно, различными интерфейсами, предоставляемыми разными поставщиками, называется связующей логикой .

Чипы проверяются на корректность проверки перед отправкой на литейный завод полупроводников . Этот процесс называется функциональной проверкой и составляет значительную часть времени и энергии, затрачиваемых на жизненный цикл проектирования чипа , часто называемую 70%. [16] [17] С ростом сложности чипов используются языки аппаратной проверки, такие как SystemVerilog , SystemC , e и OpenVera . Ошибки , обнаруженные на этапе проверки, сообщаются проектировщику.

Традиционно инженеры использовали ускорение моделирования, эмуляцию или прототипирование на перепрограммируемом оборудовании для проверки и отладки оборудования и программного обеспечения для проектов SoC до завершения проекта, известного как tape-out . Программируемые пользователем вентильные матрицы (FPGA) являются предпочтительными для прототипирования SoC, поскольку прототипы FPGA перепрограммируемы, допускают отладку и более гибки, чем специализированные интегральные схемы (ASIC). [18] [19]

Благодаря высокой емкости и быстрому времени компиляции, ускорение моделирования и эмуляция являются мощными технологиями, которые обеспечивают широкую видимость систем. Однако обе технологии работают медленно, порядка МГц, что может быть значительно медленнее — до 100 раз медленнее — рабочей частоты SoC. Блоки ускорения и эмуляции также очень большие и дорогие — более 1 миллиона долларов США. [ необходима цитата ]

Прототипы FPGA, напротив, используют FPGA напрямую, чтобы инженеры могли проверять и тестировать на полной рабочей частоте системы или близкой к ней с реальными стимулами. Такие инструменты, как Certus [20], используются для вставки зондов в RTL FPGA, которые делают сигналы доступными для наблюдения. Это используется для отладки аппаратных, встроенных и программных взаимодействий между несколькими FPGA с возможностями, аналогичными логическому анализатору.

Параллельно элементы оборудования группируются и проходят через процесс логического синтеза , в ходе которого применяются ограничения производительности, такие как рабочая частота и ожидаемые задержки сигнала. Это генерирует вывод, известный как netlist, описывающий конструкцию как физическую схему и ее взаимосвязи. Эти netlists объединяются с клеевой логикой , соединяющей компоненты, для создания схематического описания SoC как схемы, которая может быть напечатана на чипе. Этот процесс известен как place and route и предшествует tape-out в случае, если SoC производятся как специализированные интегральные схемы (ASIC).

SoC должны оптимизировать использование мощности , площадь на кристалле , связь, позиционирование для локальности между модульными блоками и другие факторы. Оптимизация обязательно является целью проектирования SoC. Если бы оптимизация не была необходима, инженеры использовали бы многочиповую модульную архитектуру без учета использования площади, энергопотребления или производительности системы в той же степени.

Далее следуют общие цели оптимизации для проектов SoC с пояснениями по каждой из них. В общем, оптимизация любой из этих величин может быть сложной комбинаторной задачей оптимизации и действительно может быть довольно легко NP-трудной . Поэтому часто требуются сложные алгоритмы оптимизации , и в некоторых случаях может быть практично использовать алгоритмы аппроксимации или эвристики . Кроме того, большинство проектов SoC содержат несколько переменных для одновременной оптимизации , поэтому при проектировании SoC ищут эффективные по Парето решения. Часто цели оптимизации некоторых из этих величин напрямую противоречат друг другу, что еще больше усложняет оптимизацию проекта SoC и вносит компромиссы в проектирование системы.

Более широкий охват компромиссов и анализа требований см. в разделе «Инженерия требований» .

SoC оптимизированы для минимизации электроэнергии , используемой для выполнения функций SoC. Большинство SoC должны потреблять мало энергии. Системы SoC часто требуют длительного срока службы батареи (например, смартфоны ), могут потенциально проводить месяцы или годы без источника питания, при этом им необходимо поддерживать автономную работу, и часто они ограничены в использовании энергии большим количеством встроенных SoC, объединенных в сеть в одной области. Кроме того, затраты на электроэнергию могут быть высокими, и экономия энергии снизит общую стоимость владения SoC. Наконец, отработанное тепло от высокого потребления энергии может повредить другие компоненты схемы, если рассеивается слишком много тепла, что дает еще одну прагматическую причину для экономии энергии. Количество энергии, используемой в схеме, является интегралом потребляемой мощности по времени, а средняя скорость потребления энергии является произведением тока на напряжение . Эквивалентно, по закону Ома , мощность равна квадрату тока, умноженному на сопротивление, или квадрату напряжения, деленному на сопротивление :

SoC часто встраиваются в портативные устройства , такие как смартфоны , устройства GPS-навигации , цифровые часы (включая смарт-часы ) и нетбуки . Клиенты хотят, чтобы мобильные вычислительные устройства работали долго , и это еще одна причина, по которой энергопотребление в SoC должно быть сведено к минимуму. На этих устройствах часто выполняются мультимедийные приложения , включая видеоигры, потоковое видео , обработку изображений ; все они в последние годы стали более сложными в вычислительной технике из-за требований и ожиданий пользователей в отношении более качественного мультимедиа. Вычисления становятся все более требовательными, поскольку ожидания смещаются в сторону 3D-видео с высоким разрешением и несколькими стандартами , поэтому SoC, выполняющие мультимедийные задачи, должны быть вычислительно способной платформой, при этом потребляя мало энергии, чтобы работать от стандартной мобильной батареи. [12] : 3

SoC оптимизированы для максимизации энергоэффективности в производительности на ватт: максимизируйте производительность SoC с учетом бюджета энергопотребления. Многие приложения, такие как периферийные вычисления , распределенная обработка и окружающий интеллект, требуют определенного уровня вычислительной производительности , но мощность ограничена в большинстве сред SoC.

Конструкции SoC оптимизированы для минимизации отвода тепла на кристалле. Как и в случае с другими интегральными схемами , тепло, выделяемое из-за высокой плотности мощности , является узким местом для дальнейшей миниатюризации компонентов. [21] : 1 Плотности мощности высокоскоростных интегральных схем, особенно микропроцессоров и включая SoC, стали крайне неравномерными. Слишком большое количество отводимого тепла может повредить схемы и со временем снизить надежность схемы. Высокие температуры и термические нагрузки отрицательно влияют на надежность, миграцию напряжений , уменьшение среднего времени между отказами , электромиграцию , соединение проводов , метастабильность и другие ухудшения производительности SoC с течением времени. [21] : 2–9

В частности, большинство SoC находятся в небольшой физической области или объеме, и поэтому эффекты отходящего тепла усугубляются, поскольку для него мало места, чтобы рассеиваться из системы. Из-за большого количества транзисторов в современных устройствах, часто компоновка достаточной пропускной способности и высокой плотности транзисторов физически реализуема в процессах изготовления , но приведет к неприемлемо высокому количеству тепла в объеме схемы. [21] : 1

Эти тепловые эффекты заставляют SoC и других разработчиков микросхем применять консервативные проектные запасы , создавая менее производительные устройства для снижения риска катастрофического отказа . Из-за увеличения плотности транзисторов по мере уменьшения масштабов длины каждое поколение процесса производит больше тепла, чем предыдущее. Усугубляя эту проблему, архитектуры SoC обычно неоднородны, создавая пространственно неоднородные тепловые потоки , которые не могут быть эффективно смягчены равномерным пассивным охлаждением . [21] : 1

SoC оптимизированы для максимального увеличения вычислительной и коммуникационной производительности .

SoC оптимизированы для минимизации задержки для некоторых или всех их функций. Это может быть достигнуто путем размещения элементов с надлежащей близостью и локальностью друг к другу, чтобы минимизировать задержки взаимосвязей и максимизировать скорость, с которой данные передаются между модулями, функциональными блоками и памятью. В общем, оптимизация для минимизации задержки является NP-полной задачей, эквивалентной задаче выполнимости булевых уравнений .

Для задач, работающих на ядрах процессора, задержка и пропускная способность могут быть улучшены с помощью планирования задач . Однако некоторые задачи выполняются в аппаратных блоках, специфичных для приложений, и даже планирование задач может быть недостаточным для оптимизации всех программных задач для соблюдения ограничений по времени и пропускной способности.

Системы на кристалле моделируются с использованием стандартных методов верификации и валидации оборудования , но для моделирования и оптимизации альтернативных вариантов конструкции SoC используются дополнительные методы, чтобы сделать систему оптимальной с точки зрения многокритериального анализа решений по вышеуказанным целям оптимизации.

Планирование задач является важной деятельностью в любой компьютерной системе с несколькими процессами или потоками, совместно использующими одно ядро процессора. Важно уменьшить § Задержку и увеличить § Пропускную способность для встроенного программного обеспечения, работающего на § Ядрах процессора SoC. Не все важные вычислительные действия в SoC выполняются в программном обеспечении, работающем на процессорах на кристалле, но планирование может радикально улучшить производительность программных задач и других задач, включающих общие ресурсы .

Программное обеспечение, работающее на SoC, часто планирует задачи в соответствии с сетевым планированием и алгоритмами рандомизированного планирования .

Аппаратные и программные задачи часто конвейеризируются в конструкции процессора . Конвейеризация является важным принципом ускорения в архитектуре компьютера . Они часто используются в графических процессорах ( графический конвейер ) и процессорах RISC (эволюция классического конвейера RISC ), но также применяются к задачам, специфичным для приложений, таким как цифровая обработка сигналов и манипуляции мультимедиа в контексте SoC. [12]

SoC часто анализируются с помощью вероятностных моделей , сетей очередей и цепей Маркова . Например, закон Литтла позволяет моделировать состояния SoC и буферы NoC как процессы прибытия и анализировать их с помощью случайных величин Пуассона и процессов Пуассона .

SoC часто моделируются с помощью цепей Маркова , как с дискретным , так и с непрерывным временем . Моделирование цепей Маркова позволяет проводить асимптотический анализ распределения стационарного состояния SoC [ сломанный якорь ] мощности, тепла, задержки и других факторов, что позволяет оптимизировать проектные решения для общего случая.

Микросхемы SoC обычно изготавливаются с использованием технологии металл-оксид-полупроводник (МОП). [22] Описанные выше списки соединений используются в качестве основы для потока физического проектирования ( место и маршрут ) для преобразования намерений проектировщиков в проект SoC. На протяжении всего процесса преобразования проект анализируется с помощью статического моделирования синхронизации, симуляции и других инструментов, чтобы гарантировать, что он соответствует указанным эксплуатационным параметрам, таким как частота, энергопотребление и рассеивание энергии, функциональная целостность (как описано в коде уровня передачи регистра) и электрическая целостность.

После исправления всех известных ошибок и их повторной проверки, а также после завершения всех проверок физического дизайна, файлы физического дизайна, описывающие каждый слой чипа, отправляются в цех масок литейного завода, где будет протравлен полный набор стеклянных литографических масок. Их отправляют на завод по производству пластин для создания кристаллов SoC перед упаковкой и тестированием.

SoC могут быть изготовлены с использованием нескольких технологий, включая:

ASIC потребляют меньше энергии и работают быстрее, чем FPGA, но не могут быть перепрограммированы и дороги в производстве. Конструкции FPGA больше подходят для проектов с меньшим объемом производства, но после достаточного количества единиц производства ASIC снижают общую стоимость владения. [23]

SoC-конструкции потребляют меньше энергии, имеют меньшую стоимость и большую надежность, чем многочиповые системы, которые они заменяют. При меньшем количестве пакетов в системе также снижаются затраты на сборку.

Однако, как и в большинстве проектов сверхбольшой интеграции (СБИС), общая стоимость [ требуется разъяснение ] выше для одной большой микросхемы, чем для той же функциональности, распределенной по нескольким меньшим микросхемам, из-за более низкого выхода [ требуется разъяснение ] и более высоких единовременных затрат на проектирование.

Когда не представляется возможным построить SoC для конкретного приложения, альтернативой является система в корпусе (SiP), включающая несколько чипов в одном корпусе . При производстве в больших объемах SoC более рентабельна, чем SiP, поскольку ее упаковка проще. [24] Другая причина, по которой SiP может быть предпочтительнее, заключается в том, что отходящее тепло может быть слишком высоким в SoC для данной цели, поскольку функциональные компоненты расположены слишком близко друг к другу, а в SiP тепло будет лучше рассеиваться от различных функциональных модулей, поскольку они физически дальше друг от друга.

Вот несколько примеров систем на кристалле:

Исследования и разработки SoC часто сравнивают множество вариантов. Для помощи в таких оценках разрабатываются бенчмарки, такие как COSMIC [25] .

собеседованиях большинство интервьюеров задают вопросы на тему "В чем разница между проверкой и валидацией?" Многие используют термины "верификация" и "валидация" как взаимозаменяемые, но оба имеют разное значение.