В электронике полевой транзистор металл-оксид-полупроводник ( МОП -транзистор , МОП-ПТ , МОП-транзистор , или МОП-транзистор ) представляет собой тип полевого транзистора (FET), чаще всего изготавливаемый путем контролируемого окисления кремния . Он имеет изолированный затвор, напряжение которого определяет проводимость устройства. Эта способность изменять проводимость в зависимости от величины приложенного напряжения может использоваться для усиления или переключения электронных сигналов . Термин полевой транзистор металл-изолятор-полупроводник ( MISFET ) является почти синонимом MOSFET . Другим почти синонимом является полевой транзистор с изолированным затвором ( IGFET ).

Главное преимущество MOSFET заключается в том, что он почти не требует входного тока для управления током нагрузки по сравнению с биполярными транзисторами (BJT). В MOSFET в режиме улучшения напряжение, приложенное к затвору, увеличивает проводимость устройства. В транзисторах в режиме истощения напряжение, приложенное к затвору, уменьшает проводимость. [1]

«Металл» в названии MOSFET иногда является неправильным употреблением , поскольку материалом затвора может быть слой поликремния (поликристаллического кремния). Аналогично, «оксид» в названии также может быть неправильным употреблением, поскольку используются различные диэлектрические материалы с целью получения прочных каналов с меньшими приложенными напряжениями.

MOSFET — это, безусловно, самый распространенный транзистор в цифровых схемах, поскольку в чип памяти или микропроцессор могут быть включены миллиарды. Поскольку MOSFET могут быть изготовлены с использованием полупроводников p-типа или n-типа, комплементарные пары MOS-транзисторов могут использоваться для создания схем переключения с очень низким энергопотреблением в виде логики CMOS .

Основной принцип полевого транзистора был впервые запатентован Юлиусом Эдгаром Лилиенфельдом в 1925 году. [2] В 1934 году изобретатель Оскар Хайль независимо запатентовал аналогичное устройство в Европе. [3]

В 1940-х годах ученые Bell Labs Уильям Шокли , Джон Бардин и Уолтер Хаузер Браттейн попытались построить полевой прибор, что привело к открытию ими транзисторного эффекта. Однако структура не продемонстрировала ожидаемых эффектов из-за проблемы поверхностных состояний : ловушек на поверхности полупроводника, которые удерживают электроны неподвижными. Без пассивации поверхности они смогли построить только биполярные плоскостные транзисторы и тиристорные транзисторы.

В 1955 году Карл Фрош и Линкольн Дерик случайно вырастили слой диоксида кремния поверх кремниевой пластины, для которого они наблюдали эффекты пассивации поверхности. [4] [5] К 1957 году Фрош и Дерик, используя маскирование и предварительное осаждение, смогли изготовить полевые транзисторы на основе диоксида кремния; первые планарные транзисторы, в которых сток и исток были расположены рядом на одной поверхности. [6] Они показали, что диоксид кремния изолирует, защищает кремниевые пластины и предотвращает диффузию легирующих примесей в пластину. [4] [7] В Bell Labs важность техники Фроша и Дерика и транзисторов была немедленно осознана. Результаты их работы распространялись в Bell Labs в форме служебных записок BTL, прежде чем были опубликованы в 1957 году. В Shockley Semiconductor Шокли распространил препринт своей статьи в декабре 1956 года среди всех своих старших сотрудников, включая Жана Эрни , [8] [9] [10] [11] , который позже , в 1959 году, работая в Fairchild Semiconductor, изобрел планарный процесс . [12] [13]

После этого JR Ligenza и WG Spitzer изучили механизм термически выращенных оксидов, изготовили высококачественный стек Si/ SiO2 и опубликовали свои результаты в 1960 году. [15] [16] [17] После этого исследования Мохамед Аталла и Давон Канг предложили кремниевый МОП-транзистор в 1959 году [18] и успешно продемонстрировали работающее МОП-устройство со своей командой из Bell Labs в 1960 году. [19] [20] В их команду входили EE LaBate и EI Povilonis, которые изготовили устройство; MO Thurston, LA D'Asaro и JR Ligenza, которые разработали процессы диффузии, а также HK Gummel и R. Lindner, которые охарактеризовали устройство. [21] [22] Это стало кульминацией десятилетий исследований полевых эффектов, которые начались с Лилиенфельда.

Первый МОП-транзистор в Bell Labs был примерно в 100 раз медленнее современных биполярных транзисторов и изначально считался худшим. Тем не менее, Канг указал на несколько преимуществ устройства, в частности, на простоту изготовления и его применение в интегральных схемах . [23]

Обычно в качестве полупроводника выбирают кремний . Некоторые производители микросхем, в частности IBM и Intel , используют сплав кремния и германия ( SiGe ) в каналах МОП-транзисторов. [ требуется ссылка ] Многие полупроводники с лучшими электрическими свойствами, чем кремний, такие как арсенид галлия , не образуют хороших интерфейсов полупроводник-изолятор и, таким образом, не подходят для МОП-транзисторов. Продолжаются исследования по созданию изоляторов с приемлемыми электрическими характеристиками на основе других полупроводниковых материалов.

Чтобы преодолеть увеличение энергопотребления из-за утечки тока затвора, вместо диоксида кремния для изолятора затвора используется диэлектрик с высоким κ , а поликремний заменяется металлическими затворами (например, Intel , 2009). [24]

Затвор отделен от канала тонким изолирующим слоем, традиционно из диоксида кремния, а позднее из оксинитрида кремния . Некоторые компании используют комбинацию диэлектрика с высоким κ и металлического затвора в узле 45 нм .

Когда напряжение подается между затвором и истоком, генерируемое электрическое поле проникает через оксид и создает инверсионный слой или канал на границе полупроводник-изолятор. Инверсионный слой обеспечивает канал, по которому ток может проходить между выводами истока и стока. Изменение напряжения между затвором и телом модулирует проводимость этого слоя и тем самым управляет током между стоком и истоком. Это известно как режим улучшения.

Традиционная структура металл-оксид-полупроводник (МОП) получается путем выращивания слоя диоксида кремния ( SiO

2) поверх кремниевой подложки, обычно путем термического окисления и осаждения слоя металла или поликристаллического кремния (последний обычно используется). Поскольку диоксид кремния является диэлектрическим материалом, его структура эквивалентна плоскому конденсатору , в котором один из электродов заменен полупроводником.

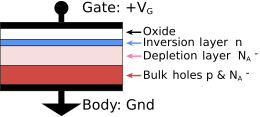

Когда напряжение прикладывается к структуре МОП, оно изменяет распределение зарядов в полупроводнике. Если мы рассмотрим полупроводник p-типа (с плотностью акцепторов N A , p плотностью дырок; p = N A в нейтральном объеме), положительное напряжение V G , от затвора к телу (см. рисунок), создает обедненный слой , вытесняя положительно заряженные дырки из интерфейса затвор-изолятор/полупроводник, оставляя открытой область без носителей неподвижных, отрицательно заряженных ионов акцептора (см. легирование ). Если V G достаточно велико, высокая концентрация отрицательных носителей заряда образуется в инверсионном слое , расположенном в тонком слое рядом с интерфейсом между полупроводником и изолятором.

Традиционно, напряжение затвора, при котором объемная плотность электронов в инверсионном слое такая же, как объемная плотность дырок в теле, называется пороговым напряжением . Когда напряжение между затвором и истоком транзистора ( V G ) превышает пороговое напряжение ( V th ), разница известна как напряжение перегрузки .

Эта структура с корпусом p-типа является основой МОП-транзистора n-типа, который требует добавления областей истока и стока n-типа.

Структура МОП-конденсатора является сердцем МОП-транзистора. Рассмотрим МОП-конденсатор, в котором кремниевая база имеет p-тип. Если на затвор подано положительное напряжение, дырки, находящиеся на поверхности подложки p-типа, будут отталкиваться электрическим полем, создаваемым приложенным напряжением. Сначала дырки будут просто отталкиваться, а то, что останется на поверхности, будет неподвижными (отрицательными) атомами акцепторного типа, что создает область обеднения на поверхности. Дырка создается атомом-акцептором, например, бором, у которого на один электрон меньше, чем у атома кремния. Дырки на самом деле не отталкиваются, будучи не-сущностями; электроны притягиваются положительным полем и заполняют эти дырки. Это создает область обеднения, в которой нет носителей заряда, поскольку электрон теперь закреплен на атоме и неподвижен.

По мере увеличения напряжения на затворе наступит момент, когда поверхность над обедненной областью преобразуется из p-типа в n-тип, поскольку электроны из основной области начнут притягиваться большим электрическим полем. Это известно как инверсия . Пороговое напряжение, при котором происходит это преобразование, является одним из важнейших параметров в МОП-транзисторе.

В случае MOSFET p-типа объемная инверсия происходит, когда собственный уровень энергии на поверхности становится меньше уровня Ферми на поверхности. Это можно увидеть на зонной диаграмме. Уровень Ферми определяет тип обсуждаемого полупроводника. Если уровень Ферми равен собственному уровню, полупроводник имеет собственный или чистый тип. Если уровень Ферми лежит ближе к зоне проводимости (валентной зоне), то тип полупроводника будет n-типа (p-типа).

Когда напряжение затвора увеличивается в положительном направлении (для данного примера), [ уточнить ] это сместит внутреннюю энергетическую зону так, что она будет изгибаться вниз к валентной зоне. Если уровень Ферми лежит ближе к валентной зоне (для p-типа), будет точка, когда внутренний уровень начнет пересекать уровень Ферми, и когда напряжение достигнет порогового напряжения, внутренний уровень действительно пересекает уровень Ферми, и это то, что известно как инверсия. В этой точке поверхность полупроводника инвертируется из p-типа в n-тип.

Если уровень Ферми лежит выше собственного уровня, то полупроводник имеет n-тип, поэтому при инверсии, когда собственный уровень достигает уровня Ферми (который находится ближе к валентной зоне) и пересекает его, тип полупроводника на поверхности изменяется в зависимости от относительного положения уровней Ферми и собственного уровня энергии.

MOSFET основан на модуляции концентрации заряда с помощью емкости MOS между электродом корпуса и электродом затвора , расположенным над корпусом и изолированным от всех других областей устройства слоем диэлектрика затвора. Если используются диэлектрики, отличные от оксида, устройство может называться металл-изолятор-полупроводник FET (MISFET). По сравнению с конденсатором MOS, MOSFET включает в себя два дополнительных вывода ( исток и сток ), каждый из которых подключен к отдельным высоколегированным областям, которые разделены областью корпуса. Эти области могут быть либо p-, либо n-типа, но они обе должны быть одного типа и противоположного типа по отношению к области корпуса. Исток и сток (в отличие от корпуса) высоколегированы, что обозначается знаком «+» после типа легирования.

Если MOSFET является n-канальным или nMOS FET, то исток и сток являются областями n+ , а тело — p -областью. Если MOSFET является p-канальным или pMOS FET, то исток и сток являются областями p+ , а тело — n- областью. Источник так назван, потому что он является источником носителей заряда (электронов для n-канала, дырок для p-канала), которые протекают через канал; аналогично, сток — это место, где носители заряда покидают канал.

Заполненность энергетических зон в полупроводнике определяется положением уровня Ферми относительно краев энергетических зон полупроводника.

При достаточном напряжении на затворе край валентной зоны перемещается далеко от уровня Ферми, а дырки из тела удаляются от затвора.

При еще большем смещении затвора, вблизи поверхности полупроводника край зоны проводимости приближается к уровню Ферми, заполняя поверхность электронами в инверсионном слое или n-канале на границе между p-областью и оксидом. Этот проводящий канал простирается между истоком и стоком, и ток проводится через него, когда между двумя электродами подается напряжение. Увеличение напряжения на затворе приводит к более высокой плотности электронов в инверсионном слое и, следовательно, увеличивает ток между истоком и стоком. При напряжениях затвора ниже порогового значения канал слабо заполнен, и между истоком и стоком может протекать только очень небольшой подпороговый ток утечки .

При приложении отрицательного напряжения затвор-исток (положительного напряжения исток-затвор) на поверхности n-области создается p-канал , аналогичный случаю n-канала, но с противоположными полярностями зарядов и напряжений. При приложении напряжения, менее отрицательного, чем пороговое значение (отрицательное напряжение для p-канала) между затвором и истоком, канал исчезает, и между истоком и стоком может протекать только очень небольшой подпороговый ток. Устройство может включать устройство кремний-на-изоляторе , в котором под тонким слоем полупроводника образован скрытый оксид. Если область канала между диэлектриком затвора и скрытой областью оксида очень тонкая, канал называется сверхтонкой областью канала с областями истока и стока, образованными по обе стороны в тонком слое полупроводника или над ним. Могут использоваться другие полупроводниковые материалы. Когда области истока и стока образованы над каналом полностью или частично, они называются приподнятыми областями источника/стока.

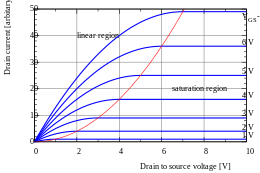

Работа MOSFET может быть разделена на три различных режима в зависимости от напряжений на клеммах. В следующем обсуждении используется упрощенная алгебраическая модель. [27] Современные характеристики MOSFET более сложны, чем представленная здесь алгебраическая модель. [28]

Для n-канального МОП-транзистора в режиме улучшения возможны три режима работы:

Когда V GS < V th :

где — смещение затвор-исток, — пороговое напряжение устройства.

Согласно базовой пороговой модели, транзистор выключен, и между стоком и истоком нет проводимости. Более точная модель учитывает влияние тепловой энергии на распределение Ферми-Дирака энергий электронов, что позволяет некоторым из более энергичных электронов в источнике войти в канал и течь к стоку. Это приводит к подпороговому току, который является экспоненциальной функцией напряжения затвор-исток. Хотя ток между стоком и истоком в идеале должен быть равен нулю, когда транзистор используется в качестве выключенного переключателя, существует слабый инверсионный ток, иногда называемый подпороговой утечкой.

При слабой инверсии, когда источник связан с объемом, ток изменяется экспоненциально, как приблизительно дается выражением: [29] [30]

где = ток при , тепловое напряжение и коэффициент наклона n определяются по формуле:

где = емкость обедненного слоя и = емкость оксидного слоя. Это уравнение обычно используется, но является лишь адекватным приближением для источника, связанного с объемом. Для источника, не связанного с объемом, подпороговое уравнение для тока стока в насыщении имеет вид [31] [32]

В длинноканальном устройстве зависимость тока от напряжения стока отсутствует , но по мере уменьшения длины канала снижение барьера, вызванное стоком, вводит зависимость напряжения стока, которая сложным образом зависит от геометрии устройства (например, легирования канала, легирования перехода и т. д.). Часто пороговое напряжение V th для этого режима определяется как напряжение затвора, при котором возникает выбранное значение тока I D0 , например, I D0 = 1 мкА, которое может не совпадать со значением V th, используемым в уравнениях для следующих режимов.

Некоторые микромощные аналоговые схемы разработаны с учетом преимуществ подпороговой проводимости. [33] [34] [35] Работая в области слабой инверсии, МОП-транзисторы в этих схемах обеспечивают максимально возможное отношение крутизны к току, а именно: , почти как у биполярного транзистора. [36]

Подпороговая кривая I–V экспоненциально зависит от порогового напряжения, что вносит сильную зависимость от любых производственных изменений, которые влияют на пороговое напряжение; например: изменения толщины оксида, глубины перехода или легирования тела, которые изменяют степень снижения барьера, вызванного стоком. Результирующая чувствительность к производственным изменениям усложняет оптимизацию утечки и производительности. [37] [38]

Когда V GS > V th и V DS < V GS − V th :

Транзистор включается, и создается канал, который пропускает ток между стоком и истоком. МОП-транзистор работает как резистор, управляемый напряжением затвора относительно как истока, так и стока. Ток от стока к истоку моделируется следующим образом:

где - эффективная подвижность носителей заряда, - ширина затвора, - длина затвора, - емкость оксида затвора на единицу площади. Переход от экспоненциальной подпороговой области к триодной области не такой резкий, как предполагают уравнения. [39] [40] [ требуется проверка ]

Когда V GS > V th и V DS ≥ (V GS – V th ):

Переключатель включается, и создается канал, который пропускает ток между стоком и истоком. Поскольку напряжение стока выше напряжения источника, электроны рассредоточиваются, и проводимость осуществляется не через узкий канал, а через более широкое, двух- или трехмерное распределение тока, простирающееся от интерфейса и глубже в подложке. Начало этой области также известно как отсечка, чтобы указать на отсутствие области канала вблизи стока. Хотя канал не простирается на всю длину устройства, электрическое поле между стоком и каналом очень велико, и проводимость продолжается. Ток стока теперь слабо зависит от напряжения стока и контролируется в основном напряжением затвор-исток и моделируется примерно так:

Дополнительный фактор, включающий λ, параметр модуляции длины канала, моделирует зависимость тока от напряжения стока из-за эффекта Эрли , или модуляции длины канала . Согласно этому уравнению, ключевым параметром проектирования является крутизна MOSFET:

где комбинация V ov = V GS − V th называется напряжением перегрузки [41] и где V DSsat = V GS − V th учитывает небольшой разрыв, который в противном случае появился бы при переходе между областями триода и насыщения.

Другим ключевым параметром конструкции является выходное сопротивление МОП-транзистора r out, определяемое по формуле:

.

r out — это обратная величина g DS , где I D — выражение в области насыщения.

Если λ принять равным нулю, то выходное сопротивление устройства будет бесконечным, что приведет к нереалистичным прогнозам схем, особенно в аналоговых схемах.

По мере того как длина канала становится очень короткой, эти уравнения становятся совершенно неточными. Возникают новые физические эффекты. Например, транспорт носителей в активном режиме может быть ограничен насыщением скорости . Когда доминирует насыщение скорости, ток стока насыщения более близок к линейному, чем квадратичному по V GS . При еще более коротких длинах носители перемещаются с близким к нулю рассеянием, известным как квазибаллистический транспорт . В баллистическом режиме носители перемещаются со скоростью инжекции, которая может превышать скорость насыщения и приближается к скорости Ферми при высокой плотности инверсионного заряда. Кроме того, снижение барьера, вызванное стоком, увеличивает ток выключенного состояния (отсечки) и требует увеличения порогового напряжения для компенсации, что, в свою очередь, уменьшает ток насыщения. [42] [43] [ требуется проверка ]

Занятость энергетических зон в полупроводнике задается положением уровня Ферми относительно краев энергетических зон полупроводника. Приложение обратного смещения источник-подложка pn-перехода источник-тело вносит расщепление между уровнями Ферми для электронов и дырок, перемещая уровень Ферми для канала дальше от края зоны, снижая занятость канала. Эффект заключается в увеличении напряжения затвора, необходимого для установления канала, как показано на рисунке. Это изменение силы канала путем приложения обратного смещения называется «эффектом тела».

На примере nMOS смещение затвор-корпус V GB располагает уровни энергии зоны проводимости, в то время как смещение источник-корпус V SB располагает уровень Ферми электронов вблизи интерфейса, определяя занятость этих уровней вблизи интерфейса и, следовательно, прочность инверсионного слоя или канала.

Воздействие тела на канал можно описать с помощью модификации порогового напряжения, аппроксимируемого следующим уравнением:

где V TB — пороговое напряжение при наличии смещения подложки, а V T0 — значение порогового напряжения при нулевом значении V SB , — параметр эффекта тела, а 2 φ B — приблизительное падение потенциала между поверхностью и объемом через обедненный слой, когда V SB = 0 и смещение затвора достаточно для обеспечения наличия канала. [44] Как показывает это уравнение, обратное смещение V SB > 0 приводит к увеличению порогового напряжения V TB и, следовательно, требует большего напряжения затвора, прежде чем канал заполнится.

Тело может работать как вторые ворота, и иногда его называют «задними воротами»; эффект тела иногда называют «эффектом задних ворот». [45]

Для MOSFET используются различные символы. Базовая конструкция обычно представляет собой линию для канала с истоком и стоком, выходящими из нее под прямым углом, а затем изгибающимися обратно под прямым углом в том же направлении, что и канал. Иногда три сегмента линии используются для режима обогащения и сплошная линия для режима истощения (см. режимы истощения и обогащения ). Другая линия рисуется параллельно каналу для затвора.

Соединение bulk или body , если показано, показано подключенным к задней части канала со стрелкой, указывающей pMOS или nMOS. Стрелки всегда указывают от P к N, поэтому NMOS (N-канал в P-well или P-подложке) имеет стрелку, указывающую внутрь (от bulk к каналу). Если bulk подключен к источнику (как это обычно бывает с дискретными устройствами), он иногда наклонен, чтобы встретиться с источником, выходящим из транзистора. Если bulk не показан (как это часто бывает в дизайне ИС, поскольку они, как правило, являются bulk), для обозначения PMOS иногда используется символ инверсии, в качестве альтернативы может использоваться стрелка на источнике так же, как для биполярных транзисторов (out для nMOS, in для pMOS).

Сравнение символов MOSFET в режиме обогащения и режиме обеднения, а также символов JFET . Ориентация символов (наиболее существенно положение источника относительно стока) такова, что более положительные напряжения появляются выше на странице, чем менее положительные напряжения, что подразумевает обычный ток, текущий «вниз» по странице: [46] [47] [48]

На схемах, где G, S, D не помечены, подробные характеристики символа указывают, какой вывод является источником, а какой стоком. Для символов MOSFET в режиме обогащения и режиме обеднения (во втором и пятом столбцах) вывод источника — это тот, который подключен к треугольнику. Кроме того, на этой схеме затвор показан в форме буквы «L», входная ножка которого ближе к S, чем к D, что также указывает, что есть что. Однако эти символы часто рисуются с затвором в форме буквы «T» (как и в других местах на этой странице), поэтому для указания вывода источника следует полагаться на треугольник.

Для символов, в которых показана основная или корпусная клемма, она здесь показана внутренне подключенной к источнику (т. е. черные треугольники на схемах в столбцах 2 и 5). Это типичная конфигурация, но ни в коем случае не единственная важная конфигурация. В общем, МОП-транзистор представляет собой четырехконтактное устройство, и в интегральных схемах многие МОП-транзисторы совместно используют корпусное соединение, не обязательно подключенное к истоковым клеммам всех транзисторов.

Цифровые интегральные схемы, такие как микропроцессоры и запоминающие устройства, содержат от тысяч до миллиардов интегрированных MOSFET-транзисторов на каждом устройстве, обеспечивая основные функции переключения, необходимые для реализации логических вентилей и хранения данных . Дискретные устройства широко используются в таких приложениях, как импульсные источники питания , частотно-регулируемые приводы и другие приложения силовой электроники , где каждое устройство может переключать тысячи ватт. Радиочастотные усилители вплоть до спектра УВЧ используют MOSFET-транзисторы в качестве аналоговых усилителей сигнала и мощности. Радиосистемы также используют MOSFET-транзисторы в качестве генераторов или смесителей для преобразования частот. Устройства MOSFET также применяются в усилителях мощности аудиочастот для систем оповещения, звукоусиления и домашних и автомобильных звуковых систем [ требуется ссылка ]

После разработки чистых комнат для снижения загрязнения до уровней, которые никогда ранее не считались необходимыми, а также фотолитографии [49] и планарного процесса , позволяющего производить схемы за очень мало шагов, система Si–SiO 2 обладала техническими преимуществами низкой стоимости производства (на основе схемы) и простоты интеграции. Во многом из-за этих двух факторов MOSFET стал наиболее широко используемым типом транзистора в Институте инженерии и технологий (IET). [ необходима цитата ]

Компания General Microelectronics представила первую коммерческую интегральную схему МОП в 1964 году. [50] Кроме того, метод соединения двух дополнительных МОП-транзисторов (P-канальных и N-канальных) в один высоко/низкоуровневый переключатель, известный как КМОП, означает, что цифровые схемы рассеивают очень мало энергии, за исключением моментов фактического переключения.

Самые ранние микропроцессоры, начиная с 1970 года, были все МОП-микропроцессоры ; т. е. полностью изготовленные из PMOS-логики или полностью изготовленные из NMOS-логики . В 1970-х годах МОП-микропроцессоры часто противопоставлялись КМОП-микропроцессорам и биполярным бит-слайс-процессорам . [51]

MOSFET используется в цифровой комплементарной логике металл-оксид-полупроводник ( CMOS ) [52] , которая использует p- и n-канальные MOSFET в качестве строительных блоков. Перегрев является серьезной проблемой в интегральных схемах , поскольку все больше транзисторов упаковываются во все меньшие чипы. Логика CMOS снижает энергопотребление, поскольку ток не течет (в идеале), и, таким образом, энергия не потребляется, за исключением случаев, когда переключаются входы логических вентилей . CMOS достигает этого снижения тока путем дополнения каждого nMOSFET pMOSFET и соединения обоих вентилей и обоих стоков вместе. Высокое напряжение на вентилях заставит nMOSFET проводить, а pMOSFET не проводить, а низкое напряжение на вентилях вызовет обратное. Во время переключения, когда напряжение переходит из одного состояния в другое, оба MOSFET будут кратковременно проводить. Такое расположение значительно снижает энергопотребление и выделение тепла.

Развитие цифровых технологий, таких как микропроцессоры, дало мотивацию для более быстрого развития технологии MOSFET, чем любого другого типа кремниевого транзистора. [53] Большим преимуществом MOSFET для цифровой коммутации является то, что оксидный слой между затвором и каналом предотвращает протекание постоянного тока через затвор, что еще больше снижает энергопотребление и обеспечивает очень большое входное сопротивление. Изолирующий оксид между затвором и каналом эффективно изолирует MOSFET на одном логическом этапе от более ранних и более поздних этапов, что позволяет одному выходу MOSFET управлять значительным количеством входов MOSFET. Биполярная транзисторная логика (такая как TTL ) не имеет такой высокой емкости разветвления. Эта изоляция также облегчает разработчикам возможность в некоторой степени игнорировать эффекты нагрузки между логическими этапами независимо. Эта степень определяется рабочей частотой: с увеличением частоты входное сопротивление MOSFET уменьшается.

Преимущества MOSFET в цифровых схемах не переходят в превосходство во всех аналоговых схемах . Два типа схем опираются на различные особенности поведения транзистора. Цифровые схемы переключаются, проводя большую часть времени либо полностью включенными, либо полностью выключенными. Переход от одной к другой имеет значение только в отношении скорости и требуемого заряда. Аналоговые схемы зависят от работы в переходной области, где небольшие изменения V gs могут модулировать выходной (сток) ток. JFET и биполярный транзистор (BJT) предпочтительны для точного согласования (соседних устройств в интегральных схемах), более высокой крутизны и определенных температурных характеристик, которые упрощают поддержание предсказуемой производительности при изменении температуры схемы.

Тем не менее, МОП-транзисторы широко используются во многих типах аналоговых схем из-за их собственных преимуществ (нулевой ток затвора, высокое и регулируемое выходное сопротивление и улучшенная надежность по сравнению с биполярными транзисторами, которые могут быть постоянно ухудшены даже легким разрушением эмиттер-базы). [ неопределенно ] Характеристики и производительность многих аналоговых схем можно масштабировать вверх или вниз, изменяя размеры (длину и ширину) используемых МОП-транзисторов. Для сравнения, в биполярных транзисторах действует другой закон масштабирования . Идеальные характеристики МОП-транзисторов относительно тока затвора (ноль) и напряжения смещения сток-исток (ноль) также делают их почти идеальными элементами переключения, а также делают аналоговые схемы с коммутируемыми конденсаторами практичными. В своей линейной области МОП-транзисторы могут использоваться в качестве прецизионных резисторов, которые могут иметь гораздо более высокое контролируемое сопротивление, чем БОП-транзисторы. В цепях высокой мощности МОП-транзисторы иногда имеют преимущество в том, что не страдают от теплового разгона , как это происходит с БОП-транзисторами. [ сомнительно – обсудить ] Это означает, что полные аналоговые схемы могут быть сделаны на кремниевом чипе в гораздо меньшем пространстве и с более простыми методами изготовления. МОП-транзисторы идеально подходят для переключения индуктивных нагрузок из-за устойчивости к индуктивной отдаче .

Некоторые ИС объединяют аналоговые и цифровые схемы MOSFET на одной интегральной схеме смешанного сигнала , что делает необходимое пространство на плате еще меньше. Это создает необходимость изолировать аналоговые схемы от цифровых схем на уровне чипа, что приводит к использованию изолирующих колец и кремния на изоляторе (SOI). Поскольку MOSFET требуют больше места для обработки заданного количества мощности, чем BJT, процессы изготовления могут включать BJT и MOSFET в одно устройство. Устройства со смешанными транзисторами называются bi-FET (биполярные FET), если они содержат только один BJT-FET, и BiCMOS (биполярные CMOS), если они содержат комплементарные BJT-FET. Такие устройства обладают преимуществами как изолированных затворов, так и более высокой плотности тока.

Аналоговые переключатели MOSFET используют MOSFET для передачи аналоговых сигналов во включенном состоянии и в качестве высокого импеданса в выключенном состоянии. Сигналы проходят в обоих направлениях через переключатель MOSFET. В этом приложении сток и исток MOSFET меняются местами в зависимости от относительного напряжения электродов истока и стока. Исток является более отрицательной стороной для N-MOS или более положительной стороной для P-MOS. Все эти переключатели ограничены в том, какие сигналы они могут пропускать или останавливать, их напряжениями затвор-исток, затвор-сток и исток-сток; превышение пределов напряжения, тока или мощности может привести к повреждению переключателя.

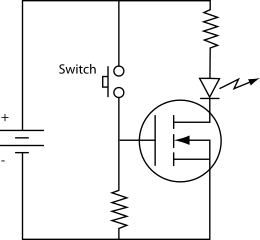

В этом аналоговом переключателе используется простой четырехконтактный МОП-транзистор P- или N-типа.

В случае переключателя n-типа корпус подключен к самому отрицательному источнику питания (обычно GND), а затвор используется для управления переключателем. Всякий раз, когда напряжение затвора превышает напряжение источника по крайней мере на пороговое напряжение, MOSFET проводит. Чем выше напряжение, тем больше MOSFET может проводить. Переключатель N-MOS пропускает все напряжения, меньшие, чем V gate − V tn . Когда переключатель проводит, он обычно работает в линейном (или омическом) режиме работы, поскольку напряжения источника и стока обычно будут почти равны.

В случае P-MOS корпус подключается к самому положительному напряжению, а затвор приводится к более низкому потенциалу для включения переключателя. Переключатель P-MOS пропускает все напряжения выше V gate − V tp (пороговое напряжение V tp отрицательно в случае P-MOS в режиме улучшения).

Этот «комплементарный» или КМОП-тип переключателя использует один P-MOS и один N-MOS FET для противодействия ограничениям однотипного переключателя. У FET стоки и истоки соединены параллельно, корпус P-MOS подключен к высокому потенциалу ( V DD ), а корпус N-MOS подключен к низкому потенциалу ( gnd ). Чтобы включить переключатель, затвор P-MOS приводится в состояние низкого потенциала, а затвор N-MOS — в состояние высокого потенциала. При напряжениях между V DD − V tn и gnd − V tp оба FET проводят сигнал; при напряжениях меньше gnd − V tp N-MOS проводит сигнал один; а при напряжениях больше V DD − V tn P-MOS проводит сигнал один.

Пределы напряжения для этого переключателя — это пределы напряжения затвор-исток, затвор-сток и исток-сток для обоих FET. Кроме того, P-MOS обычно в два-три раза шире, чем N-MOS, поэтому переключатель будет сбалансирован по скорости в двух направлениях.

Трехпозиционная схема иногда включает в себя КМОП-переключатель MOSFET на выходе, чтобы обеспечить низкоомный выходной сигнал полного диапазона во включенном состоянии и высокоомный сигнал среднего уровня в выключенном состоянии.

Основным критерием для материала затвора является то, что он является хорошим проводником . Высоколегированный поликристаллический кремний является приемлемым, но, безусловно, не идеальным проводником, а также страдает от некоторых дополнительных технических недостатков в своей роли стандартного материала затвора. Тем не менее, есть несколько причин в пользу использования поликремния:

Хотя поликремниевые затворы были фактическим стандартом в течение последних двадцати лет, у них есть некоторые недостатки, которые привели к их вероятной будущей замене металлическими затворами. К этим недостаткам относятся:

Современные высокопроизводительные процессоры используют технологию металлических затворов вместе с диэлектриками high-κ , комбинацию, известную как high-κ, metal gate (HKMG). Недостатки металлических затворов преодолеваются несколькими методами: [54]

По мере уменьшения размеров устройств изолирующие слои становятся тоньше, часто с помощью этапов термического окисления или локального окисления кремния ( LOCOS ). Для наномасштабных устройств в какой-то момент происходит туннелирование носителей через изолятор из канала в затворный электрод. Чтобы уменьшить результирующий ток утечки , изолятор можно сделать тоньше, выбрав материал с более высокой диэлектрической проницаемостью. Чтобы увидеть, как связаны толщина и диэлектрическая проницаемость, обратите внимание, что закон Гаусса связывает поле с зарядом следующим образом:

где Q = плотность заряда, κ = диэлектрическая постоянная, ε 0 = диэлектрическая проницаемость пустого пространства и E = электрическое поле. Из этого закона следует, что тот же заряд может поддерживаться в канале при более низком поле при условии увеличения κ. Напряжение на затворе определяется по формуле:

где V G = напряжение затвора, V ch = напряжение на стороне канала изолятора, а t ins = толщина изолятора. Это уравнение показывает, что напряжение затвора не увеличится при увеличении толщины изолятора, при условии, что κ увеличится, чтобы сохранить t ins / κ = постоянным (более подробную информацию см. в статье о диэлектриках с высоким κ и в разделе этой статьи об утечке затвор-оксид).

Изолятор в МОП-транзисторе — это диэлектрик, который в любом случае может быть оксидом кремния, образованным LOCOS , но используются и многие другие диэлектрические материалы. Общим термином для диэлектрика является затворный диэлектрик, поскольку диэлектрик находится непосредственно под затворным электродом и над каналом МОП-транзистора.

Переходы исток-корпус и сток-корпус являются объектом большого внимания из-за трех основных факторов: их конструкция влияет на вольт-амперные характеристики ( ВАХ ) устройства, снижая выходное сопротивление, а также на быстродействие устройства через эффект нагрузки емкостей перехода и , наконец, на компонент рассеиваемой мощности в режиме ожидания из-за утечки перехода.

Снижение порогового напряжения, вызванное стоком, и эффекты модуляции длины канала на кривых IV уменьшаются за счет использования неглубоких расширений переходов. Кроме того, может использоваться легирование гало , то есть добавление очень тонких сильно легированных областей того же типа легирования, что и тело, плотно прилегающих к стенкам переходов, чтобы ограничить протяженность областей обеднения . [55]

Емкостные эффекты ограничиваются использованием приподнятых геометрий истока и стока, благодаря которым большая часть контактной области граничит с толстым диэлектриком вместо кремния. [56]

Эти различные особенности конструкции перекрестка показаны (с художественной долей ) на рисунке.

За последние десятилетия MOSFET (используемый для цифровой логики) постоянно уменьшался в размерах; типичная длина канала MOSFET когда-то составляла несколько микрометров , но современные интегральные схемы включают MOSFET с длиной канала в десятки нанометров. Работа Роберта Деннарда по теории масштабирования сыграла решающую роль в признании того, что это постоянное сокращение возможно. Intel начала производство процесса с размером элемента 32 нм (с каналом еще короче) в конце 2009 года. Полупроводниковая промышленность поддерживает «дорожную карту», ITRS , [57], которая задает темп для разработки MOSFET. Исторически трудности с уменьшением размера MOSFET были связаны с процессом изготовления полупроводниковых устройств, необходимостью использования очень низких напряжений и с худшими электрическими характеристиками, требующими перепроектирования схемы и инноваций (маленькие MOSFET демонстрируют более высокие токи утечки и более низкое выходное сопротивление).

МОП-транзисторы меньшего размера желательны по нескольким причинам. Основная причина уменьшения размеров транзисторов — это размещение большего количества устройств на заданной площади чипа. Это приводит к получению чипа с той же функциональностью на меньшей площади или чипов с большей функциональностью на той же площади. Поскольку затраты на изготовление полупроводниковой пластины относительно фиксированы, стоимость интегральных схем в основном связана с количеством чипов, которые можно произвести на одной пластине. Следовательно, меньшие ИС позволяют производить больше чипов на пластине, что снижает цену на чип. Фактически, за последние 30 лет количество транзисторов на чип удваивалось каждые 2–3 года после внедрения нового технологического узла. Например, количество МОП-транзисторов в микропроцессоре, изготовленном по технологии 45 нм , вполне может быть вдвое больше, чем в чипе 65 нм . Это удвоение плотности транзисторов впервые наблюдал Гордон Мур в 1965 году и обычно называется законом Мура . [58] Также ожидается, что меньшие транзисторы переключаются быстрее. Например, одним из подходов к уменьшению размера является масштабирование MOSFET, которое требует пропорционального уменьшения всех размеров устройства. Основными размерами устройства являются длина канала, ширина канала и толщина оксида. При уменьшении их в равных количествах сопротивление канала транзистора не изменяется, в то время как емкость затвора уменьшается в этом же количестве. Следовательно, задержка RC транзистора масштабируется с аналогичным коэффициентом. Хотя это традиционно имело место для старых технологий, для современных MOSFET уменьшение размеров транзистора не обязательно приводит к более высокой скорости чипа, поскольку задержка из-за межсоединений более значительна.

Производство МОП-транзисторов с длиной канала намного меньше микрометра является сложной задачей, а трудности изготовления полупроводниковых приборов всегда являются ограничивающим фактором в развитии технологии интегральных схем. Хотя такие процессы, как ALD, улучшили производство небольших компонентов, малый размер МОП-транзистора (менее нескольких десятков нанометров) создал эксплуатационные проблемы:

По мере уменьшения геометрии МОП-транзистора напряжение, которое может быть приложено к затвору, должно быть уменьшено для поддержания надежности. Для поддержания производительности пороговое напряжение МОП-транзистора также должно быть уменьшено. По мере уменьшения порогового напряжения транзистор не может быть переключен из состояния полного выключения в состояние полного включения с ограниченным размахом доступного напряжения; конструкция схемы представляет собой компромисс между сильным током в состоянии включения и слабым током в состоянии выключения , и приложение определяет, следует ли отдать предпочтение одному из них. Подпороговая утечка (включая подпороговую проводимость, утечку затвор-оксид и утечку обратного смещения), которая игнорировалась в прошлом, теперь может потреблять более половины общей потребляемой мощности современных высокопроизводительных чипов СБИС. [59] [60]

Оксид затвора, который служит изолятором между затвором и каналом, должен быть сделан как можно тоньше, чтобы увеличить проводимость канала и производительность, когда транзистор включен, и уменьшить подпороговую утечку, когда транзистор выключен. Однако с оксидами затвора тока толщиной около 1,2 нм (что в кремнии составляет ~5 атомов ) квантово-механическое явление туннелирования электронов происходит между затвором и каналом, что приводит к увеличению энергопотребления. Диоксид кремния традиционно использовался в качестве изолятора затвора. Однако диоксид кремния имеет скромную диэлектрическую проницаемость. Увеличение диэлектрической проницаемости диэлектрика затвора позволяет получить более толстый слой, сохраняя при этом высокую емкость (емкость пропорциональна диэлектрической проницаемости и обратно пропорциональна толщине диэлектрика). При прочих равных условиях большая толщина диэлектрика уменьшает квантовый туннельный ток через диэлектрик между затвором и каналом.

Изоляторы, которые имеют большую диэлектрическую постоянную , чем диоксид кремния (называемые диэлектриками с высоким значением κ ), такие как силикаты металлов группы IVb, например, силикаты и оксиды гафния и циркония , используются для уменьшения утечки затвора, начиная с 45-нанометрового технологического узла. С другой стороны, высота барьера нового изолятора затвора является важным фактором; разница в энергии зоны проводимости между полупроводником и диэлектриком (и соответствующая разница в энергии валентной зоны ) также влияет на уровень тока утечки. Для традиционного оксида затвора, диоксида кремния, первый барьер составляет приблизительно 8 эВ . Для многих альтернативных диэлектриков это значение значительно ниже, что имеет тенденцию к увеличению туннельного тока, что несколько сводит на нет преимущество более высокой диэлектрической постоянной. Максимальное напряжение затвор-исток определяется силой электрического поля, которое может поддерживаться диэлектриком затвора до того, как произойдет значительная утечка. По мере того, как изолирующий диэлектрик становится тоньше, напряженность электрического поля внутри него увеличивается для фиксированного напряжения. Это требует использования более низких напряжений с более тонким диэлектриком.

Чтобы сделать устройства меньше, конструкция переходов стала более сложной, что привело к более высоким уровням легирования , более мелким переходам, легированию «гало» и т. д. [61] [62] все для уменьшения снижения барьера, вызванного стоком (см. раздел о конструкции переходов). Чтобы сохранить эти сложные переходы на месте, этапы отжига, ранее использовавшиеся для удаления повреждений и электрически активных дефектов, должны быть сокращены [63], что увеличивает утечку переходов. Более сильное легирование также связано с более тонкими обедненными слоями и большим количеством центров рекомбинации, что приводит к увеличению тока утечки, даже без повреждения решетки.

Снижение барьера, вызванное стоком (DIBL), и спад V T : Из-за эффекта короткого канала формирование канала не полностью выполняется затвором, но теперь сток и исток также влияют на формирование канала. По мере уменьшения длины канала области истощения истока и стока сближаются и делают пороговое напряжение ( V T ) функцией длины канала. Это называется спадом V T. V T также становится функцией напряжения сток-исток V DS . По мере увеличения V DS области истощения увеличиваются в размерах, и значительное количество заряда истощается V DS . Затем напряжение затвора, необходимое для формирования канала, понижается, и, таким образом, V T уменьшается с увеличением V DS . Этот эффект называется снижением барьера, вызванным стоком (DIBL).

Для аналоговой работы хороший коэффициент усиления требует высокого выходного импеданса MOSFET, то есть ток MOSFET должен лишь незначительно меняться в зависимости от приложенного напряжения сток-исток. По мере уменьшения размеров устройств влияние стока все более успешно конкурирует с влиянием затвора из-за растущей близости этих двух электродов, что увеличивает чувствительность тока MOSFET к напряжению стока. Чтобы противодействовать результирующему снижению выходного сопротивления, схемы усложняются либо за счет использования большего количества устройств, например, каскодных и каскадных усилителей , либо за счет использования схем обратной связи с использованием операционных усилителей , например, схемы, подобной той, что представлена на соседнем рисунке.

Транскондуктивность МОП- транзистора определяет его усиление и пропорциональна подвижности дырок или электронов (в зависимости от типа устройства), по крайней мере, для низких напряжений стока. По мере уменьшения размера МОП-транзистора поля в канале увеличиваются, а уровни легирующих примесей увеличиваются. Оба изменения уменьшают подвижность носителей и, следовательно, транскондуктивность. Поскольку длина канала уменьшается без пропорционального уменьшения напряжения стока, что увеличивает электрическое поле в канале, результатом является насыщение скорости носителей, что ограничивает ток и транскондуктивность.

Традиционно время переключения было примерно пропорционально емкости затвора затворов. Однако, с уменьшением размеров транзисторов и размещением большего количества транзисторов на чипе, емкость межсоединений (емкость соединений металлического слоя между различными частями чипа) становится большим процентом емкости. [64] [65] Сигналы должны проходить через межсоединения, что приводит к увеличению задержки и снижению производительности.

Постоянно растущая плотность МОП-транзисторов на интегральной схеме создает проблемы существенного локального выделения тепла, которое может ухудшить работу схемы. Схемы работают медленнее при высоких температурах, имеют пониженную надежность и более короткий срок службы. Радиаторы и другие охлаждающие устройства и методы теперь требуются для многих интегральных схем, включая микропроцессоры. Силовые МОП-транзисторы подвержены риску теплового разгона . Поскольку их сопротивление в открытом состоянии увеличивается с температурой, если нагрузка приблизительно равна нагрузке постоянного тока, то потери мощности соответственно увеличиваются, генерируя дополнительное тепло. Когда радиатор не может поддерживать температуру достаточно низкой, температура перехода может быстро и неконтролируемо расти, что приведет к разрушению устройства.

С уменьшением размеров МОП-транзисторов уменьшается и количество атомов в кремнии, которые определяют многие свойства транзистора, в результате чего контроль количества легирующих примесей и их размещения становится более нестабильным. Во время производства чипов случайные изменения процесса влияют на все размеры транзистора: длину, ширину, глубину перехода, толщину оксида и т. д ., и становятся все большим процентом от общего размера транзистора по мере уменьшения размера транзистора. Характеристики транзистора становятся менее определенными, более статистическими. Случайный характер производства означает, что мы не знаем, какой конкретный пример МОП-транзистора фактически окажется в конкретном экземпляре схемы. Эта неопределенность вынуждает использовать менее оптимальную конструкцию, поскольку конструкция должна работать для большого разнообразия возможных компонентных МОП-транзисторов. См. изменение процесса , проектирование для технологичности , проектирование надежности и статистическое управление процессом . [66]

Современные ИС моделируются на компьютере с целью получения рабочих схем из первой изготовленной партии. По мере миниатюризации устройств сложность обработки затрудняет точное предсказание того, как будут выглядеть конечные устройства, а моделирование физических процессов также становится более сложным. Кроме того, микроскопические изменения в структуре, обусловленные просто вероятностной природой атомных процессов, требуют статистических (а не только детерминированных) прогнозов. Сочетание этих факторов затрудняет адекватное моделирование и производство «с первого раза».

Двухзатворный МОП-транзистор имеет конфигурацию тетрода , где оба затвора управляют током в устройстве. Он обычно используется для малосигнальных устройств в радиочастотных приложениях, где смещение затвора на стороне стока при постоянном потенциале снижает потери усиления, вызванные эффектом Миллера , заменяя два отдельных транзистора в каскодной конфигурации. Другие распространенные применения в радиочастотных схемах включают управление усилением и смешивание (преобразование частоты). Описание тетрода , хотя и точное, не копирует тетрод вакуумной лампы. Тетроды вакуумной лампы, использующие сетку экрана, демонстрируют гораздо более низкую емкость сетка-пластина и гораздо более высокое выходное сопротивление и усиление напряжения, чем триодные вакуумные лампы. Эти улучшения обычно составляют порядок величины (в 10 раз) или значительно больше. Транзисторы тетрода (будь то биполярные переходы или полевые) не демонстрируют улучшений такой большой степени.

FinFET — это двухзатворный кремний-на-изоляторе прибор, одна из многих геометрий, введенных для смягчения эффектов коротких каналов и снижения снижения барьера, вызванного стоком. Ребро относится к узкому каналу между истоком и стоком. Тонкий изолирующий оксидный слой по обе стороны ребра отделяет его от затвора. SOI FinFET с толстым оксидом наверху ребра называются двухзатворными , а те, у которых сверху и по бокам тонкий оксид, называются трехзатворными FinFET. [67] [68]

Существуют устройства MOSFET в режиме истощения , которые используются реже, чем стандартные устройства в режиме обогащения, которые уже описаны. Это устройства MOSFET, которые легированы таким образом, что канал существует даже при нулевом напряжении от затвора до источника. Для управления каналом на затвор подается отрицательное напряжение (для устройства с n-каналом), истощая канал, что уменьшает ток, протекающий через устройство. По сути, устройство в режиме истощения эквивалентно нормально замкнутому (включенному) переключателю, в то время как устройство в режиме обогащения эквивалентно нормально разомкнутому (выключенному) переключателю. [69]

Благодаря низкому коэффициенту шума в радиочастотном диапазоне и лучшему коэффициенту усиления эти устройства часто предпочитают биполярным транзисторам в радиочастотных входных каскадах, например, в телевизорах .

Семейства МОП-транзисторов, работающих в режиме обеднения, включают BF960 от Siemens и Telefunken , а также BF980, выпущенный в 1980-х годах Philips (позже ставший NXP Semiconductors ), чьи производные до сих пор используются в схемах АРУ и ВЧ- смесителей .

Полевой транзистор с металлическим изолятором и полупроводником [70] [71] [72] или MISFET — более общий термин, чем MOSFET , и синоним полевого транзистора с изолированным затвором (IGFET). Все MOSFET являются MISFET, но не все MISFET являются MOSFET.

Диэлектрик затвора в МДП-транзисторе — это оксид подложки (отсюда обычно диоксид кремния ) в МДП-транзисторе, но могут использоваться и другие материалы. Диэлектрик затвора находится непосредственно под электродом затвора и над каналом МДП-транзистора. Термин « металл» исторически используется для обозначения материала затвора, хотя сейчас это обычно высоколегированный поликремний или какой-либо другой неметалл .

Типы изоляторов могут быть:

Для устройств с одинаковой способностью управления током n-канальные МОП-транзисторы могут быть сделаны меньше, чем p-канальные МОП-транзисторы, из-за того, что носители заряда p-канала ( дырки ) имеют меньшую подвижность , чем носители заряда n-канала ( электроны ), и производство только одного типа МОП-транзистора на кремниевой подложке дешевле и технически проще. Это были движущие принципы при проектировании логики NMOS , которая использует исключительно n-канальные МОП-транзисторы. Однако, пренебрегая током утечки , в отличие от КМОП-логики, NMOS-логика потребляет энергию, даже когда не происходит переключения. С развитием технологий КМОП-логика вытеснила NMOS-логику в середине 1980-х годов, став предпочтительным процессом для цифровых микросхем.

Силовые МОП-транзисторы имеют другую структуру. [74] Как и большинство силовых устройств, структура вертикальная, а не планарная. Используя вертикальную структуру, транзистор может выдерживать как высокое блокирующее напряжение, так и высокий ток. Номинальное напряжение транзистора является функцией легирования и толщины N- эпитаксиального слоя (см. поперечное сечение), в то время как номинальный ток является функцией ширины канала (чем шире канал, тем выше ток). В планарной структуре номинальные значения тока и пробивного напряжения являются функцией размеров канала (соответственно ширины и длины канала), что приводит к неэффективному использованию «кремниевого имущества». При вертикальной структуре площадь компонента примерно пропорциональна току, который он может выдержать, а толщина компонента (фактически толщина N-эпитаксиального слоя) пропорциональна пробивному напряжению. [75]

Мощные МОП-транзисторы с боковой структурой в основном используются в высококачественных аудиоусилителях и мощных PA-системах. Их преимущество заключается в лучшем поведении в области насыщения (соответствующей линейной области биполярного транзистора), чем у вертикальных МОП-транзисторов. Вертикальные МОП-транзисторы предназначены для коммутационных приложений. [76]

Существуют LDMOS (боковой двойной диффузионный металл-оксид-полупроводник) и VDMOS (вертикальный двойной диффузионный металл-оксид-полупроводник). Большинство мощных МОП-транзисторов изготавливаются с использованием этой технологии.

Полупроводниковые субмикрометровые и нанометровые электронные схемы являются основной проблемой для работы в пределах нормального допуска в жестких радиационных условиях, таких как открытый космос . Одним из подходов к проектированию для создания радиационно-стойкого по конструкции (RHBD) устройства является транзистор с закрытой компоновкой (ELT). Обычно затвор MOSFET окружает сток, который размещается в центре ELT. Исток MOSFET окружает затвор. Другой RHBD MOSFET называется H-Gate. Оба этих транзистора имеют очень низкие токи утечки по отношению к радиации. Однако они имеют большие размеры и занимают больше места на кремнии, чем стандартный MOSFET. В старых конструкциях STI (мелкоканальная изоляция) удары излучения вблизи области оксида кремния вызывают инверсию канала в углах стандартного MOSFET из-за накопления захваченных зарядов, вызванных радиацией. Если заряды достаточно велики, накопленные заряды влияют на края поверхности STI вдоль канала вблизи интерфейса канала (затвора) стандартного MOSFET. Это приводит к инверсии канала устройства вдоль краев канала, создавая путь утечки в выключенном состоянии. Впоследствии устройство включается; этот процесс серьезно снижает надежность схем. ELT предлагает много преимуществ, включая повышение надежности за счет снижения нежелательной инверсии поверхности на краях затвора, которая происходит в стандартном MOSFET. Поскольку края затвора заключены в ELT, нет края оксида затвора (STI на интерфейсе затвора), и, таким образом, утечка транзистора в выключенном состоянии значительно снижается. Маломощные микроэлектронные схемы, включая компьютеры, устройства связи и системы мониторинга в космических челноках и спутниках, сильно отличаются от тех, что используются на Земле. Это схемы, устойчивые к радиации (высокоскоростные атомные частицы, такие как протоны и нейтроны , рассеяние магнитной энергии солнечных вспышек в околоземном пространстве, энергичные космические лучи, такие как рентгеновские , гамма-лучи и т. д.). Эта специальная электроника разработана с применением различных методов с использованием RHBD MOSFET для обеспечения безопасных космических путешествий и безопасных выходов астронавтов в открытый космос.